-

像素探测器[1]是当前最先进的位置灵敏探测器之一,在加速器物理实验的内径迹探测系统[2]、X光成像[3]等领域都有着广泛的应用。像素探测器由于通道密度高,给读出电子学的设计带来很大的挑战,其信号读出采用ASIC(Application Specific Integrated Circuit) 芯片实现。典型的ASIC芯片,如Timepix系列芯片[4-5]、Medipix系列芯片[6-7]、Topmetal系列芯片[8]均在相应的领域有着重要的应用。

像素阵列读出芯片通常由一个个单像素电子学组成的阵列及其控制逻辑组成,通常具有像素数目多、单像素面积小的特点。例如,Topmetal-Ⅰ芯片单个像素尺寸为80 μm×80 μm,像素阵列大小为64行×64列;Medipix-Ⅱ芯片单个像素尺寸为55 μm×55 μm,像素阵列大小为256行×256列;Timepix系列芯片单个像素尺寸为55 μm×55 μm,像素阵列大小为256行×256列。通过像素阵列的每一个击中信号的信息都会被记录下来,通常因为应用场景的不同而设计为在不同的模式下工作具备不同的功能。值得注意的是,Timepix3芯片[5]可以在三种模式下工作:光子计数模式、TOA(Time-over-Arrival)[9-11]和TOT(Time-over-Threshold) [12-13],同时具备位置分辨、时间测量及能量测量的能力,其中bin size可以达到1.56 ns。随着物理实验和其他应用场景的发展,对时间测量的精度提出了更高的要求,需要设计性能更加优越的TDC(Time-to-Digital Conversion) ASIC来满足需求。

预期未来像素阵列设计的规模为100行×100列,本文设计的TDC负责单列信号的时间信息测量,即未来需要100通道TDC集成到像素阵列的末端,本设计为验证TDC性能,设计为两通道。考虑到一列100个像素点可能存在多个像素点被击中的情况,因此预期一列像素的输出信号具备以下特点:输出信号为连续脉冲信号,相邻脉冲信号时间间隔最短为500 ps,脉冲宽度最短为200 ps,连续的脉冲信号最多包含十个连续脉冲。要求测量每个脉冲的前沿和后沿的到达时间,bin size达到10 ps,精度好于10 ps RMS。

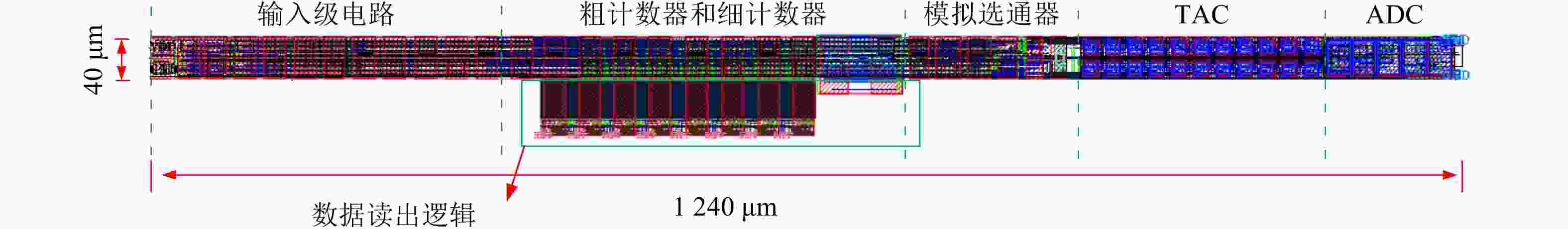

设计的难点在于如何在有限的40 μm宽度(单个像素预期尺寸为40 μm×40 μm)范围内处理高速的多事例信号,并同时获得高的时间测量精度。将指标需求总结为表1。

表 1 单通道TDC的指标需求

指标 TDC 精度 优于10 ps RMS bin size 优于10 ps 速度 2 GHz(最多处理10个信号) -

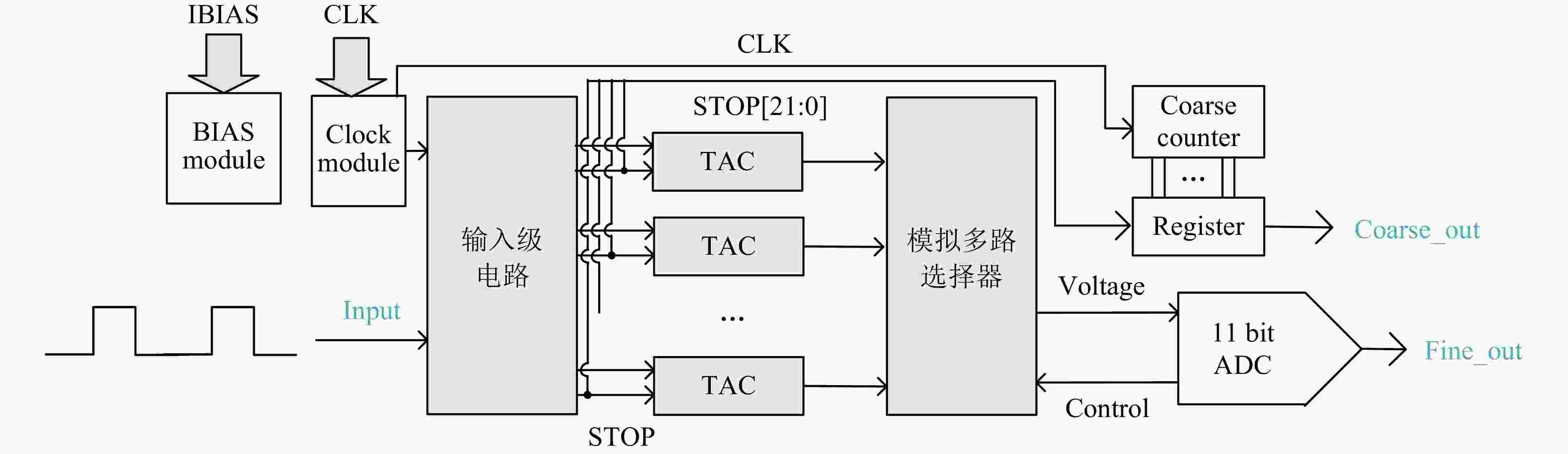

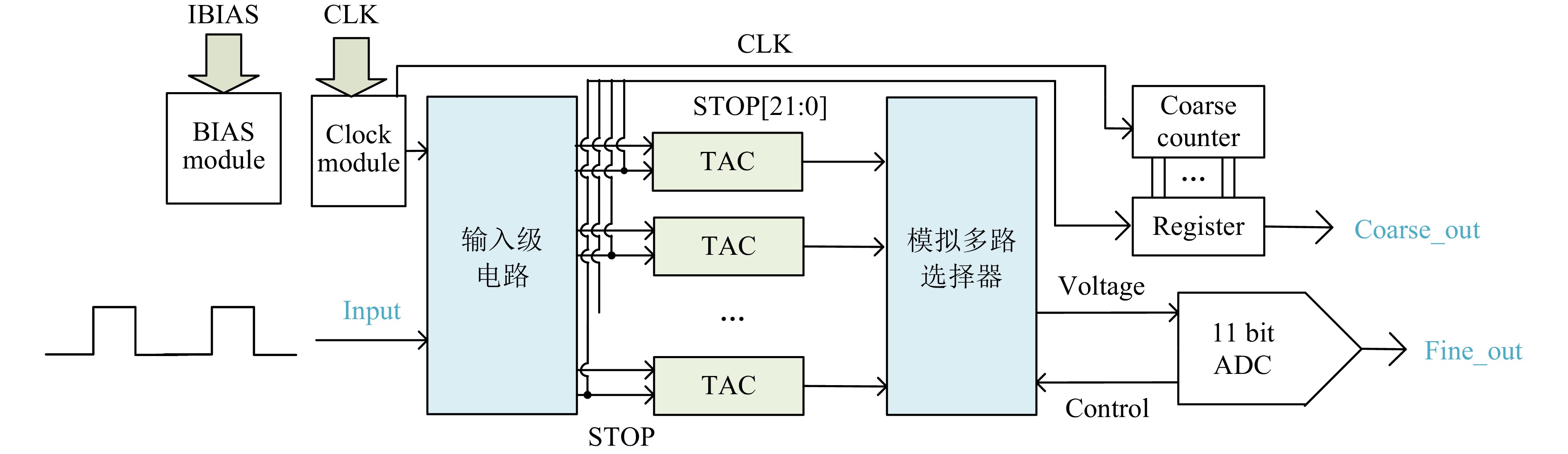

根据应用需求设计完成TDC AISC,具体结构如图1所示。

TDC由输入级电路、时间幅度变换电路、模拟选通器、粗计数模块、寄存器组和一个ADC组成。考虑到输入信号速度较快,因此首先设计输入级电路处理输入信号,使得连续过来的脉冲信号被依次送到11个不同的通道中(11个是因为预留一个通道做标定),使得连续处理11个脉冲信号变得可行。以某一个通道为例,脉冲信号继续在输入级中处理得到两组信号,一组记录了上升沿的时间信息,产生一个START和STOP信号,另一组记录了下降沿的时间信息,同样产生一个START和STOP信号。因此总共产生22组START和STOP信号,STOP信号送到各自的寄存器组锁下粗计数模块的数值,作为各自的粗计数时间戳。细计数由START和STOP信号继续处理得到,有许多方案可以选取:Vernier Delay Lines[14]、Delay Looped Lines[15]等等。上述方案都属于数字信号处理的方案,因为22组信号都需要一个高精度TDC,这对面积提出了很高的要求,因此选用结构简单的TAC(Time-to-Amplitude Converter)+ADC(Time-to-Amplitude Converter)方案,22 个TAC共用一个ADC。每一组START和STOP信号输入到各自的TAC中得到正比于START和STOP时间差的电压信号。希望通过共用ADC简化电路,需要额外设计一个模拟多路选择器来逐个量化得到电压信号。ADC的输出和粗计数共同构成对应上升沿或者下降沿的时间戳。

-

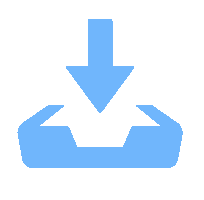

输入级电路的整体结构如图2所示。原理图中的触发器组为Input信号作为时钟驱动的移位寄存器组,产生选通信号控制传输门的打开与关断。同时,传输门的输入端为输入信号经延时产生的信号Signal_delay,调整合适的延时使得脉冲被选通到不同的通路中,经过buffer后得到信号S1~S11,送到同步模块中继续处理。图3给出同步模块的原理图,其主要作用是产生后续TAC需要的START和STOP信号,因为下降沿也需要定时,则产生了两组启停信号。

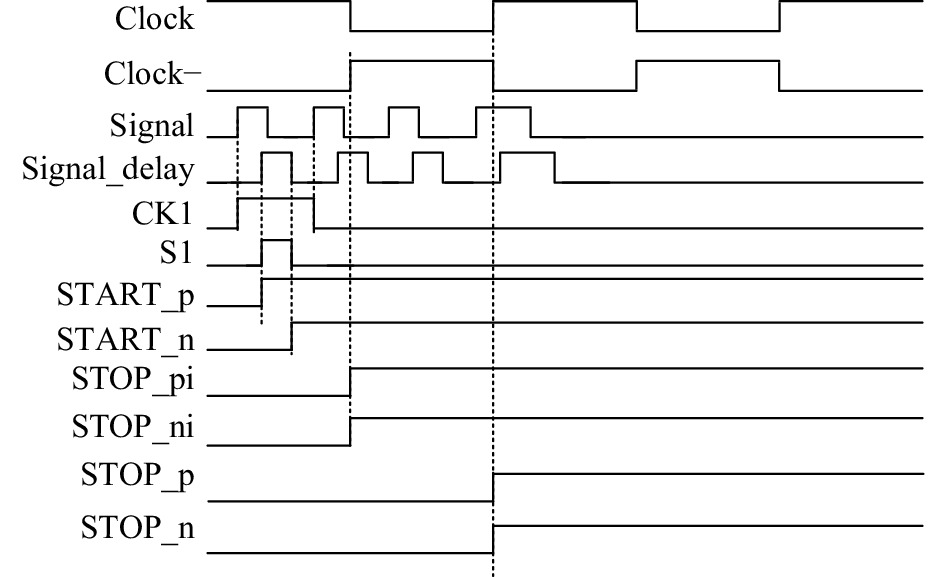

整体电路为数字电路,电路的搭建没有走数字标准流程,因此需要注意时序的完整性。图4给出关键节点的波形,其对应线名在图2和图3中都有对应名称。需要注意的是,为了降低亚稳态发生的概率,在同步逻辑电路模块中采用两级锁存的方式将START_p和START_n信号同步到Clock时钟域,Clock时钟周期为2 ns [16]。但是这里采用的两级锁存中,第一级触发器的时钟为Clock的反向时钟Clock-,第二级触发器的时钟为Clock,采用这样的方法得到的START和STOP信号的时间差为1~3 ns,采用同向时钟驱动的两级触发器得到的启停信号的时间差为2~4 ns。因为使用的130 nm工艺的电源电压为1.2 V,充电时长的增加会恶化TAC的非线性,因此采用Clock−驱动第一级触发器,Clock驱动第二个触发器的方法为接下来的TAC电路的处理带来便捷。停止信号即STOP信号同时会送到粗计数模块中,粗计数模块是由Clock驱动的8位粗计数器,因为STOP已经同步到Clock时钟域,因此在锁存粗计数的过程中没有亚稳态的问题。

-

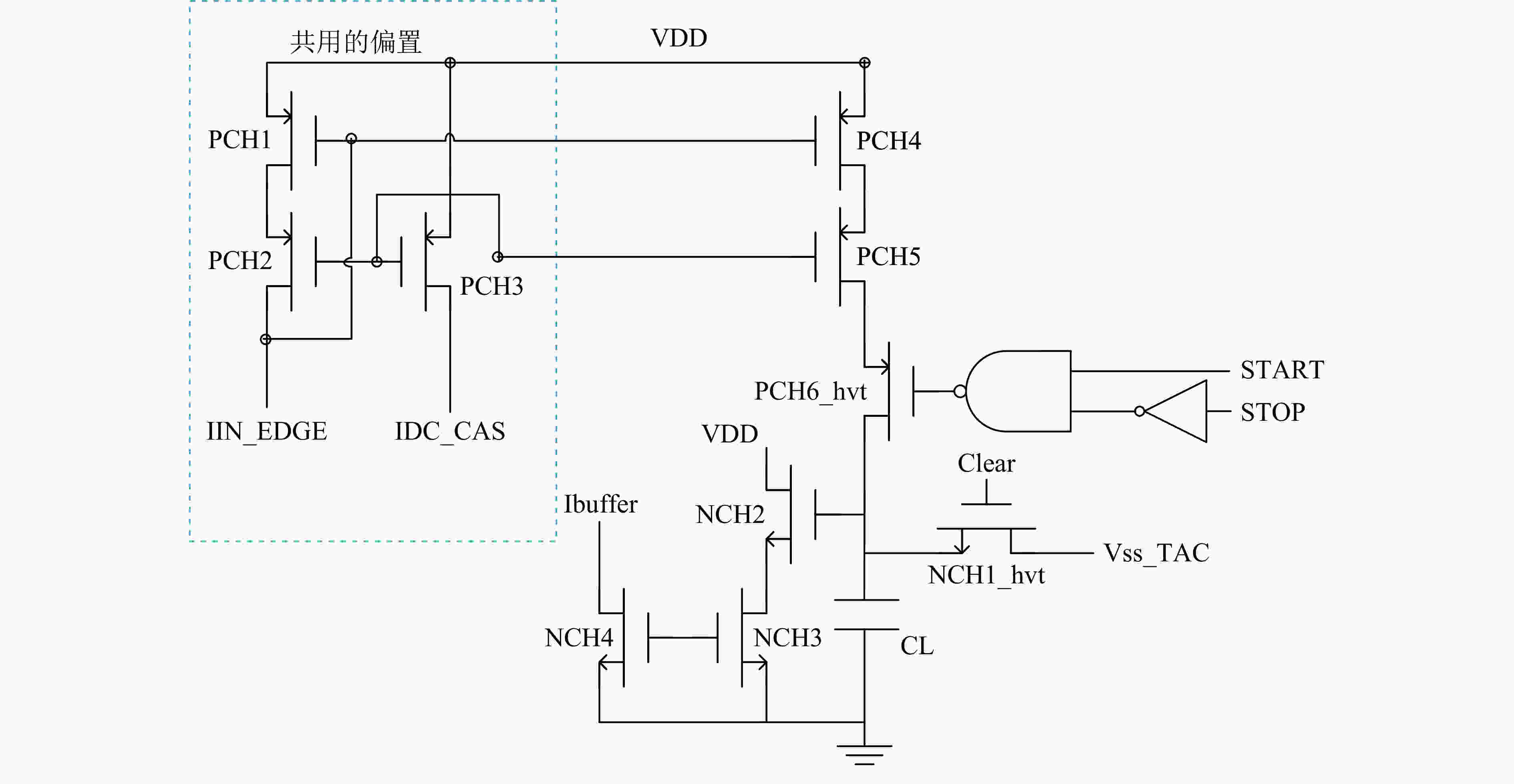

输入级电路输出22组启停信号,分别送给22路TAC电路处理。TAC电路结构如图5所示。

PCH4和PCH5共同组成电流源,采用共源共栅的结构以增大输出阻抗,组成线性度更优越的电流源。PCH1~PCH3组成电流源的偏置电路,采用宽摆幅的偏置电路对电流源进行偏置,以使电流源获得更大的线性区间。并且因为电源电压为1.2 V,为了进一步扩大线性区间,PCH4和PCH5被偏置在亚阈值区域[17],以降低PCH4和PCH5的过驱动电压和功耗。电流源的输出阻抗可由式(1)表达:

$$ {R_{{\text{out}}}} = \frac{4}{{{\lambda _4}{\lambda _5}{v_{{\text{dsat}}4}}{v_{{\text{dsat}}5}}}} \text{,} $$ (1) 其中:

$\lambda $ 4和$\lambda $ 5为PCH4、PCH5的沟道长度调制系数、反比于沟道长度;$ {v_{{\text{dsat4}}}} $ 和${v_{{\text{dsat5}}}}$ 为PCH4、PCH5的过驱动电压。因为它们都被偏置在亚阈值区域(过驱动电压较小),并且选择较大的沟道长度,使得${R_{{\text{out}}}}$ 数值非常大,相应的电流源的线性度就会非常好。PCH6_hvt为电流源的开关(需要使用dummy PMOS减弱开关的非理想效应,图中未标出),选择阈值电压高的PMOS制作,以阻止负载电容上的存储电压因为漏电流而在PCH6_hvt关断后被继续充电。START信号打开开关,电流源对负载电容CL充电,STOP信号关断开关,停止充电。复位开关NCH1_hvt同样采用高阈值NMOS制作(同样需要dummy NMOS处理其非理想效应),并且复位电压设定为VSS_T2A进一步降低NCH1_hvt的漏电流。合理调节PCH6_hvt和NCH1_hvt的尺寸,使得两个MOS的漏电流相接近,减小漏电流对CL存储电压的影响。负载电容CL在PCH6_hvt打开的瞬间,因为电荷转移效应,会存在电压的跳变,跳变过程结束后开始以电流源输出的恒定电流进行充电,也就是说电容上的电压存在一段非线性区间。因此电容上的电压随着时间的变化可由式(2)表达:

$$ {V_{\text{n}}} = \frac{{{I_{{\text{DC}}}}}}{{{C_{\text{L}}}}}(t - {t_{{\rm{ref}}}}) + {V_{{\text{ref}}}} \text{,} $$ (2) 其中:Vn为电容上存储的电压值;IDC为电流源的输出电流值;CL为负载电容大小;tref为电压线性区间的起始参考时间点;Vref为参考时间时刻电容上的参考电压值。据此给出了Vn随着时间t (t >tref) 变化的表达式。由2.2节所述,START和STOP信号的时间差的范围为 1~3 ns。而造成非线性的原因:电荷转移效应是非常迅速的,仿真显示在几百ps左右。因此对于待测时间差,Vn是线性的。调节CL和IDC的大小,使得在时间差1~3 ns范围内,Vn的线性度达到要求。时间测量bin size达到10 ps,细时间测量范围为2 ns,因此要求分辨率达到1/200,据此仿真TAC得到合适分辨率的设计。需要强调的是,因为电荷转移,线性区间不从零时刻开始,这对于时间戳型的TDC而言是没有影响的,对于启停型的TDC是有影响的,这时需要通过增大负载电容的数值来减小因电荷转移而产生的电压误差。此次设计的TDC为粗计数和细计数共同构成一个时间戳型的TDC,对这个效应不再做处理。

TAC另外一个重要的性能指标是它的噪声水平,主要由MOSFET贡献的沟道热噪声和低频噪声在负载电容上积分形成,经过推导,主要的噪声可由式(3)表达:

$$\begin{split} \frac{{\overline {v_{\text{n}}^{\text{2}}} }}{{v_{{\text{binsize}}}^{\text{2}}}} =& \frac{1}{{2I_{{\text{DC}}}^2}}\left[ {\frac{K}{{{{(WL)}_4}{C_{{\text{ox}}}}}}g_{{\text{m}}4}^2 + \frac{K}{{{{(WL)}_1}{C_{{\text{ox}}}}}}g_{{\text{m}}4}^2} \right]\frac{1}{{{C_{\text{L}}}}} \times \\& {\left( { \frac{{{t_{{\text{sd}}}}}}{{{t_{{\text{bin}}}}}} } \right)^2} + \frac{8}{3}kT{g_{{\text{m}}4}}\frac{1}{{I_{{\text{DC}}}^2}}\frac{{{t_{{\text{sd}}}}}}{{t_{{\text{bin}}}^2}} \text{,} \end{split} $$ (3) 其中:

$\overline {v_{\text{n}}^{\text{2}}} $ 为噪声积分的平均功率;$v_{{\text{binsize}}}^{\text{2}}$ 为充电tbin (即为设计精度)时长的积分电压的平方,二者的比值即为信噪比平方的倒数;IDC为电流源的输出电流值,(WL)4、(WL)1分别为PCH4、PCH1宽长的乘积;gm4为PCH4的跨导;tsd为待测时间差;K为低频噪声系数;k为玻尔兹曼常数;T为温度;Cox为MOSFET单位面积的电容大小。可以看到,选择大面积的电流源、大的电容、减小PCH4的跨导值有利于噪声的降低,同时需要注意随着待测时间差的增加噪声会增大,因此待测时间差最大处噪声水平最差。电容上存储的电压经过由NCH2~NCH4组成的源跟随buffer送到后续电路处理,需要指出的是,输出电压从NCH2的源级接出。采用源跟随buffer的原因是其线性度较高并且结构简单,如果想要实现相同的线性度的闭环buffer需要很高增益的两级运放搭建,因为同样需要22个buffer,因此选择源跟随buffer。优化其线性区间和噪声水平使得能够达到要求即可。

优化后给出最终的设计结果:22路共用的偏置IIN_EDGE为50 μA,IDC_CAS为2 μA。充电开关PCH6_hvt打开时充电电流为50 nA,充电电容设计为100 fF。buffer的偏置电流设计为100 nA。

-

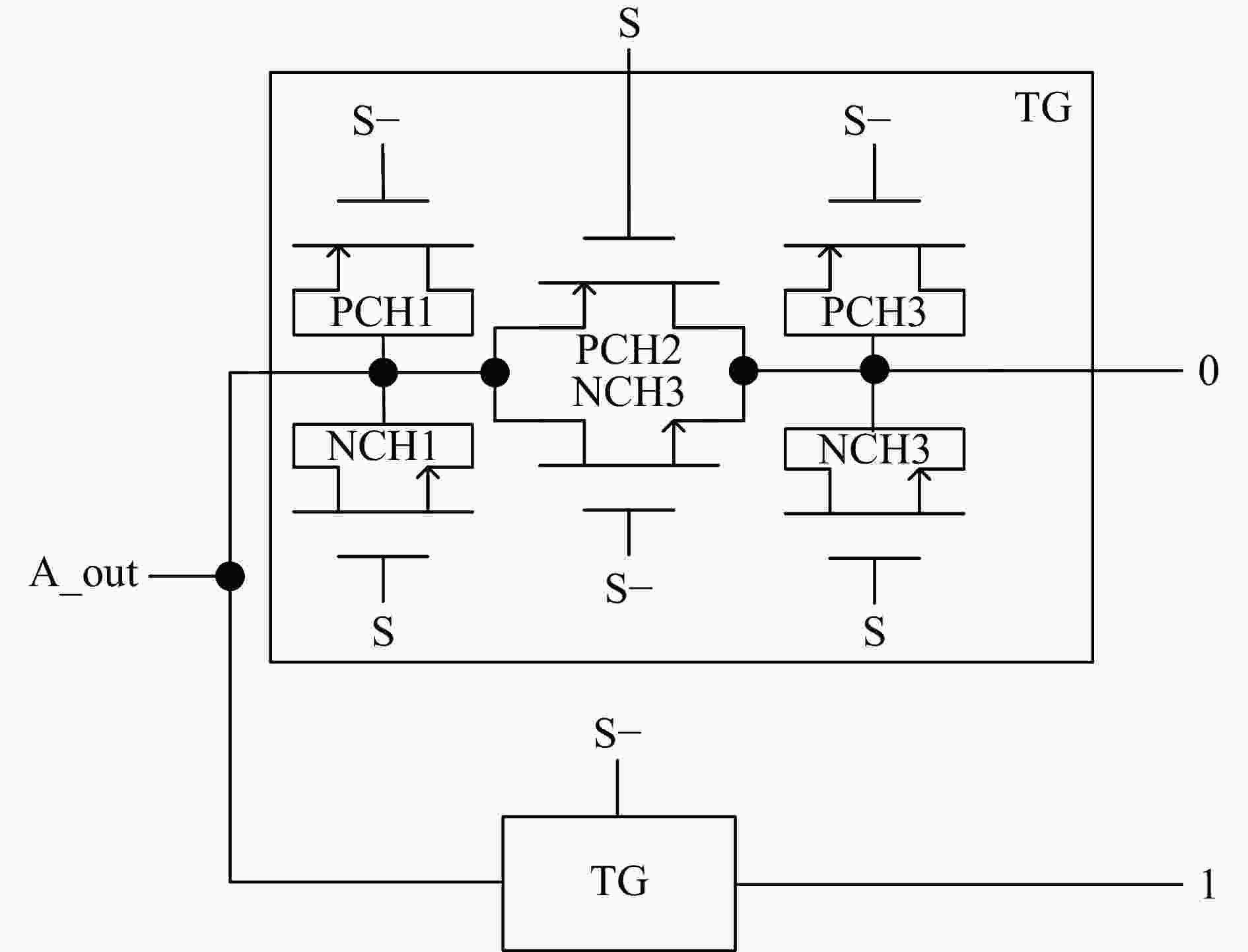

buffer的输出电压送入模拟多路选择器处理,模拟多路选择器需要设计为22选1的模拟选通器,采用多个2选1选通器级联的方式实现这个模块。选通器的输出送入ADC进行量化得到对应的细计数结果。10 ps对应1/200的分辨率,因此需要8位的ADC,考虑到噪声和非线性,设计为10位的ADC,以留有足够的冗余。这样精度的ADC有很多实现方式,出于对于面积制约的考虑,选择为结构简单的威尔金森ADC[18]。ADC和模拟多路选择器的具体结构和互连如图6所示。

因为需要逐个扫描22个TAC的输出电压,至少需要5级控制,控制信号为D0~D4。组成这个模块的基本单元电路为A_MUX,是由两个反向信号控制的CMOS传输门构成,图7给出其原理图,其中S和S-为两个反向信号。CMOS传输门加入dummy MOS,合理地调节每个MOS的长度和宽度,尽可能地减小时钟馈通和电荷注入的非理想效应的影响。当然,因为在进入模拟选通器之前已经加入了buffer,这里对非理想效应的处理仿佛不是那么关键,但是因为TAC部分的电容很小,仅仅0.1 pF,对于这么小的电容要格外关注所有可能的寄生电容的馈通影响。时钟馈通和电荷注入都会引起电压的快速变化,而buffer的驱动能力基于功耗考虑设计得非常有限,因此可能会通过buffer串扰到TAC的充电电容上,故这里对于开关非理想效应的处理是必要的。

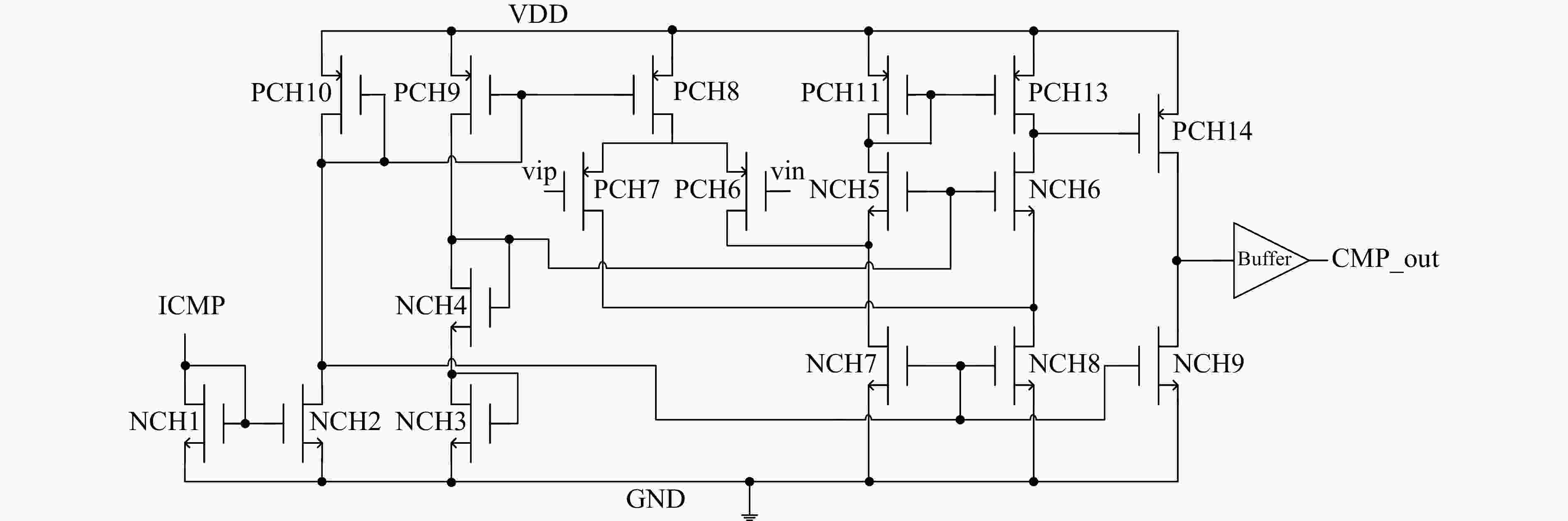

威尔金森ADC为单斜坡ADC,主要由三部分组成:斜坡信号发生电路、比较器电路、计数器。斜坡信号在Clear降为逻辑低电平的时候开始以固定斜率上升,并同时启动计数器开始计数。如图6所示,斜坡信号发生器的输出即斜坡信号Ramp_out送到比较器CMP的负端,CMP的正端接模拟多路选择器的输出即待测通道的电压信号。当斜坡信号上升到超过待测电压信号时,比较器翻转输出CMP_out,并同时锁存计数器的计数值。斜坡信号发生电路和2.3节设计的TAC电路类似,但是这里需要处理开关的非理想效应,加入了dummy MOS来改善非理想效应。给出斜坡发生器优化后的设计结果:偏置电流共计700 nA,充电电流为500 nA,充电电容为 3 pF。计数器的时钟为500 MHz,即周期为2 ns。为了确保ADC为10位的分辨率,则斜坡信号要确保在最差的工艺角下满足对应的满摆幅的转换时间大于2 μs,据此确定斜坡信号的斜率。比较器模块的具体结构由图8给出,为满足ADC的分辨率需求,比较器需要足够大的增益 (大约为60 dB),采用两级运放以达到上述增益。为了增大允许的输入电压范围,PCH6和PCH7差分输入级采用折叠的结构。第一级运放的输出加入共源共栅管NCH5和NCH6以隔离第一级输出到输入经过寄生电容的馈通,负载为有源电流镜。第二级采用共源级放大器,负载为电流源。除了分辨率需要关注,另外一个需要关注的是比较器输出的抖动,其大小可用式(4) [19]给出:

$$ {\sigma _{\text{t}}} = \frac{{\sqrt {\overline {v_{\text{n}}^{\text{2}}} } }}{k} \text{,} $$ (4) 其中:σt为比较器输出信号的抖动;k为斜坡信号的斜率;

$\overline {v_{\text{n}}^2} $ 为输入噪声电压的平方。输入噪声电压包含斜坡信号发生器输出的斜坡信号噪声电压、TAC输出的待测信号的噪声电压以及比较器的等效输入噪声,前两者噪声电压在形式上类似于式(3)给出的结果,优化方向也是类似的。至于比较器的等效输入噪声电压,其谱密度$\overline {v_{\rm in}^2} $ 可表达如式(5)所示:$$ \overline {v_{{\text{in}}}^2} = 2 \times \left( {\frac{8}{3}kT\frac{1}{{{g_{{\text{m}}6,7}}}} + \frac{K}{{{{(WL)}_{6,7}}{C_{{\text{ox}}}}}}\frac{1}{f}} \right) , $$ (5) 其中:gm6,7为差分输入对的跨导;(WL)6,7为差分输入对的面积;f为信号频率。因此通过增大差分输入对的面积,增大它们的跨导可有效地减小比较器的等效输入噪声。值得强调的是,因为比较器作为模拟选通器的负载接在其输出端,二者实际上都是由TAC的buffer驱动的,过大的输入电容会对buffer的驱动能力提出高的要求,因此需要在噪声水平和功耗之间寻求一个折衷以满足预期指标。最终设计结果为:运放的第一级尾电流源PCH8的偏置电流为2 μA,第一级负载PCH11的偏置电流为1 μA,输出级的偏置电流为2 μA。即比较器的功耗为6 μA,若计入偏置部分也不会超过其两倍。

计数器电路采用格雷码计数,以使得锁存结果最多和真实数值相差1 LSB的误差[20]。同时设计控制逻辑电路控制ADC和模拟选通器的工作,最终实现ADC对22路待测信号的逐个采样。

-

因为需要测量速度2 GHz的信号,这样的信号因为芯片输入IO的限制难以从片外输入,因此设计了测试电路以产生高速信号送入TDC中进行测试。测试电路和TDC的互连如图9所示给出。

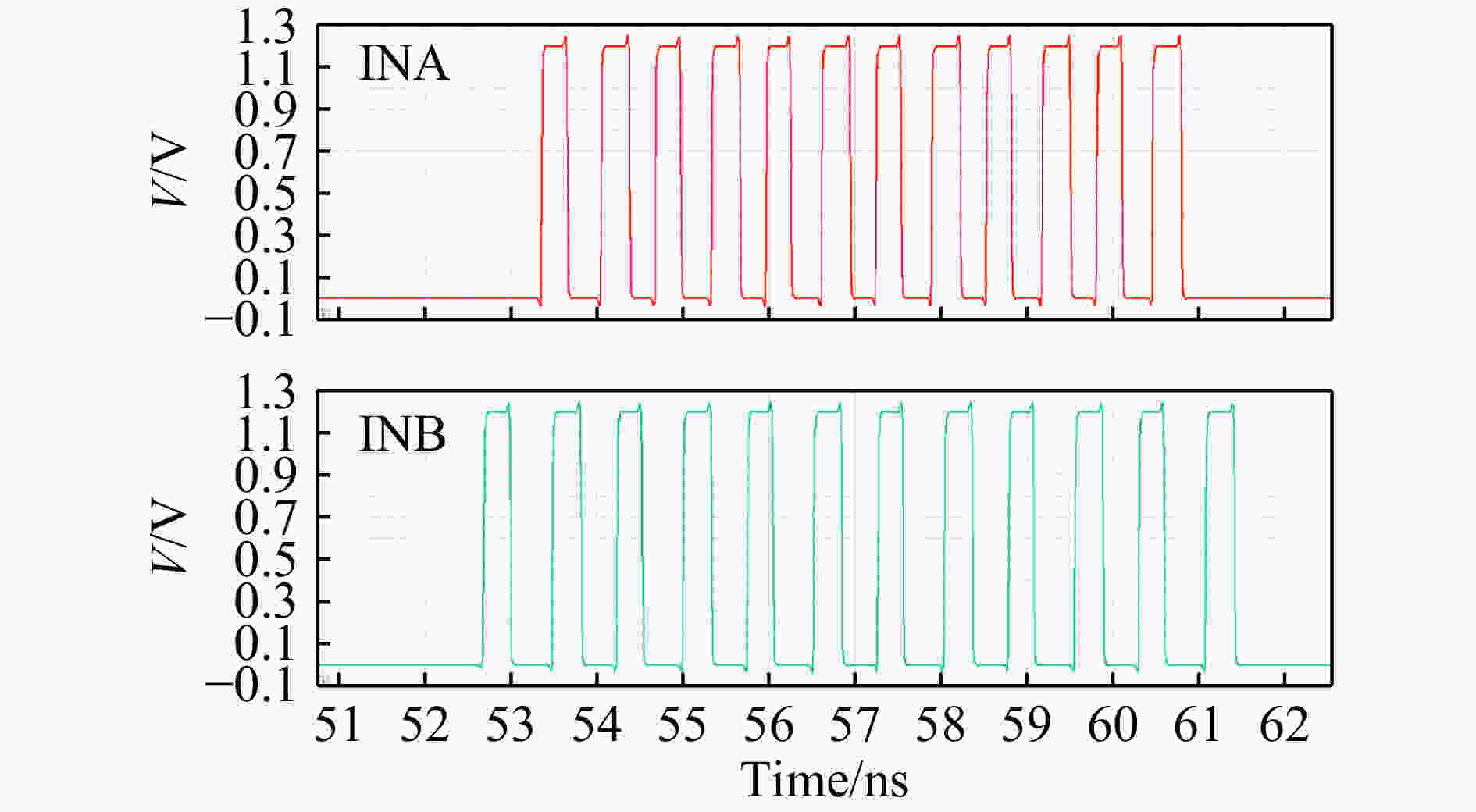

测试电路由12个像素单元PXL组成,被分成两列,以模拟像素点被击中的情况。每一列信号由一个TDC来测量其时间信息。图10给出测试电路的仿真结果,显示能够产生相邻脉冲时间间隔最短500 ps的信号。

-

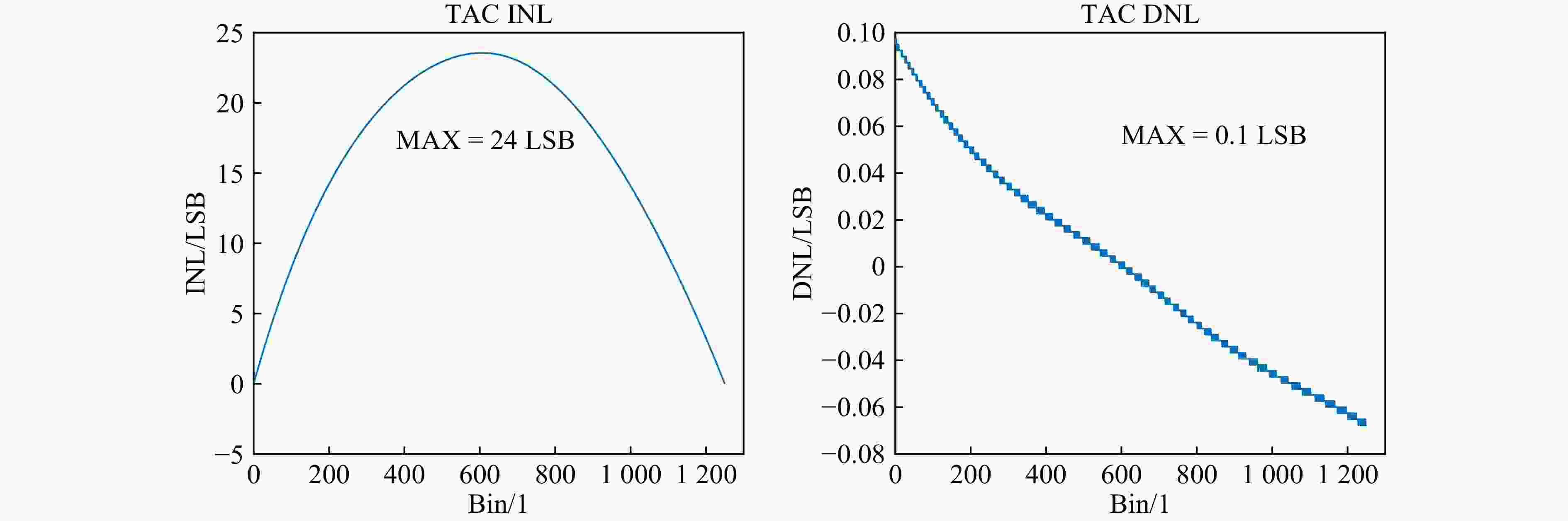

TDC关注的主要指标性能为bin size、精度。依次给出仿真结果,并且为了更好地分析影响bin size和精度的主要模块,抓取TAC的输出信号作为中间信号分析其bin size和精度。图11给出TAC输出信号的线性度:DNL(Differential Non-Linearity)和INL (Integral Non-linearity)的仿真结果。仿真结果显示,TAC的INL不理想,最大值达到24 LSB,需要进行标定。DNL的结果较为理想,最大仅有0.1 LSB。

INL的不理想是TAC结构存在的固有问题,但是,在设计时选取合适的线性区间,增大电流源的输出阻抗会减小DNL的数值。

图12给出整体的TDC的DNL和INL的仿真结果,由图可知 DNL 最大为1.4 LSB,其中bin size在最差的工艺角下的仿真结果达到2 ps;INL最大为25 LSB,主要是TAC模块引入的积分非线性。仿真结果显示,bin size能够达到10 ps的预期指标。

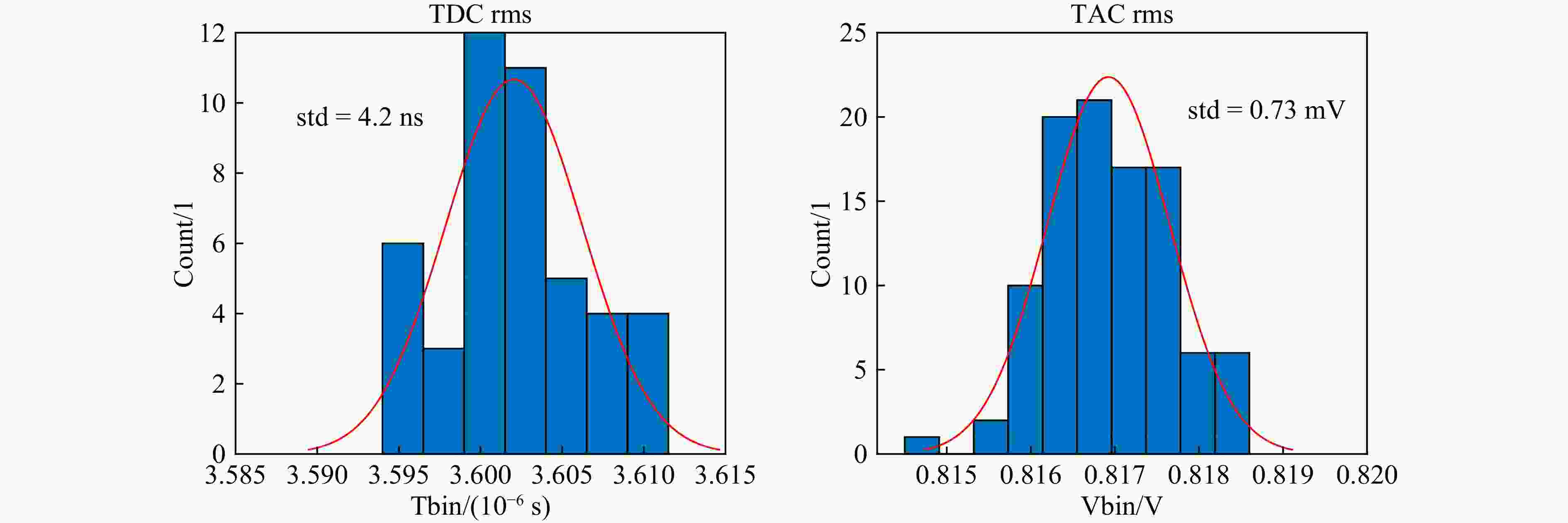

图13给出TAC和TDC噪声性能仿真结果。其中TDC的噪声性能采用瞬态噪声仿真的方法,仅添加了MOSFET的噪声,选取比较器模块的过阈时间来衡量TDC的噪声性能。最差的工艺脚下,TAC将范围为1~3 ns的输入时间间隔转换为一定范围的待量化电压,这个范围的待量化电压对应了Ramp_out信号的转换时间范围为2 μs,格雷码计数器时钟周期为2 ns,则2 ns对应细计数1 LSB。因此,MOSFET噪声引入的TDC的精度为4.2 ps RMS。同样对TAC的仿真结果分析,经仿真知TAC满量程约为430 mV,设计为10位,则1 LSB对应的电压值约为0.43 mV,因此转换为输入时间间隔后,TAC的精度为3.4 ps RMS。相较于ADC,TAC贡献了大部分的噪声。

-

在本论文的工作中,针对像素探测器读出电子学对于时间测量的特殊需求,设计完成了具备多事例处理能力(相邻事例时间间隔最短为500 ps)和高精度的TDC ASIC原型电路。

针对主要的设计难点提出了解决方法:

(1) 如何在有限的40 μm宽度范围内处理高速的多事例信号——设计了输入级电路对输入信号进行了预处理,降低了TDC速度的要求。

(2) 如何获得高的时间测量精度——采用粗细结合的测量方案实现了较高的精度。

对ASIC的主要性能指标进行了仿真, 仿真结果显示bin size达到了2 ps,DNL小于2.8 ps,精度好于5 ps RMS,达到了预期指标性能需求。后续会完成对原型芯片功能和性能的测试,给出芯片的实测结果。

Design and Simulation of High Event Rate and High Precision TDC ASIC Prototype for Pixel Detector

-

摘要: 像素探测器因其优异的位置分辨能力在高能粒子物理实验的内径探测器中有着广泛应用,随着应用场景的发展,许多物理实验要求探测器及其读出电子学也具备高精度时间测量的能力。针对像素探测器时间测量的需求,设计完成了一款具备高事例率处理能力、高精度特点的TDC(Time-to-Digital Conversion) ASIC(Application Specific Integrated Circuit) 原型电路,将来可以作为核心组成部分集成到像素探测器前端读出ASIC中。采用粗细结合的方案完成TDC的设计,其中粗时间测量基于计数器实现,细时间测量采用TAC(Time-to-Amplitude Converter)结合ADC(Time-to-Amplitude Converter)的结构实现,基于130 nm工艺完成了原型电路的设计。对TDC进行仿真,仿真结果表明,该电路可以最多处理连续11个事例,相邻事例的最短时间间隔为500 ps,bin size达到了2 ps,DNL(Differential Non-Linearity)小于2.8 ps,时间测量精度好于5 ps RMS。Abstract: The pixel detector has been widely used in the inner track detector of high energy particle physics experiments because of its excellent position resolution. With the development of physics experiments, many experiments require detectors and readout electronics to have the capability of high-precision time measurement. To reach the requirement of pixel detectors about the time measurement, a TDC(Time-to-Digital Conversion) ASIC(Application Specific Integrated Circuit) prototype with high event rate processing capability and high precision has been designed. It is expected to be integrated with the front-end readout ASIC of pixel detector as a core component in the future. TDC presented in this paper adopts the combination of coarse and fine measurement, in which the coarse time measurement is based on the counter, and the fine time measurement is implemented by employing the architecture of TAC(Time-to-Amplifier Converter) combined with ADC(Analog-to-Digital Converter). The prototype circuit has been designed based on 130 nm process. TDC has also been simulated, the simulation results indicate that the circuit has the capability processing up to 11 consecutive events in which the time interval between adjacent events is as small as 500 ps, while the bin size of TDC is 2 ps, the DNL (Differential Non-Linearity) is less than 2.8 ps, and the time measurement precision is better than 5 ps RMS.

-

Key words:

- pixel detector /

- high event rate /

- high precision /

- TDC /

- ASIC

-

表 1 单通道TDC的指标需求

指标 TDC 精度 优于10 ps RMS bin size 优于10 ps 速度 2 GHz(最多处理10个信号) -

[1] ERIK H M H. Nucl Instr and Meth A, 2001, 465(1): 1. doi: 10.1016/S0168-9002(01)00340-0 [2] KAZUYOSHI A, MARINA A, RYAN B, et al. Nucl Instr and Meth A, 2011, 661(1): 31. doi: 10.1016/j.nima.2011.09.021 [3] RAFAEL B, MICHAEL C, XAVIER L. Nucl Instr and Meth A, 2018, 878(1): 10. doi: 10.1016/j.nima.2017.07.029 [4] LLOPART X, BALLABRIGA R, CAMPBELL M, et al. Nucl Instr and Meth A, 2007, 581(1): 485. doi: 10.1016/j.nima.2007.08.079 [5] POIKELA T, PLOSILA J, WESTERLUND T, et al. Journal of Instrumentation, 2014, 9(5): 5. doi: 10.1088/1748-0221/9/05/C05013 [6] LLOPART X, CAMPBELL M, DINAPOLI R, et al. Nuclear Science IEEE Transactions on, 2002, 49(5): 2279. doi: 10.1109/TNS.2002.803788 [7] BALLABRIGA R, CAMPBELL M, HEIJNE E, et al. Nucl Instr and Meth, 2011, 633: 15. doi: 10.1016/j.nima.2010.06.108 [8] FAG Y, GAO C, HUANG G, et al. arXiv: 1407.3712v1. [9] PERIC I, BLANQUART L, COMES G, et al. Nucl Instr and Meth A, 2006, 565(1): 178. doi: 10.1016/j.nima.2006.05.032 [10] ARUTINOV D, BARBERO M, BECCHERLE R, et al. IEEE Transactions on Nuclear Science, 2009, 56(2): 388. doi: 10.1109/TNS.2009.2015318 [11] MAZZA G, CALVO D, REMIGIS P D, et al. Journal of Instrumentation, 2012, 7(02): 02015. doi: 10.1088/1748-0221/7/02/c02015 [12] TREMSIN A S, VALLERGA J V, MCPHATE J B, et al. IEEE Transactions on Nuclear Science, 2013, 60(2): 578. doi: 10.1109/TNS.2012.2223714 [13] MARTISIKOVA M, HARTMANN B, GWOSCH K, et al. Study of Thecapabilities of the Timepix Detector for Ion Beam Radiotherapy Applications[C]// IEEE Nucl Sci Symposium and Medical Imaging Conference, NSS/MIC , 2012: 4324. [14] LJUSLIN C, CHRISTIANSEN J, MARCHIORO A, et al. IEEE Transactions on Nuclear Science, 1994, 41(4): 1104. doi: 10.1109/23.322866 [15] PORAT D I. IEEE Transactions on Nuclear Science, 1973, 20(5): 36. doi: 10.1109/TNS.1973.4327349 [16] CHEN Y, DENG Z, LIU Y. Journal of Instrumentation, 2018, 13(07): 07023. doi: 10.1088/1748-0221/13/07/P07023 [17] DO A V, BOON C C, DO M A, et al. IEEE Transactions on Microwave Theory & Techniques, 2008, 56(2): 286. doi: 10.1109/TMTT.2007.913366 [18] FERRAGINA V, MALCOVATI P, BORGHETTI F, et al. Implementation of a Novel Read-out Strategy Based on a Wilkinson ADC for a 16×16 Pixel X-ray Detector Array[C]//International Symposium on Circuits & Systems. DBLP, 2005. [19] SPATHIS C, BIRBAS A, GEORGAKOPOULOU K, et al. Noise and Uncertainty in Comparator/TDC Sensor Readout Circuits[C]// 2017 International Conference on Noise and Fluctuations (ICNF), Vilnius, Lithuania, 2017. [20] NAGATA K, NEMENZO F. Some Properties of Binary Gray Code[C]//2015 International Conference on Computer Application Technologies, Matsue, Japan, 2015: 72. doi: 10.1109/CCATS.2015.27 -

下载:

下载:

甘公网安备 62010202000723号

甘公网安备 62010202000723号