-

高精度时间测量是核与粒子物理实验中读出电子学的核心任务之一,诸多能实现精密时间测量的方法已经被提出,而其中基于定时甄别加TDC(time-to-digital converter)的结构便是其中一个主流技术路线[1]。TDC作为该技术路线的主要组成部分在诸多物理场合中都有很好的应用[2],比如在ATLAS(A Toroidal LHC ApparatuS)的MDT(Monitored Drift Tube chambers)探测器中TDC ASIC(Application Specific Integrated Circuit)直接集成在前端电子学中参与信号的时间量化及数据传输[3-4],在BESIII(Beijing Spectrometer III)飞行时间(Time-of-Flight, ToF)监控系统中也将TDC作为时间测量模块的关键部分之一[5]。TDC在其他领域也有广泛应用,比如在无线传感网络以及物联网市场中迅速发展的ADPLL(All-Digital Phase-Locked Loop)中用于时钟相位差测量[6-7],在医疗成像领域中逐渐兴起的ToF正电子发射计算机断层成像技术(Positron Emission Tomography, PET)[8-9]里TDC通过测量射线抵达探测器的到达时间用于计算相应的位置信息,等等。随着对其的结构及性能探索的不断深入,越来越多TDC类型得以发展,并在对应领域有着优异的表现[10]。

模拟型TDC是较早得以发展的一类TDC,其主要设计思想是先利用TAC(Time-to-Amplitude Converter)将时间间隔转化为电压信号,再配合后端电路比如ADC(Analog-to-Digital Converter)实现时间数字化[2]。为了进一步提高精度,可以采用时间放大原理进行设计,比如基于双斜坡放大的电路结构[11]。尽管模拟型TDC通过细致的结构优化以及版图调整后可以实现很好的时间性能,但模拟电路的固有特性使其易受到噪声、干扰及电压波动等因素的影响,这促使人们进一步发展数字型TDC。

高精度数字型TDC中的典型代表有基于门延迟单元的链型或者环形振荡器型TDC[12-14],其使用低延迟单元进行时间内插从而实现门延迟级别时间测量,电路拓扑结构简单。相比于模拟型TDC,除了数字电路固有的较好的抗噪声特点,伴随着工艺的发展,延迟单元所能实现的最小延迟不断减小,因此可以实现的时间精度也不断提升。数字型TDC可以进一步分为FPGA(Field-Programmable-Gate-Array)TDC和ASIC TDC两种类型。前者利用FPGA内部资源,如延迟线或者查找表,可以实现高精度的数字TDC设计[15],FPGA可编程重构的特性使此类TDC设计的周期大为缩短,并提升了应用的灵活性。然而,由于FPGA属于通用型器件,在实现TDC设计时无法做到资源最优化目标下的专用化设计,尤其在大规模使用时因其成本高、效能比低等因素受到诸多限制。而ASIC TDC在这些方面优势明显,可以大大提高资源利用率,降低电路功耗,提高系统集成度从而降低平均成本[3]。

考虑到基于环形振荡器型TDC ASIC设计在拓扑上需要将延迟链弯曲成环形结构,在弯曲处势必会引入延迟的不一致,为了克服这一点需要额外的电路设计进行补偿[16]。就此方面考虑延迟链型TDC结构简单,能够较好地进行紧凑版图设计,提高集成度。基本延迟链TDC使用简单的门电路比如反相器作为延迟单元,单元首尾相连构成延迟链结合采样电路实现时间量化功能,电路能测量的最小时间间隔就是单个反相器延迟。但是该TDC基本单元延迟会受到工艺、电压以及温度(PVT)影响而变化,此时基于DLL(Delay-Locked Loop)的受控延迟链型TDC便是一种能减轻PVT影响的常用结构 [17-19]。

结合上述讨论,针对国内外大型粒子物理实验中对百皮秒量级的TDC一直有着较高需求[3, 20-21],本研究团队在180 nm CMOS工艺上基于DLL结构实现了原型TDC ASIC设计,芯片命名为Delay-locked loop based High Resolution TDC,简称DHR TDC。该ASIC工作旨在为了满足未来该领域物理实验的需求,需要发展国内自主设计TDC ASIC以作准备。考虑到TDC本身的核心指标在于位宽(bin size)及RMS精度,此原型芯片指标希望达到200 ps bin size,时间精度好于100 ps RMS。

为评估原型芯片性能,本论文将设计电子学测试模块,构建测试系统并进行性能测试,需完成对该TDC芯片的位宽、时间精度、DNL(Differential NonLinearity)以及INL(Integral NonLinearity)等指标的测量。

-

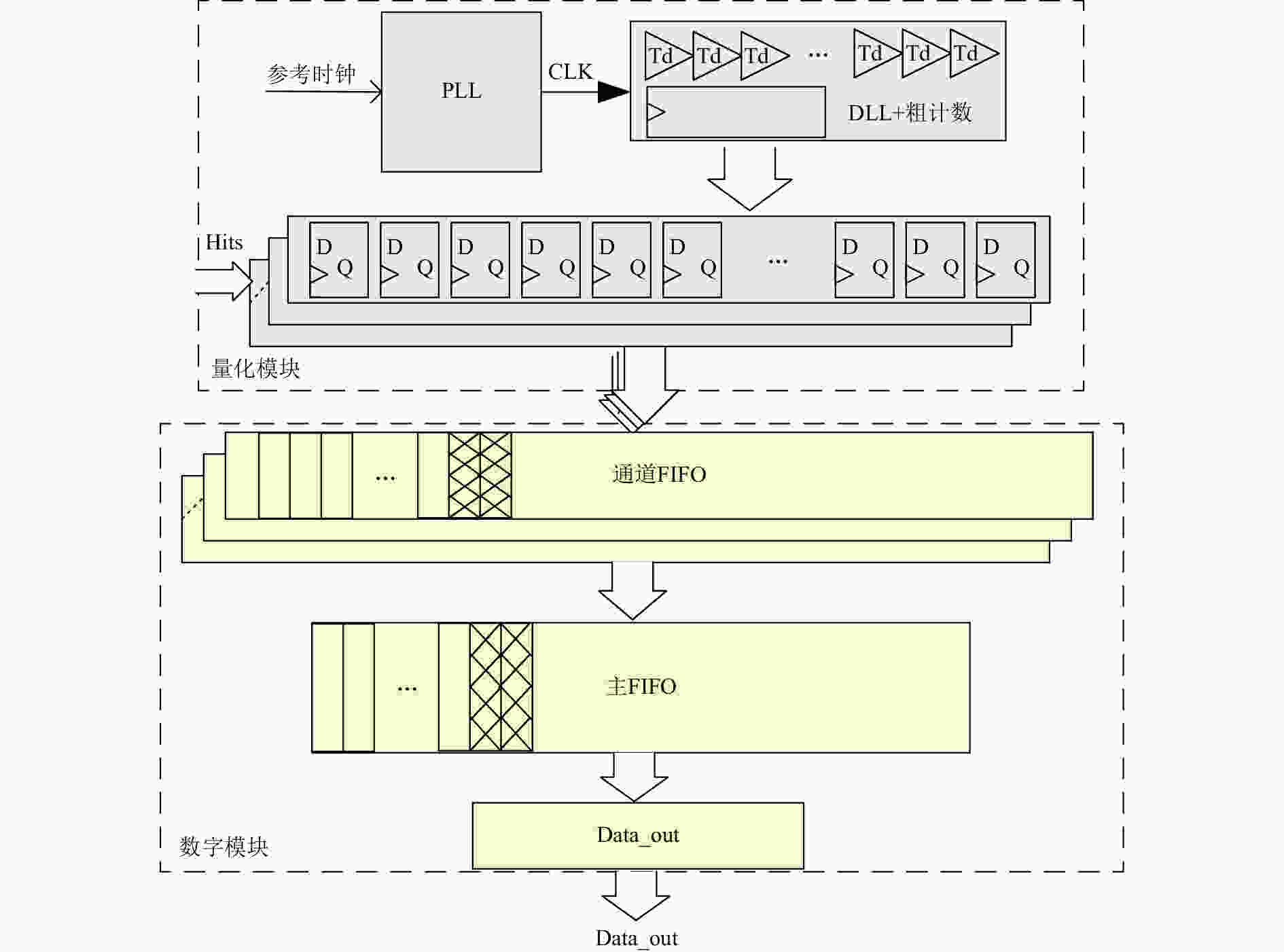

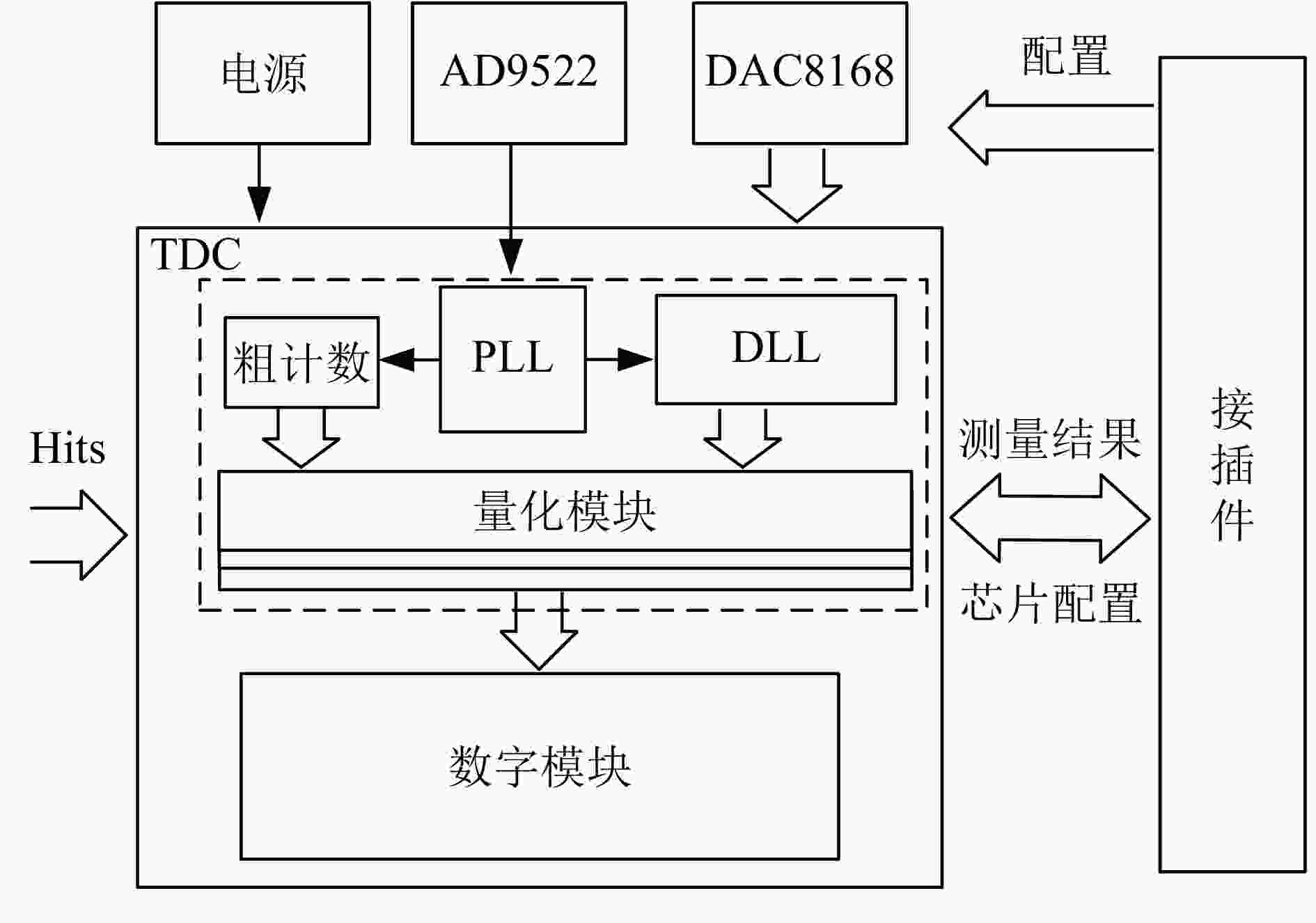

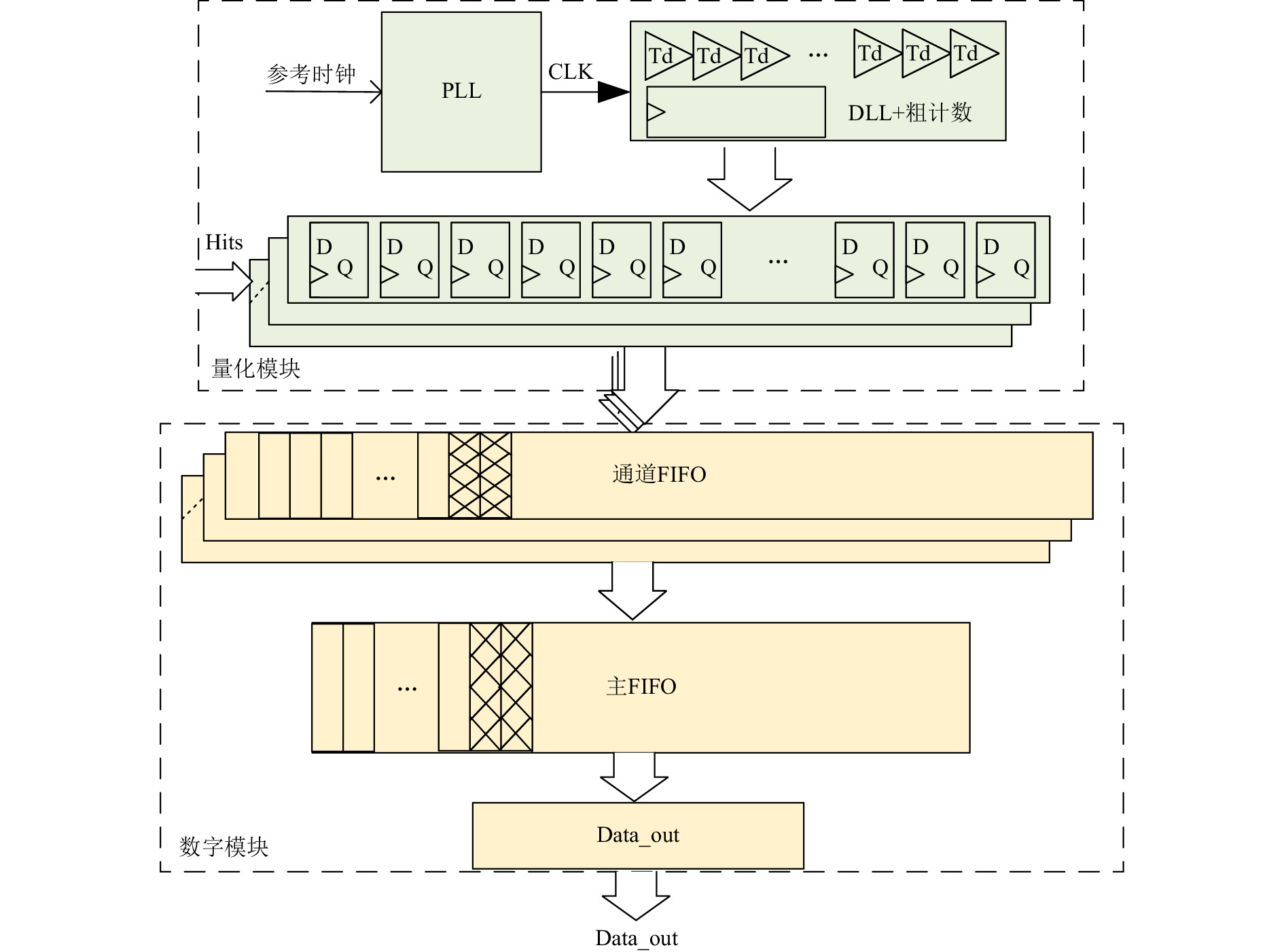

图1所示为原型TDC ASIC的基本结构示意图,芯片主要由量化模块和数字模块两部分组成。前者主要完成芯片的时间量化功能,片内集成PLL模块将参考时钟倍频成200 MHz粗计数时钟,该时钟在驱动12 bits的粗计数器的同时输入到DLL中进一步实现32分相作为量化细计数,从而在实现大测量范围同时得到高时间分辨。芯片采样电路由D触发器组构成,在相应通道时间信号Hit的触发下对粗计数和细计数进行采样进而完成时间量化。后者则是基于数字IC流程实现的数字模块,集成了通道缓存FIFO、公共存储FIFO以及后端数据打包处理等功能。

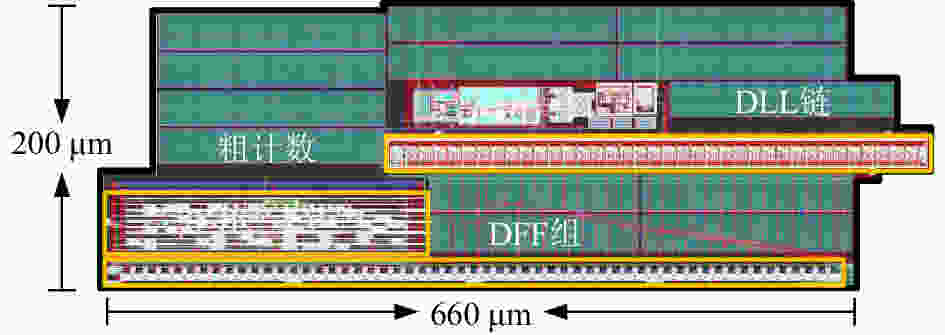

基于上述电路结构完成了相应的芯片设计及仿真,并基于180 nm CMOS工艺完成流片,图2为芯片关键量化部分版图。

-

为了评估该原型芯片的实际性能,同时为其后续进一步的改版设计工作提供参考依据,对该芯片进行充分的验证和测试是必要且有意义的。为了确保测试的完整性应当基于正确的测试方法测量TDC相应的主要指标。

-

LSB(Least Significant Bit)决定了TDC本身所能分辨的最小输入时间间隔,在两个LSB之间连续的时间间隔都会被量化为同一个码值。相对应的TDC的动态范围(Dynamic Range)则指其所能测量的最大时间间隔,大量程高精度的TDC设计是诸多应用场合中所需求的。对于一个TDC而言,其实际不同刻度间的bin size是存在差异的,这便对TDC的时间转换性能引入了非线性(Nonlinearity),DNL与INL常用于表征TDC的非线性并通常以LSB作归一化处理。同时量化RMS精度则是评估TDC性能的又一个关键指标,其一般用对相同时间间隔重复测量后量化结果的标准差表示。TDC的时间精度由公式

$\sigma_ {\rm{RMS}} = \sqrt {\sigma _{\rm{q}}^2 + \sigma _{{\rm{start}}}^2 + \sigma _{{\rm{stop}}}^2 + \sigma _{{\rm{others}}}^2}$ 决定,其中${\sigma _{\rm{q}}}$ 为TDC量化误差,${\sigma _{{\rm{start}}}}$ 与${\sigma _{{\rm{stop}}}}$ 则分别对应前后输入的起始待测脉冲和结束待测脉冲的自身误差,最后${\sigma _{{\rm{others}}}}$ 则表征了其余系统误差。另外TDC的量化死时间(Dead Time)对应于进行连续两次量化所需要的等待时间,本文中为信号锁定时钟型TDC,其通过待测信号上升沿对粗、细计数采样即完成量化,内核死时间一般很小,芯片整体死时间主要由系统读出决定。最后芯片的功耗以及面积也是评估芯片性能的常见指标[2]。 -

码密度法测试常常用于评估TDC的LSB以及非线性。其基本思想是由信号源产生一组周期信号送入TDC进行量化,由于该输入信号与TDC内部量化主时钟不同源,因而经过大量对输入脉冲信号的测量就能够遍历TDC的所有码值。这里码密度指的是大量测量后某个特定输出码值出现的次数,统计上反映了该出现码值的概率,其相对大小便对应了该刻度处bin size的相对大小,某处码密度为零则对应于失码情况。对于理想的TDC其所有bin size宽度相同,各个码值出现的概率呈均匀分布,对应的码密度也应相等[21-22]。

-

线延迟法测试可用于测量TDC的时间精度。其基本原理为由信号源产生多组具有固定时间间隔的两列信号,TDC对这两列信号进行大量测量之后便可以得到一组符合正态分布的TDC量化结果,取该组数据的标准差便可以表征测量的时间精度。考虑到一个量化结果是将两列信号量化后作差的结果,因而单个通道的时间精度应在此前基础上再除以

$\sqrt 2 $ [21]。当需要更高精度测量时,可先由信号源产生一组单脉冲信号经无源功分器分入两路不同长度的传输电缆,经TDC测量可以获得该输入时间间隔下的TDC自身测量误差。随后再由线延迟法测量该时间间隔下的总系统误差,此时将测得的TDC自身测量误差从系统误差中扣除就可以获得信号源的输出误差,从而在后续的测量中可以消除信号源引入误差[23]。 -

基于上述TDC测试的主要指标及方法,设计了相应的ASIC测试电子学模块,结合FPGA数字传输模块及相应软件构建了测试系统。

-

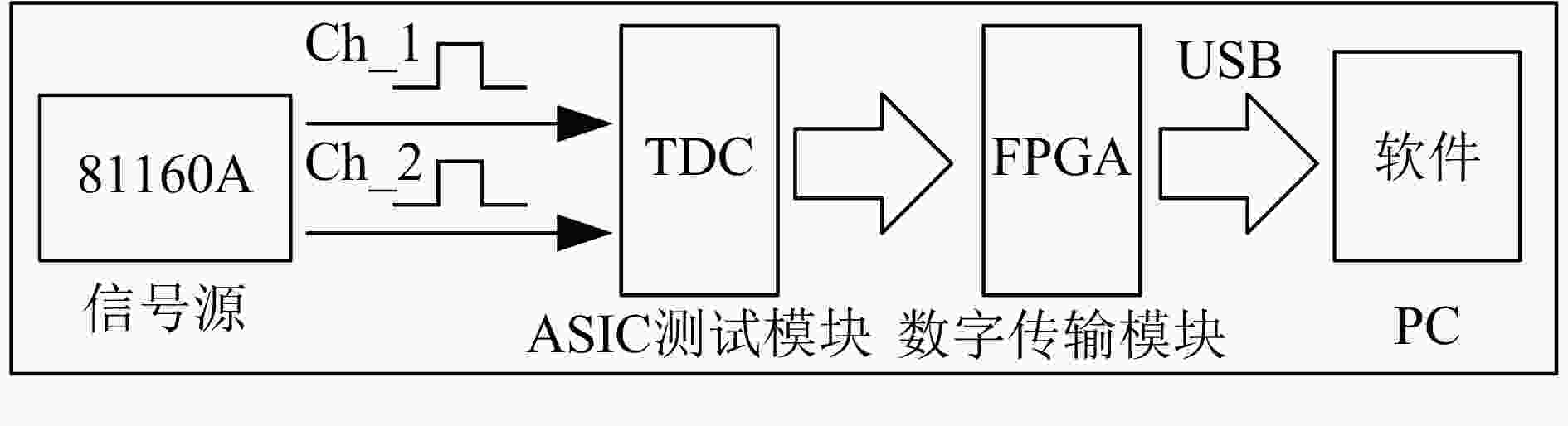

图3所示为该ASIC测试系统的基本示意图。为了实现准确的性能测量,选用较高性能的Agilent 81160A信号源,该信号源能够产生较快边沿的脉冲信号,同时在使用两通道输出固定时间间隔信号时能够以最小1 ps的步长调整间隔大小,输出时间间隔精度好于4 ps,考虑到TDC的最小测量步长,能够很好地评估其时间性能。基于码密度法或者线延迟法,使用信号源输出信号输入到设计的ASIC测试模块,测试模块为TDC芯片供电并配合后端逻辑完成对芯片相应配置,同时将信号源传输的待测信号送入芯片相应通道完成时间间隔测量并将结果传输到数字传输模块。数字传输模块上主要集成了一块Kintex-7 FPGA以及USB传输电路,FPGA内烧写相应逻辑用以完成TDC芯片的相应配置,同时接收TDC的量化数据并配合测试软件控制USB模块将数据传输至PC端。

-

ASIC测试模块主要包括TDC ASIC、相应的电源电路、DAC配置电路和参考时钟产生电路等,测试模块接收信号源产生的待测信号并将其送入芯片,同时通过接插件实现测试模块与数字传输模块的交互,接收来自FPGA对芯片的配置信号并将芯片输出送入FPGA。图4即为ASIC测试模块的基本结构示意图。

电源为测试模块各电路提供电源。其中在TDC ASIC上共用到1.8 V和3.3 V两种电源,同时为了保证部分关键电路的性能芯片将电源进一步区分了模拟电源与数字电源。在进行电源模块设计时考虑到各器件的功耗以及对纹波要求等,共使用了4块电源芯片进行供电,分别对应模拟1.8 V、3.3 V电源以及数字1.8 V、3.3 V电源。

另一方面,TDC内的PLL需要一个片外提供的参考时钟,该参考时钟质量会影响PLL输出时钟性能并最终影响芯片精度[24]。同时TDC数字模块也需要外部提供的逻辑时钟。综合上述考虑,在测试模块上选用了一块AD9522芯片结合晶振为TDC提供所需时钟,其输出时钟jitter好于1 ps RMS,满足TDC要求。同时, 时钟模块还支持通过LEMO接收外部提供时钟。

而DAC8168芯片为TDC提供了部分电路所需的参考电压以保证其稳定工作。ASIC测试模块与后端数字传输模块的数据交互经由一个接插件连接完成。

-

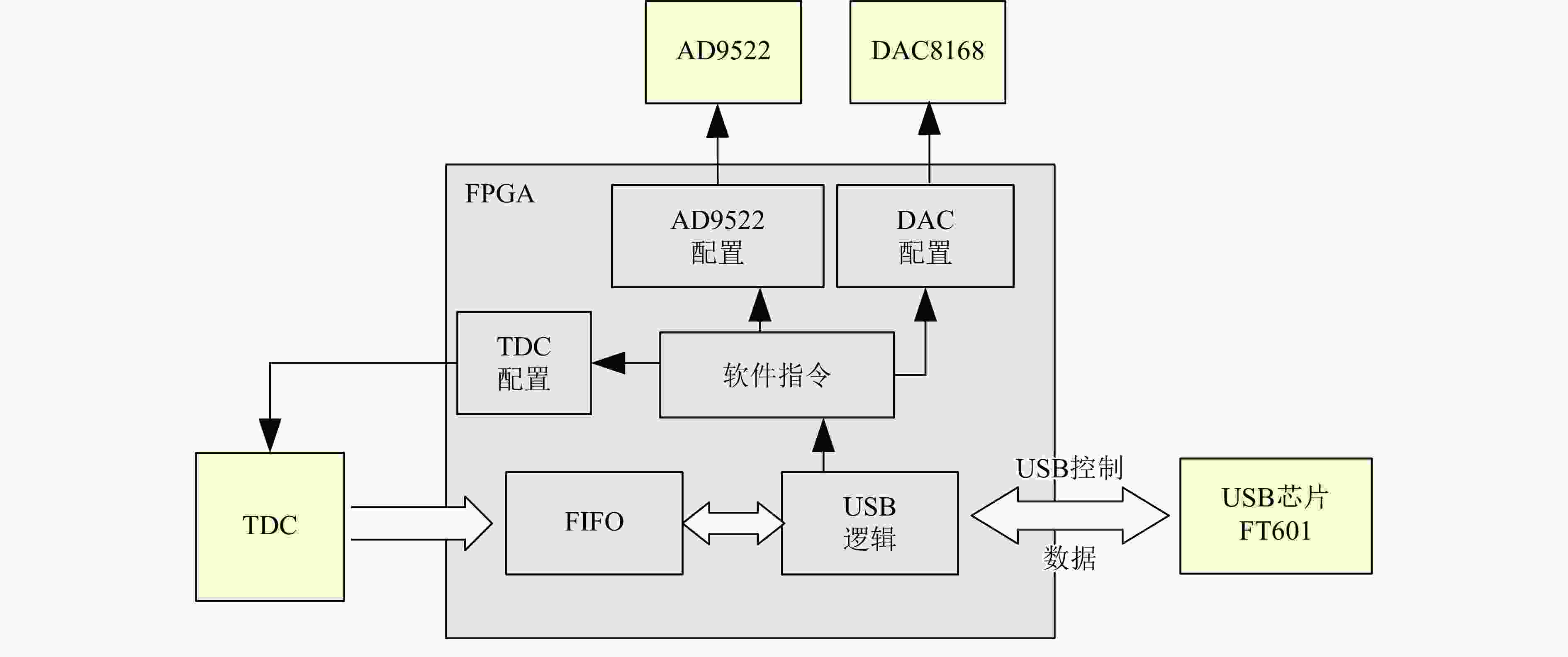

为了配合ASIC测试模块对TDC ASIC进行配置,完成量化结果的接收并将其传输到PC进行最终数据分析处理,需要设计相应的TDC测试FPGA逻辑。该逻辑包含多个功能:对TDC芯片数据的读写控制,部分数字配置以及片内PLL,DLL等电路的启动控制;对AD9522以及DAC8168的配置使其能向TDC提供正确时钟和参考电压;配合相应测试软件控制USB芯片将测试结果传输到PC端,同时支持使用软件实时配置ASIC测试模块工作状态。图5所示为整个FPGA内部逻辑结构示意图。

考虑到USB采用32位数据位宽传输,而TDC输出测量结果为8位传输,因而需要调用FPGA内IP资源实现8位转32位的存储FIFO,配合读写控制将测试结果正确地传输至PC。

-

基于码密度法及线延迟法,使用上述测试系统,完成了对TDC ASIC的所有测试,评估了芯片性能。图6所示即为实际测试系统现场图,TDC芯片采用了QFP128封装,尺寸约为16 mm×16 mm,晶核尺寸约为3 173 μm×2 613 μm。

-

基于码密度法,使用信号源产生一系列的周期脉冲信号,经测试系统完成数据传输能获得通道的原始时间码值。图7为进行10万次测量后测得的TDC细计数各个码值处对应的码密度分布。结合该码密度分布图分析可得TDC实际LSB约为156.3 ps。

结合码密度测试结果进一步分析可以得到TDC芯片的非线性,如图8所示芯片各个刻度bin size相对均匀,其DNL/INL好于0.13/0.15 LSB,此时芯片不需要额外的修正便可有较好的精度。

-

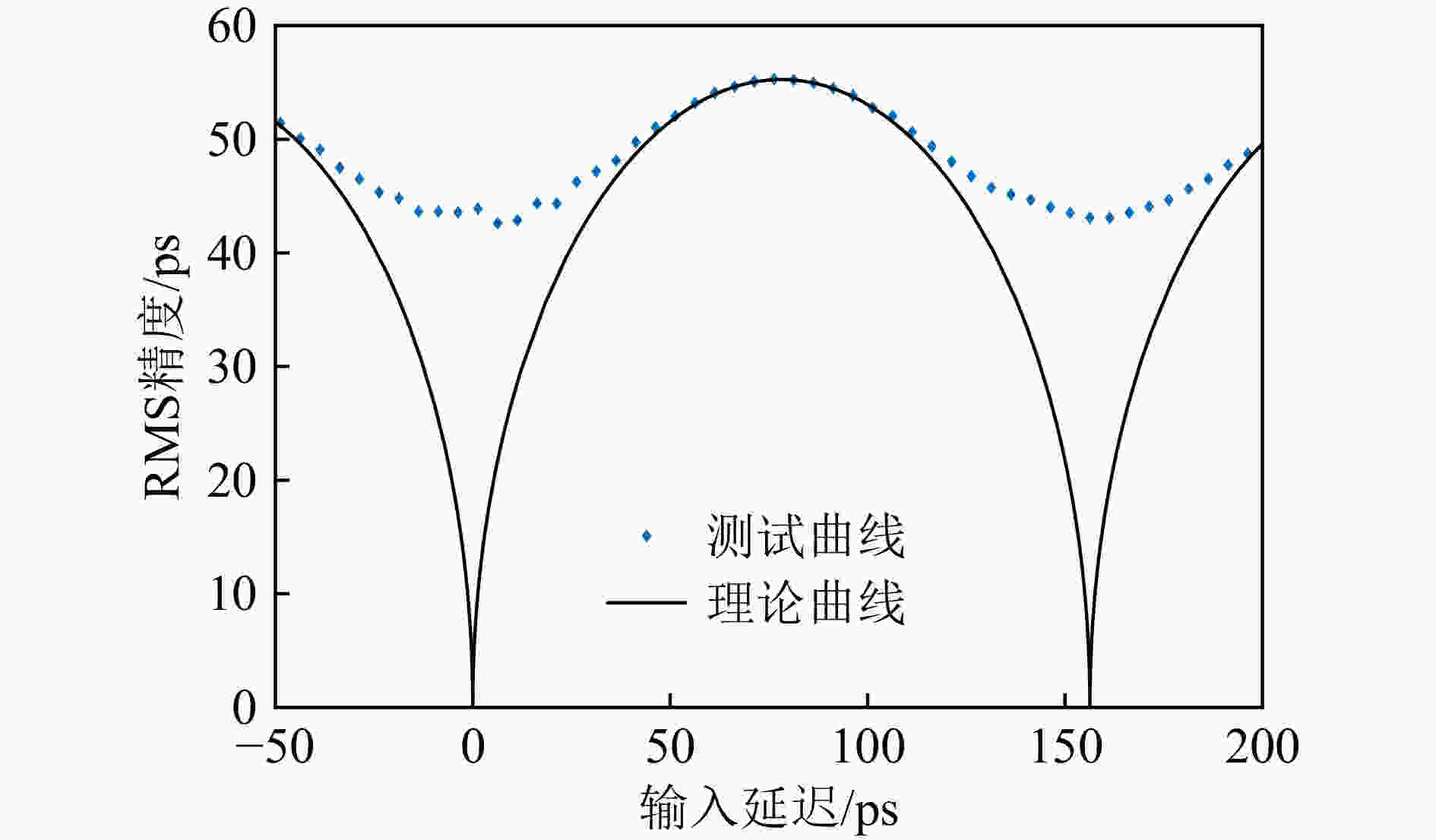

基于前文阐述的线延迟法进一步对芯片的时间性能进行了相应测试。对于理想TDC,其时间测量精度只受到量化误差影响,对于不同待测时间间隔的量化精度有所不同。若待测量时间间隔为T,记T_delta=T%LSB,则该TDC此时的量化RMS精度理论为

${\rm{LSB}} \times $ $ \sqrt {\frac{{T\_{\rm{delta}}}}{{{\rm{LSB}}}}\left(1 - \frac{{T\_{\rm{delta}}}}{{{\rm{LSB}}}}\right)} $ [25],即理想TDC的量化RMS精度以LSB为周期变化,当待测时间间隔为整倍数LSB时量化误差为0,而当间隔为整数倍加半个LSB时误差最大为0.5 LSB。考虑到线延迟法下TDC的一次时间间隔测量是由两个通道共同量化完成的,因而这个理论量化RMS精度分摊为单通道精度需再除以$\sqrt 2 $ ,即约为0.35 LSB[3]。基于上述讨论,需要以小步长调节输出延迟间隔以全面评估TDC的时间性能。相对于156.3 ps的LSB,测试通过信号源以5 ps为步长扫描了多个TDC位宽得到了如图9所示的TDC量化RMS精度曲线(虚线)与理论曲线(实线)的对比图。为了便于比较,图中x轴将实际测量时间间隔归一化到1 LSB内,可以看到TDC具有良好的时间性能,与理论曲线符合较好。当待测时间间隔为整倍数LSB时还存在一定误差,这是由于整体系统噪声以及TDC自身非线性所引入的影响。对于TDC而言,其噪声主要包括PLL与DLL电路输出的时钟相位噪声,时钟树及buffer树引入的电路噪声,芯片电源和地的串扰噪声以及采样电路亚稳态所引入的噪声。

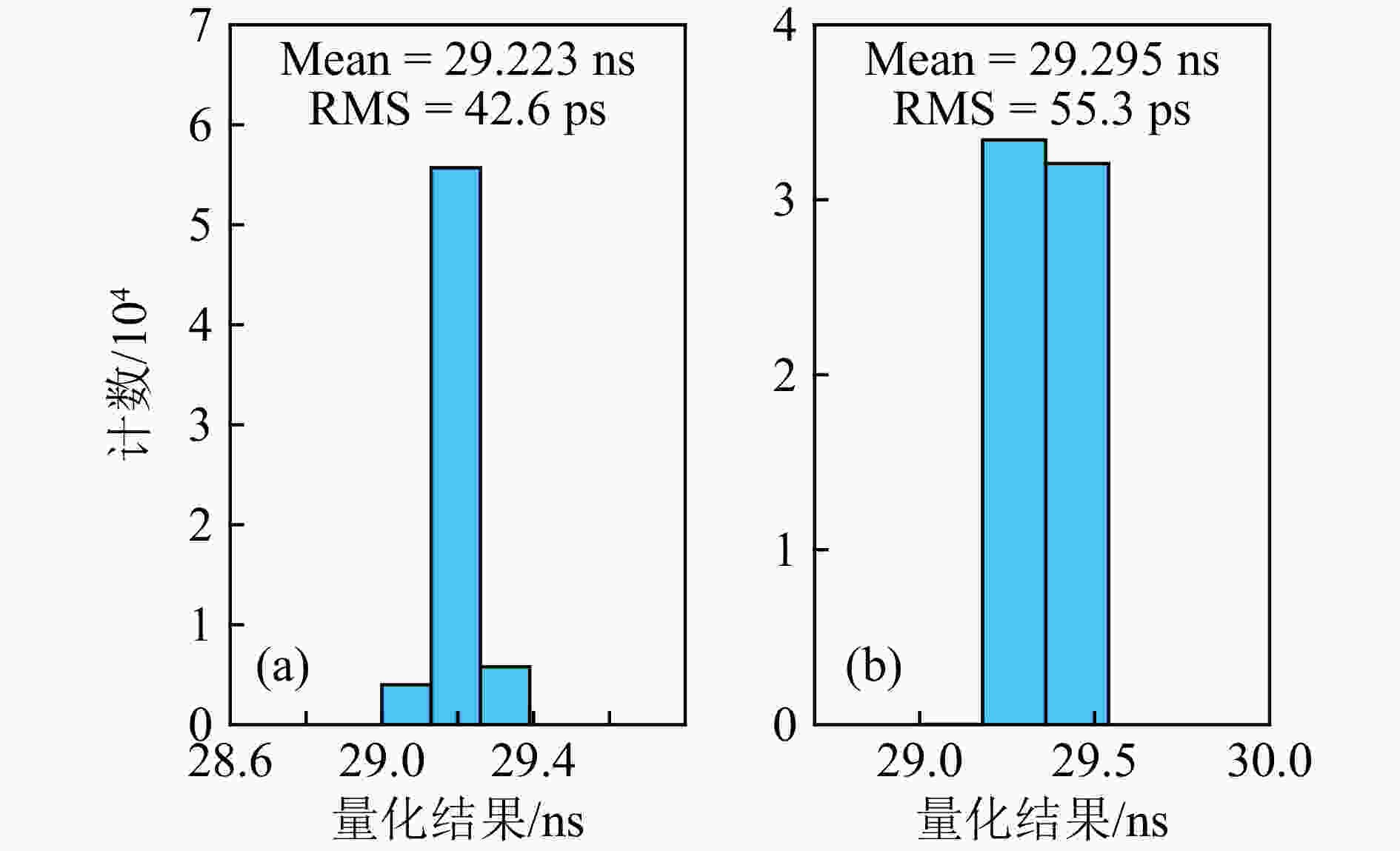

为做更进一步分析,图10所示为图9测试精度曲线中的两个极值点的测量结果分布柱状图。可以看到,图10(a)对应于待测时间间隔为图9约0 LSB时的测量结果分布图,其量化RMS精度为42.6 ps。该测量结果存在三个码值,分别对应于–1、0、l LSB,对应于两次采样分别出现亚稳态的情况。图10(b)则对应于图9约0.5 LSB时的待测时间间隔测量结果分布图,其量化RMS精度为55.3 ps,测量结果只存在两种码值的情况,与理论相符合。

-

结合上述测试,进一步对TDC整体时间转换性能进行了测试,以较大的时间间隔步长扫描了TDC的测量动态范围。结合测量码值分布分析,芯片动态范围达20 μs。图11即为相应的TDC全量程时间转换性能曲线。

-

另外还对芯片功耗进行了评估,方法是将ASIC测试模块上供电系统磁珠更换为小电阻,通过测量两端压降可以得到流过电流,从而评估对应部分的功耗。芯片功耗主要包括模拟部分供电及数字部分供电,结合ASIC设计时的事例率考虑,分别评估了无事例触发、1 MHz事例率和2 MHz事例率情况下的通道功耗,测试结果如表1所列。

表 1 ASIC不同工作状态下单通道功耗表

事例率 模拟部分/mW 数字部分/mW 总功耗/mW 无事例 2.25 5.14 7.39 1 MHz事例率 2.25 5.32 7.57 2 MHz事例率 2.25 5.50 7.75 可以看到芯片通道功耗低于8 mW,在不同事例率情况下数字部分功耗略有不同,这是由部分时钟树及接口处翻转率有所变化所导致的。

最后为了评估芯片的系统死时间,通过调节信号源输出的周期信号间隔,测量了通道所能达到的最大事例率。测试结果表明通道最大平均事例率约为2.5 MHz,对应系统死时间即为0.4 μs。综合测试结果表明,该原型芯片具有较好的工作性能,符合设计预期。

-

本论文介绍了实验室设计完成的基于DLL结构的TDC ASIC,设计在180 nm CMOS工艺上实现。为了完成芯片性能的相关测试,设计了对应的ASIC测试电子学模块,构建了芯片测试系统并完成了测试。测试结果表明,该芯片具有较好的时间精度,在20 μs的动态范围下精度好于60 ps且DNL/INL好于0.13/0.15 LSB。符合设计预期。

-

摘要: TDC(time-to-digital converter)作为基于信号甄别和时间数字转换的时间测量技术路线的主要组成部分之一,至今在诸多领域中都具有广泛的应用。本实验室对高精度时间测量TDC ASIC(Application Specific Integrated Circuit)进行了深入研究,在180 nm CMOS工艺下完成了基于DLL(Delay-Locked Loop)结构的原型芯片的设计,芯片命名为DHR TDC。为了评估原型芯片的相关性能以推进下一步的改版设计,设计了测试电子学模块,构建了相应的电子学测试系统并完成了性能测试。测试结果表明,该TDC具有较好的性能,在实现156 ps的bin size基础上时间精度好于60 ps RMS。同时该TDC在20 µs的动态范围下具有较好的线性,其DNL(Differential NonLinearity)和INL(Integral NonLinearity)分别好于0.13和0.15 LSB (Least Significant Bit)。Abstract: As one of the key components in high precision time measurement based on discrimination and time digitization, the time-to-digital converter(TDC) is widely used in many fields. This paper presents the design and testing of a DLL based TDC prototype ASIC named DHR TDC with a large detectable range and high resolution in 180 nm CMOS technology. A test module was designed and the test platform was set up for the TDC performance evaluation. Test results indicate that this TDC achieves a time resolution of better than 60 ps RMS with an averaged bin size of around 156 ps, as well as a measurement dynamic range of up to 20 µs, and its differential nonlinearity(DNL) and integral nonlinearity(INL) are better than 0.13 LSB and 0.15 LSB, respectively.

-

Key words:

- TDC /

- ASIC /

- high-precision time measurement /

- ASIC test

-

表 1 ASIC不同工作状态下单通道功耗表

事例率 模拟部分/mW 数字部分/mW 总功耗/mW 无事例 2.25 5.14 7.39 1 MHz事例率 2.25 5.32 7.57 2 MHz事例率 2.25 5.50 7.75 -

[1] 安琪. 核技术, 2006(06): 453. AN Qi. Nuclear Techniques, 2006(06): 453. (in Chinese) [2] CHENG Z, ZHENG X, DEEN M J, et al. IEEE Transactions on Electron Devices, 2015, 63(1): 235. doi: 10.1109/TED.2015.2503718 [3] 梁宇. ATLAS MDT二期升级前端电子学中的TDC ASIC研究[D]. 合肥: 中国科学技术大学, 2019. LIANG Yu. Research of TDC ASIC for Front End Electronics in ATLAS MDT Phase II Upgrade[D]. Hefei: University of Science and Technology of China, 2019. (in Chinese) [4] WANG J, LIANG Y, XIAO X, et al. Nucl Instr and Meth A, 2018, 880: 174. doi: 10.1016/j.nima.2017.10.077 [5] FENG C, LIU S, AN Q. IEEE Transactions on Nuclear Science, 2010, 57(2): 463. doi: 10.1109/TNS.2009.2034658 [6] WANG B, LIU Y H, HARPE P, et al. A Digital to Time Converter with Fully Digital Calibration Scheme for Ultra-low Power ADPLL in 40 nm CMOS[C]//2015 IEEE International Symposium on Circuits and Systems (ISCAS). IEEE, 2015: 2289. [7] WAHEED K, STASZEWSKI R B, DULGER F, et al. IEEE Transactions on Circuits and Systems I:Regular Papers, 2011, 58(9): 2051. doi: 10.1109/TCSI.2011.2163981 [8] 邓佩佩. 小动物 PET 单事件处理电子学的研究[D]. 合肥: 中国科学技术大学, 2018. DENG Peipei. Research of singles Processing Electronics for the Small Animal PET [D]. Hefei: University of Science and Technology of China, 2018. (in Chinese) [9] HUF CAMPOS B L, GASPARINI L, GRANT L, et al. IEEE Journal of Solid-State Circuits, 2014, 49(1): 301. doi: 10.1109/JSSC.2013.2284351 [10] VYHLIDAL D, CECH M. IEEE Transactions on Instrumentation and Measurement, 2015, 65(2): 328. [11] CHEN P, WANG K M, LI C Y, et al. CMOS Time-to-digital Converter with Low PVT Sensitivity 20.8 ps Resolution and− 0.25~0.22 LSB Inaccuracy[C]//2011 IEEE International Conference on Anti-Counterfeiting, Security and Identification. IEEE, 2011: 127. [12] MACHADO R, ALVES F S, GERALDES Á, et al. IEEE Access, 2020, 8: 195820. doi: 10.1109/ACCESS.2020.3034522 [13] HEJAZI A, OH S J, REHMAN M R U, et al. IEEE Transactions on Instrumentation and Measurement, 2020, 69(11): 9262. doi: 10.1109/TIM.2020.2995249 [14] STRAAYER M Z, PERROTT M H. IEEE Journal of Solid-State Circuits, 2009, 44(4): 1089. doi: 10.1109/JSSC.2009.2014709 [15] YE C, ZHAO L, ZHOU Z, et al. Review of Scientific Instruments, 2014, 85(4): 045115. doi: 10.1063/1.4870922 [16] HENZLER S. Time-to-Digital Converters[M]. New York: Springer Science & Business Media, 2010: 43. [17] DEPPE H, FLEMMING H. The GSI Event-driven TDC with 4 channels GET4[C]//2009 IEEE Nuclear Science Symposium Conference Record (NSS/MIC). IEEE, 2009: 295. [18] MARKOVIC B, TISA S, VILLA F A, et al. IEEE Transactions on Circuits and Systems I:Regular Papers, 2013, 60(3): 557. doi: 10.1109/TCSI.2012.2215737 [19] MARINO N, BARONTI F, FANUCCI L, et al. IEEE Transactions on Nuclear Science, 2015, 62(3): 814. doi: 10.1109/TNS.2015.2403291 [20] ZHAO L, MA C, CHU S, et al. IEEE Transactions on Nuclear Science, 2017, 64(6): 1367. doi: 10.1109/TNS.2017.2693296 [21] KANG L, ZHAO L, ZHOU J, et al. Metrology and Measurement Systems, 2013, 20(2). [22] DOERNBERG J, LEE H S, HODGES D A. IEEE Journal of Solid-state circuits, 1984, 19(6): 820. doi: 10.1109/JSSC.1984.1052232 [23] CHEN H, QIN J, ZHAO L, et al. Testing of SCA Waveform Digitization ASIC for High-precision Time Measurement[C]//2020 6th International Conference on Event-based Control, Communication, and Signal Processing (EBCCSP). IEEE, 2020: 1. [24] MEHROTRA A. Noise in Radio Frequency Circuits: Analysis and Design Implications[C]//Proceedings of the IEEE 2001. 2nd International Symposium on Quality Electronic Design. IEEE, 2001: 469. [25] KALISZ J. Metrologia, 2003, 41(1): 17. -

下载:

下载:

甘公网安备 62010202000723号

甘公网安备 62010202000723号