-

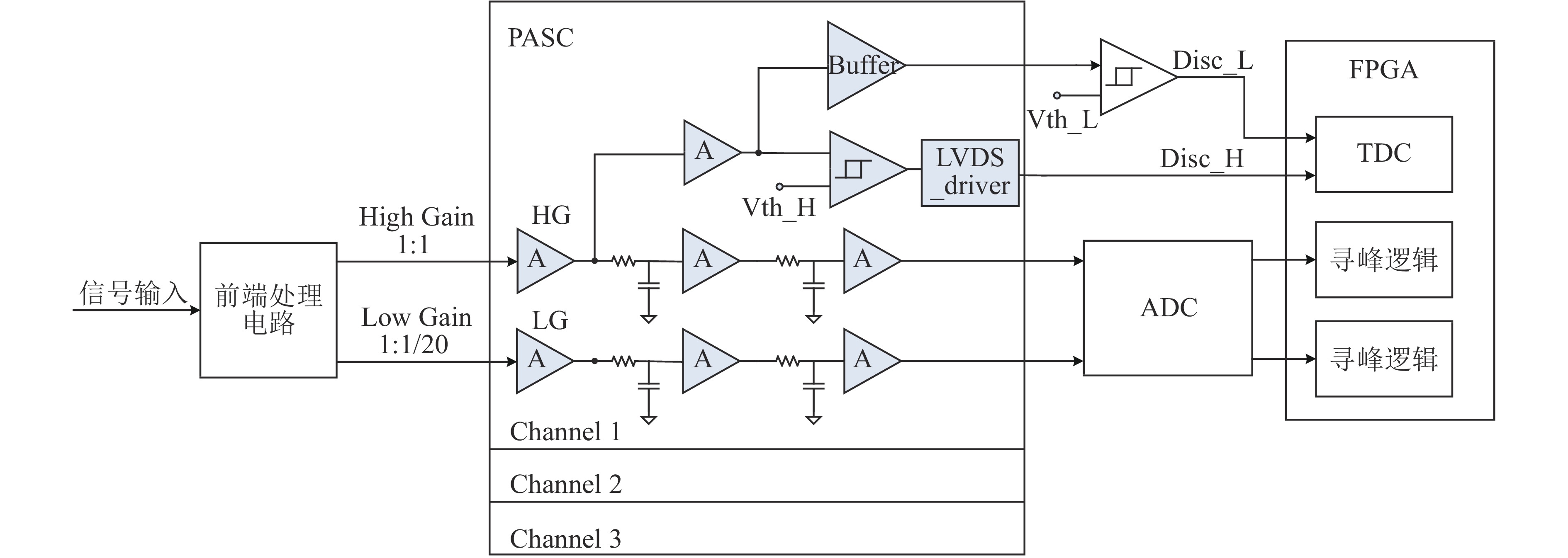

大型高海拔空气簇射观测站(Large High Altitude Air Shower Observatory,LHAASO)是“国家发改委十二五规划”中计划建设的大型γ粒子巡天扫描探测系统,其中水契伦科夫探测器阵列(Water Cherenkov Detector Array,WCDA)是主要探测器系统之一[1-2]。WCDA使用光电倍增管(PhotoMultiplier Tube,PMT)接收契伦科夫光,然后将接收到的信号进行光电转换并输出。为了对PMT的输出信号进行采集和处理,我们设计了与其配套的读出电子学系统,并通过该系统将测量结果(其中包括电荷信息和时间信息)传输到PC端的数据获取系统(Data Acquisition System,DAQ)中[3-5]。针对大动态范围下高精度电荷和时间测量的要求,本实验室自主研发了PASC(Pre-Amplifier and Shaping Circuit) ASIC(Application Specific Integrated Circuit),并结合WCDA采用国产新型20”MCP(Micro Channel Plate,微通道板)PMT的新方案进行了优化设计。该芯片的制作工艺为0.35 μm CMOS,其内部集成电荷成形、放大和时间前沿甄别功能。在实际应用中结合整个电子学系统将PMT的输出信号调理为准高斯信号,然后利用芯片后端的ADC和FPGA完成电荷和时间测量。

为了确保PASC ASIC的设计工作顺利进行,需要设计一套用于芯片验证与测试的批量测试系统。系统化的测试在集成电路的研制中占重要地位,尤其在工程项目中芯片的批量制造阶段,必须配套大批量芯片测试的高精度和高可靠性的自动化测试系统。由于PASC ASIC的复杂性和高性能指标特点,设计一套高质量的测试系统具有其必要性。出于此目的,以PASC ASIC为研究对象,设计出用于此芯片的自动化测试系统,从而简化测试流程,提高测试效率。这对批量芯片性能筛选以用于工程项目有着重要的意义。

-

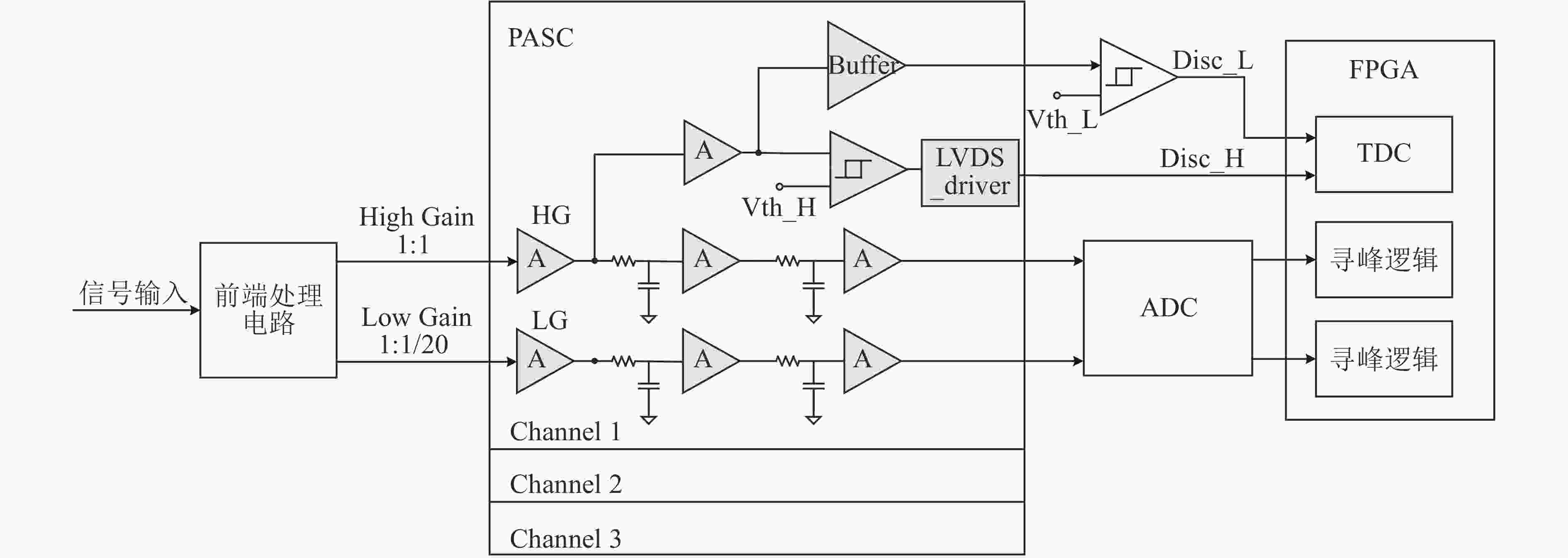

PASC芯片内部集成了放大、成形和时间甄别等模拟调理电路。每片PASC包含三个高增益(High Gain,HG)通道和三个低增益(Low Gain,LG)通道,HG和LG电路结构基本相同而放大倍数不同,结合前端处理电路可实现20倍的增益关系。

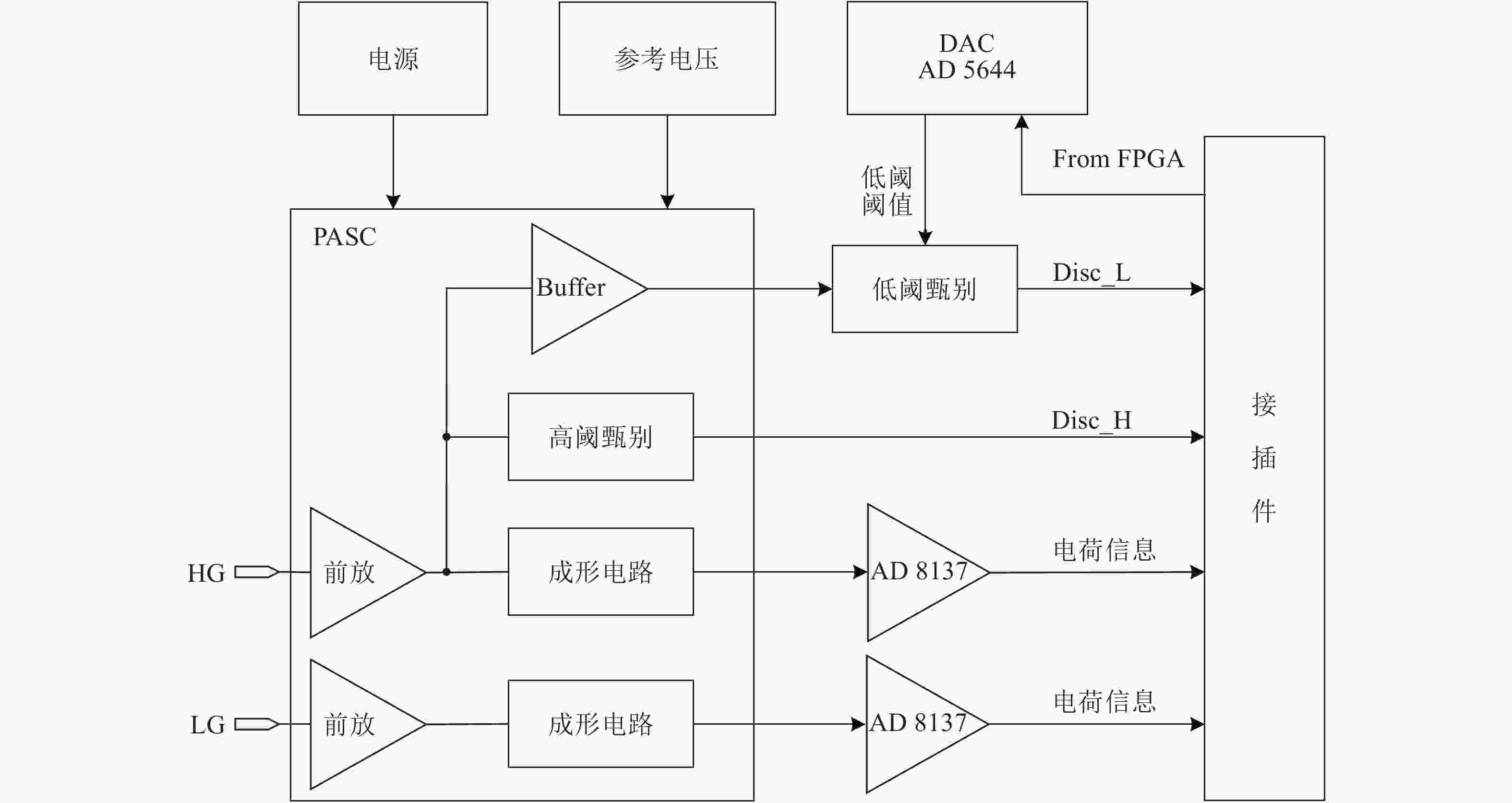

HG通道经过前放扇出为两路,一路进行前沿定时,另一路送入滤波器进行信号成形,LG通道与HG通道类似,但只负责信号的放大成形,将PMT输出的电信号成形为准高斯信号(幅度正比于信号的电荷量)。内部电路由前放、两级RC和隔离运放组成,时间甄别电路还包括甄别器和DAC,运放的增益和RC常数都能通过开关选择。PASC芯片目前已经完成了多个阶段原理样片的设计和批量制作,即将用于LHAASO WCDA第三水池的工程中。图1为基于PASC ASIC的前端读出方案,PASC的定时甄别输出直接送入FPGA-TDC进行时间数字化,电荷成形输出通过ADC波形数字化后送入FPGA进行寻峰计算。

-

本测试系统目标为针对PASC ASIC进行系统化的性能测试,以准确评估该芯片时间和电荷测量相关指标,保证PASC能适用于LHAASO WCDA的读出中。此芯片应用指标需求参数具体如表1所列。

表 1 芯片应用指标需求

项目 指标需求 动态范围 S.P.E.(Single Photoelectron)~ 2 000 P.E.(S.P.E.

约4 mV)电荷分辨精度 <30% @S.P.E., 3%@2 000 P.E. 时间分辨精度 <500 ps RMS -

电荷测量过程需对待测信号的电荷量进行计算并给出电荷测量精度。此过程需要PASC ASIC内部进行滤波成形,并结合PASC外部的ADC电路以及FPGA数字寻峰逻辑完成[6]。对同一电荷量下进行多次测量,其电荷测量结果的RMS值可定义为电荷测量精度,该指标是评估PASC ASIC性能的关键指标。通过示波器虽然可以获取成形后的准高斯波形,但受限于示波器本身的量程和分辨精度,在小信号下无法进行精确的电荷精度测试,因此本论文所设计的测试系统有必要对电荷量进行精确测量。此外我们还需要考虑将芯片和电子学后续电路相结合用于评估整个电子学系统的电荷精度,因此电荷测量方案我们选取了兼容系统读出电子学的整体技术路线[7],即结合FPGA数字寻峰技术。该技术首先采用PASC芯片内电荷成形电路将较快速的PMT输出信号调理成较慢的准高斯信号,其波形的峰值与面积成正比,然后通过中高速ADC芯片将波形进行模数转换,最后将得到的数字化信号输入FPGA计算峰值,峰值即可代表电荷量。通过MATLAB进一步统计和分析计算,得到电荷精度的RMS值,反推出系统的电荷测量精度。

-

对于时间测量,则要获取信号到达的时间信息并计算时间测量精度。芯片内部集成了放大、时间甄别电路,PMT输出的模拟信号经过芯片内时间甄别电路后转换为一个数字脉冲,数字脉冲的上升沿即为信号的到达时间。甄别后的信号直接送入测试电路的FPGA中,利用FPGA内部TDC进行时间数字转换,即可得到此芯片用于实际电子学系统的相关指标。在实际测试过程中,仅在需要时使用高速示波器直接观察甄别器输出的数字脉冲信号来判断芯片功能是否正确,性能测试则使用FPGA-TDC进行数字化。基于时钟分相原理的FPGA-TDC占用资源较少且较易于实现,适用于多通道集成。为了扩大TDC的动态范围,同时为了保证较高测量精度,利用粗细结合测量的思想,将16 ns的时钟周期细分为48份,时间测量分辨率可达333 ps,满足应用需求[8]。另外在测试系统连接上,通过延时线法来消除信号源本身的晃动对测量结果的影响,通过功分器提供同步输入信号,计算相邻两通道间时间延迟差的RMS值,反推出系统的时间测量精度。

-

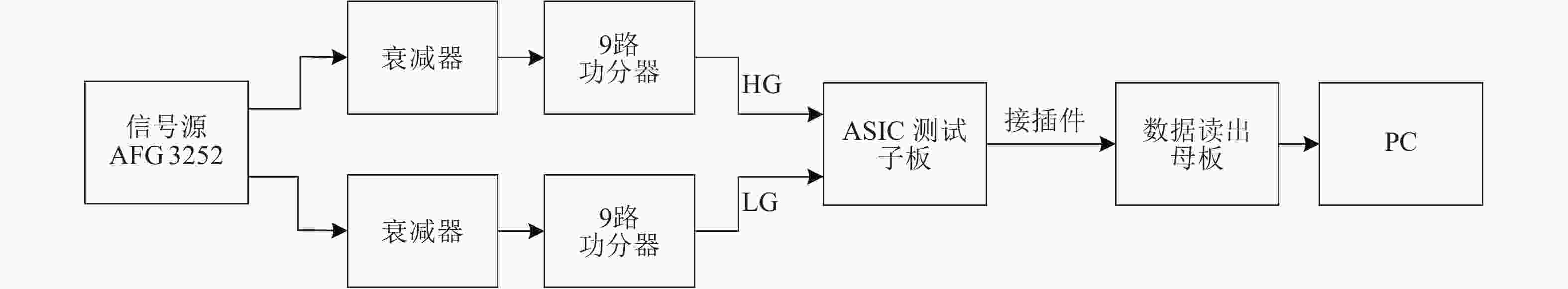

通过上述测试要求的分析和基本方案的讨论,我们构建了如图2所示的测试系统。在测试过程中先使用示波器(WavePro715Zi, LeCroy公司)抓取PMT信号的波形并转换成数据点文件,然后通过ArbExpress软件将数据点文件绘制成波形图后存入任意波形发生器(AFG3252,Tektronix公司)作为测试波形。由于信号源最小只能产生50 mV的信号,所以在测试中将AFG3252输出电压幅值固定在最大输出幅度(5 V),然后使用有源衰减器(RF Step Attenuator,ROHDE& SCHWARZ公司)进行衰减得到不同幅度的信号,既保证了测试中可以测试不同幅度下的性能指标,同时又能保证输入信号的信噪比。此外,考虑到多片ASIC并行测试的方案,信号源产生的两路信号经过衰减器再分别通过两个9路功分器直接接入ASIC测试子板上的PASC输入端,两路信号分别对应HG和LG,该方案可同时进行三片芯片9个通道的测试。在硬件电路结构上,设计成比较灵活的子母板形式,每个子板上放置一片ASIC,一块母板对应三块子板,通过接插件相连接,最后将数据读出母板处理得到的相应数据结果输出到PC端。

-

ASIC测试子板主要包括PASC芯片以及相应的电源电路、参考电源电路、DAC配置电路、时间甄别电路等,ASIC测试子板接收信号并将芯片输出通过接插件传输至后端母板。

如上所述,一块子板对应一片PASC芯片,包含3个HG通道和3个LG通道。由于HG与LG之前的增益相差20倍,结合设计指标所要求的1~2 000 P.E.的电荷测量动态范围,则可由HG通道完成前沿定时和1~100 P.E.范围的电荷测量,LG通道完成20~2 000 P.E.范围内的电荷测量。PMT输出信号经过两级RC滤波成形和电压放大后,输出到片外的差分运放(型号AD8137),将单端信号转为差分信号,并通过接插件给到后端母板。时间通道分高低阈甄别,对于小信号,需设置较低阈值以保证其可以过阈甄别,而大信号前沿靠近基线处的扰动和噪声可能会引起过阈翻转误触发,为此对于大信号测量还需引入高阈进行甄别,故采用双阈值甄别方式。小信号以1/3 P.E.为甄别阈值,大信号以5 P.E.为甄别阈值。高阈甄别电路集成在PASC芯片内部,甄别结果直接通过内部LVDS驱动输出到接插件,低阈甄别则放在了片外,主要原因是ASIC只有+3.3 V单边供电,相比于商用放大器和甄别器(+/– 3.3 V供电)所允许的信号摆幅都要低,而探测器输出信号波形后沿存在过冲,会更易被放大至饱和从而导致更长的恢复时间,此时若大信号后沿上存在单光子信号,则此单光子信号将无法甄别,等效增加了甄别电路的死时间。片外每个通道对应一个低阈甄别器,由DAC(型号AD5644)配置片外甄别器的甄别阈值。

图3是前端ASIC测试子板结构示意图,时间测量通道和HG的电荷测量通道在芯片内共用前放,之后时间通道扇出两路,一路经过驱动buffer输出至片外作低阈甄别,另一路经过交流耦合后作高阈甄别,甄别后的信号经过片内LVDS驱动器输出至片外。

-

数字读出母板则主要包括FPGA、ADC模数转换电路、电源电路、DDR缓存电路、传感器电路、时钟与数据接口电路等,具体结构框图如图4所示,每块母板对应三块子板,通过接插件相连,子板的电源由母板提供,子板的输出则通过接插件传递给母板。子板电荷成形通道的输出直接输入至母板上的ADC进行采样,配合数字寻峰逻辑实现电荷测量;时间甄别的定时信号输入至FPGA-TDC实现时间测量,同时此定时信号也作为触发信号用以并启动寻峰逻辑。数字信号处理母板的结构框图如图4所示。

由于子板输出的信号已通过差分放大器将单端信号转换为差分信号,故母板上的ADC选用差分输入的AD9222,此ADC为8通道,12 bits,Pipeline ADC,一片ADC对应一块子板,可对三个HG和三个LG一共6个通道进行采样。ADC采样时钟由PLL(型号AD9522)产生,频率为62.5 MHz。另一方面,FPGA输出的时钟jitter较大,也需要PLL对其进行去抖[9]。

当子板信号到来时,首先将高低阈甄别器产生脉冲输入到FPGA-TDC进行时间测量,同时将甄别信号作为FPGA寻峰逻辑的启动信号用来启动数字寻峰逻辑,在甄别信号到来后的一定时间窗口内依次比较ADC的输出码值,保留峰值结果;并以甄别信号到来前8个时钟周期的ADC采样点的平均值作为基线,再将峰值与基线相减得到电荷量测量值。对于同一个事例,高低阈甄别器产生的脉冲上升沿相差较小,为节省数据带宽,可对TDC值进行合并处理,将粗时间计数合并,只保留细计数,并加入2 bit的跨时钟周期信息,以此减小数据位宽。将合并后的时间信息与电荷信息组装为128 bits的数据包,进入DDR3缓存逻辑。缓存逻辑可将数据缓存到外部DDR3芯片中以增大存储深度,等待数据传输接口(SiTCP模块)进行TCP/IP打包并传输,经FPGA内的高速串行收发器(GTP)转化为串行数据流发送到上位机。此外,为监控测试板工作状态,测试板还设计了温度和湿度传感器模块。

-

ASIC的测试内容为在信号源模拟的PMT信号下获得由电子学输出的二进制数据文件,并利用如前文所述获得电荷信息和时间信息的算法从数据文件中得到电荷和时间结果。在测试操作上,每一次测试都包含大量重复性的人工操作,每个测试点都需要调节衰减器的衰减值来对应一种输入电荷量,且测试过程中还需改变几次信号发生器的波形形状。为提高测试效率,需配套一个自动化流程的测试软件,所有重复性的人工操作可通过软件控制自动执行。

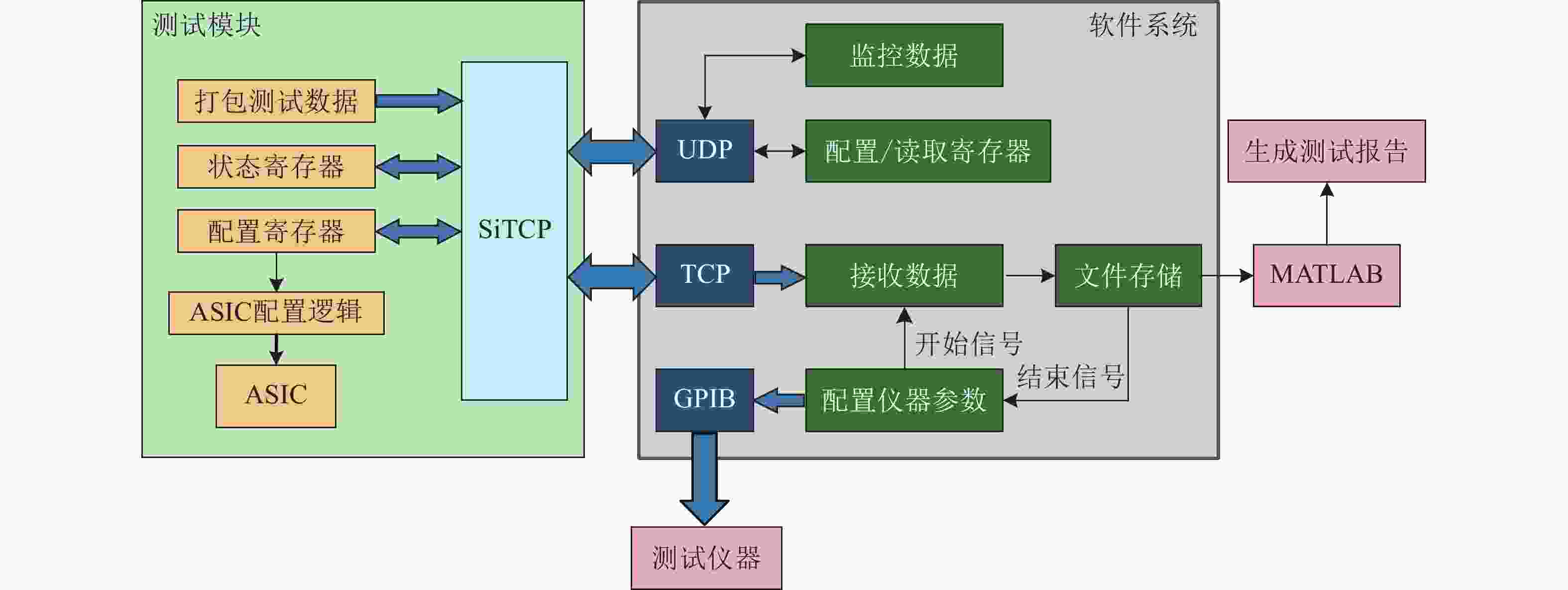

该软件基于Window MFC库,主要在Microsoft Visual Studio环境下使用C++语言开发。它具有仪器程控、数据采集、数据分析、命令控制、状态监视等功能,可以满足LHAASO WCDA电子学前端ASIC测试的要求。软件系统整体框图如图5所示。

测试软件系统基于TCP/IP协议与测试板建立网络连接,接收并分析从FPGA传输来的数据。在测试过程中,首先需要配置ASIC中每个通道的初始化参数,例如时间测量阈值和DAC参数等。在用户界面中调用配置按钮时,软件将同时创建一个数据报套接字,基于UDP协议发送配置数据,并接受来自FPGA的反馈ACK数据包。而仪器的程控则通过通用接口总线(General-Purpose Interface Bus,GPIB)控制卡连接到计算机上,通过GPIB电缆来实现计算机与多台程控仪器的信号传输[10],以VISA(Virtual Instrument Software Architecture)通讯形式通过GPIB编程指令控制信号发生器和衰减器,使用多线程同步来自动控制仪器参数配置、接收数据和文件存储等有序步骤。此外,软件系统应定期读取测试板的状态寄存器,并根据读取结果监视测试板的当前工作状态。

关于数据分析部分,考虑到软件运行的稳定性,软件接收并保存的数据通过MATLAB进行处理,使用MATLAB中的分析程序完成电荷精度和时间精度的计算,并自动生成与芯片编号一一对应的测试报告。

-

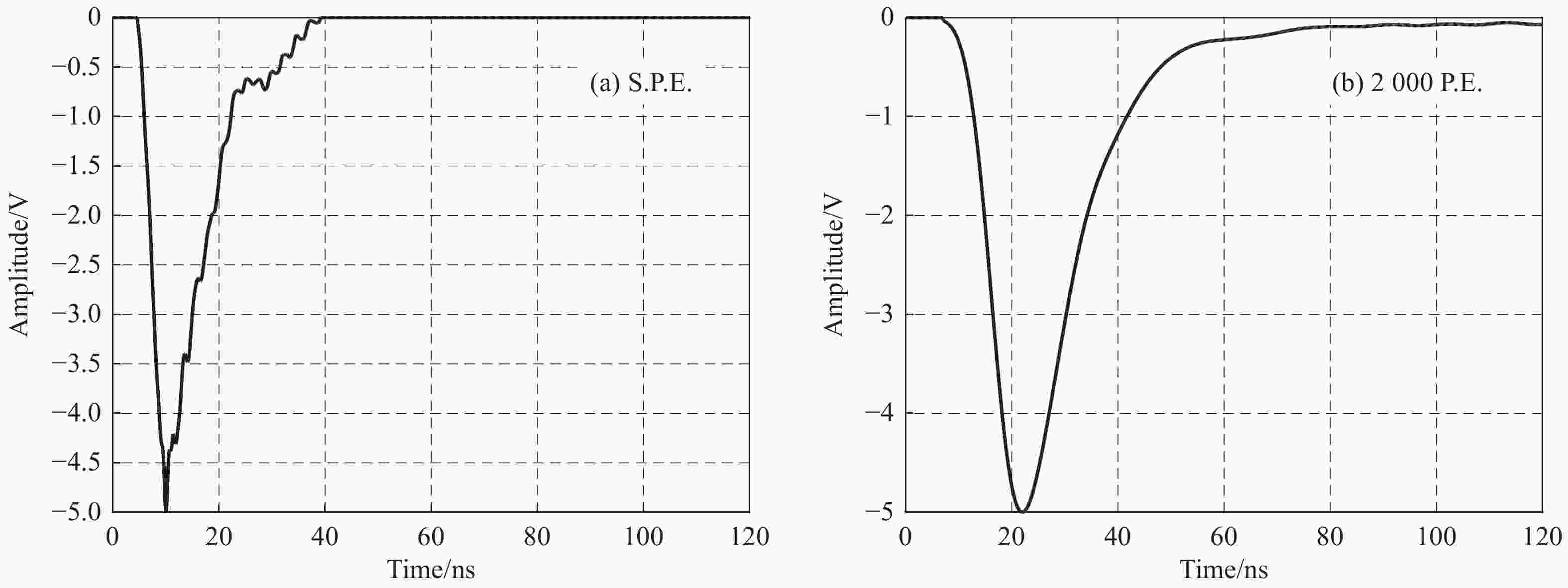

基于上述介绍的测试平台,我们对芯片进行了批量测试,测试数据覆盖如下测试点。对于HG得到经过功分后的信号对应的一系列等效光电子数下的波形:S.P.E, 5, 10, 20, 50, 70, 100 P.E.。对于LG,得到一系列等效光电子数下波形:20, 200, 400, 1 000, 1 400, 2 000 P.E.。以上电荷点可通过前文所述软件结合仪器硬件连接实现自动的增益调节,在每个电荷点下ASIC子板接收信号并将芯片输出通过接插件传输至母板中,母板处理后的数据送入电脑中通过MATLAB进行处理。为保证信号的信噪比,信号源输出幅度固定为5 V,其使用的单光电子波形和2 000 P.E.波形形状如图6所示。

-

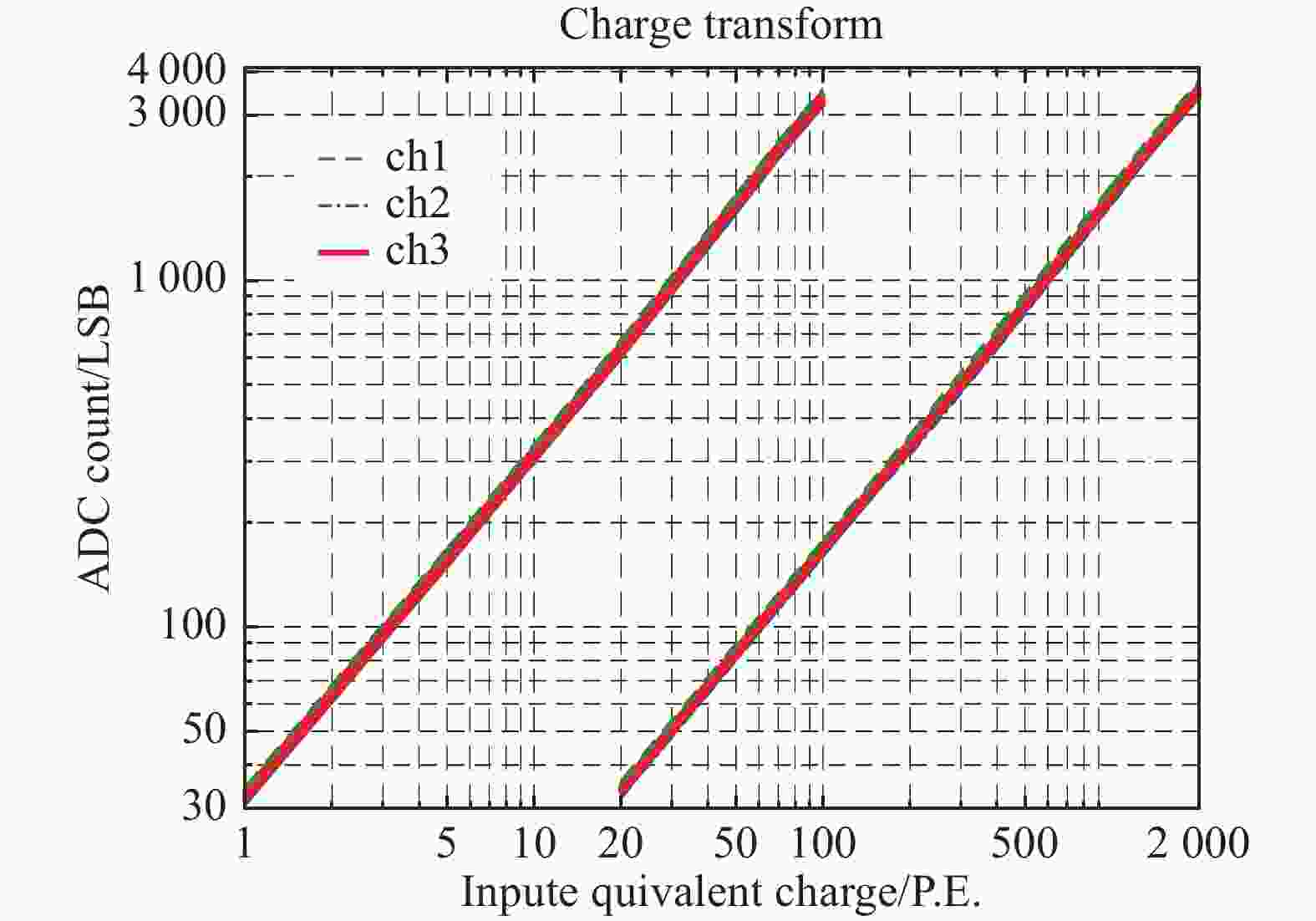

首先用信号源输出模拟的PMT信号,然后通过调整衰减器的衰减值获得与不同光电子数(即不同幅度)相对应的测试信号。测试信号首先经PASC芯片处理后利用ADC数字化,再通过FPGA进行寻峰计算得到不同输入信号的峰值平均值,进而得到待测芯片3个通道的光电子数-ADC码值的转换曲线。第一批共测试了100片芯片,剩下的芯片按相同测试模式测试即可,以下以100片芯片的测试结果为例,其结果如图7所示,3个通道的数据分别用3种颜色标出。

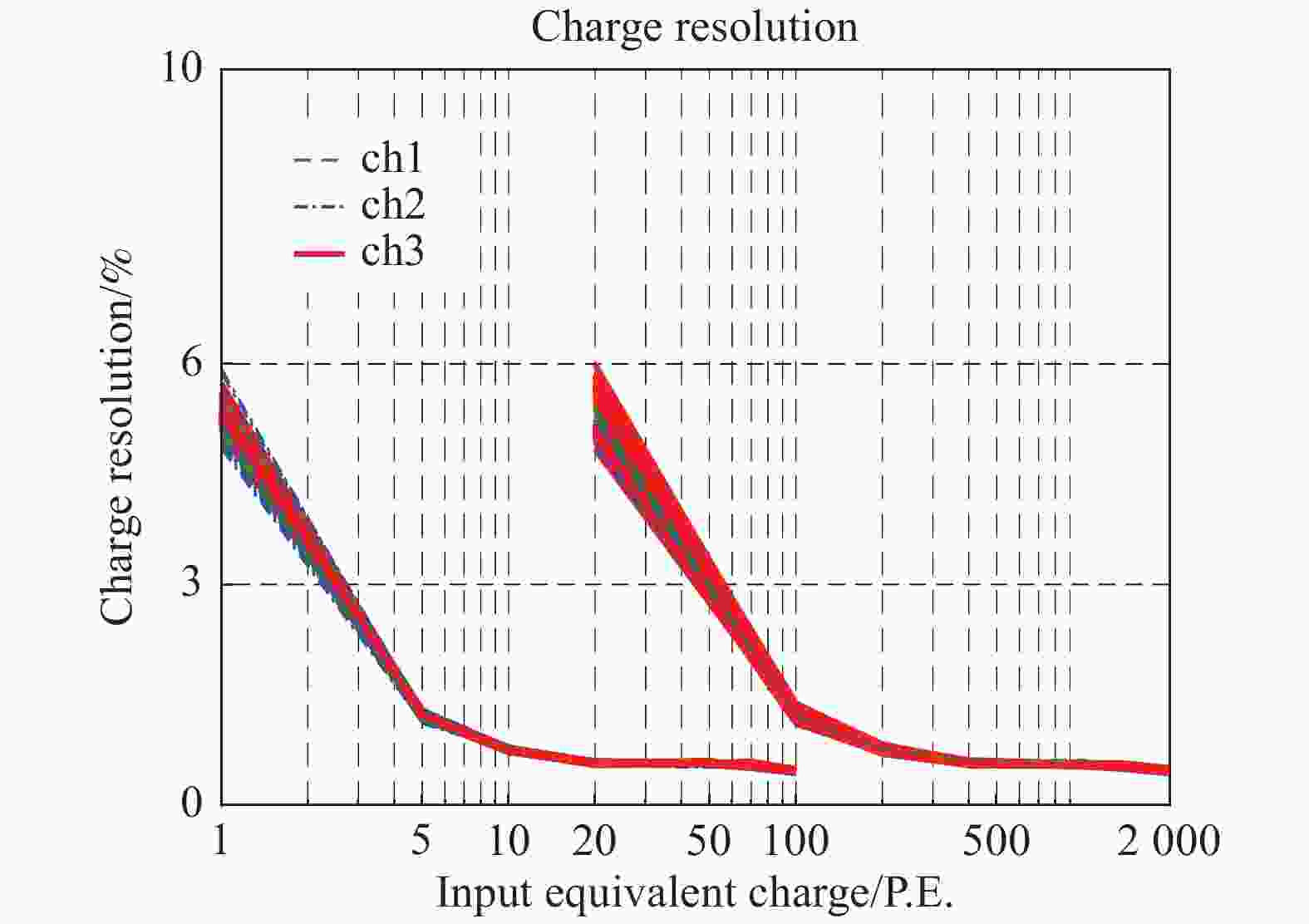

根据对不同幅度点对应的数字寻峰结果的统计可知,每个幅度点下数字寻峰的ADC道数呈高斯分布。计算每个幅度点下的ADC码值的RMS值与ADC码值的平均值之比,此比值可以用来衡量电荷测量电路的精度性能,测量的结果如图8所示。测试结果表明,单光子电荷分辨率在10%以内,2 000 P.E.电荷分辨率在1%以内,满足工程应用需求。

-

时间性能的测试基于延时线法,将信号源的一路输出经过功分器分为多路,通过测量相邻两路信号间时间差的晃动推算时间测量精度,以消除信号源输出信号本身晃动的影响。

通过改变波形和调节衰减器衰减值,将各个电荷量下的等效信号输入ASIC。基于MATLAB分析得到时间测量结果,计算相邻两通道对于信号源产生的同一个信号的时间测量结果的差值,并分析其标准差再除以21/2,以此结果作为时间测量精度。时间精度测试曲线如图9,在整个测量区间内的时间精度RMS好于200 ps,满足应用需求。

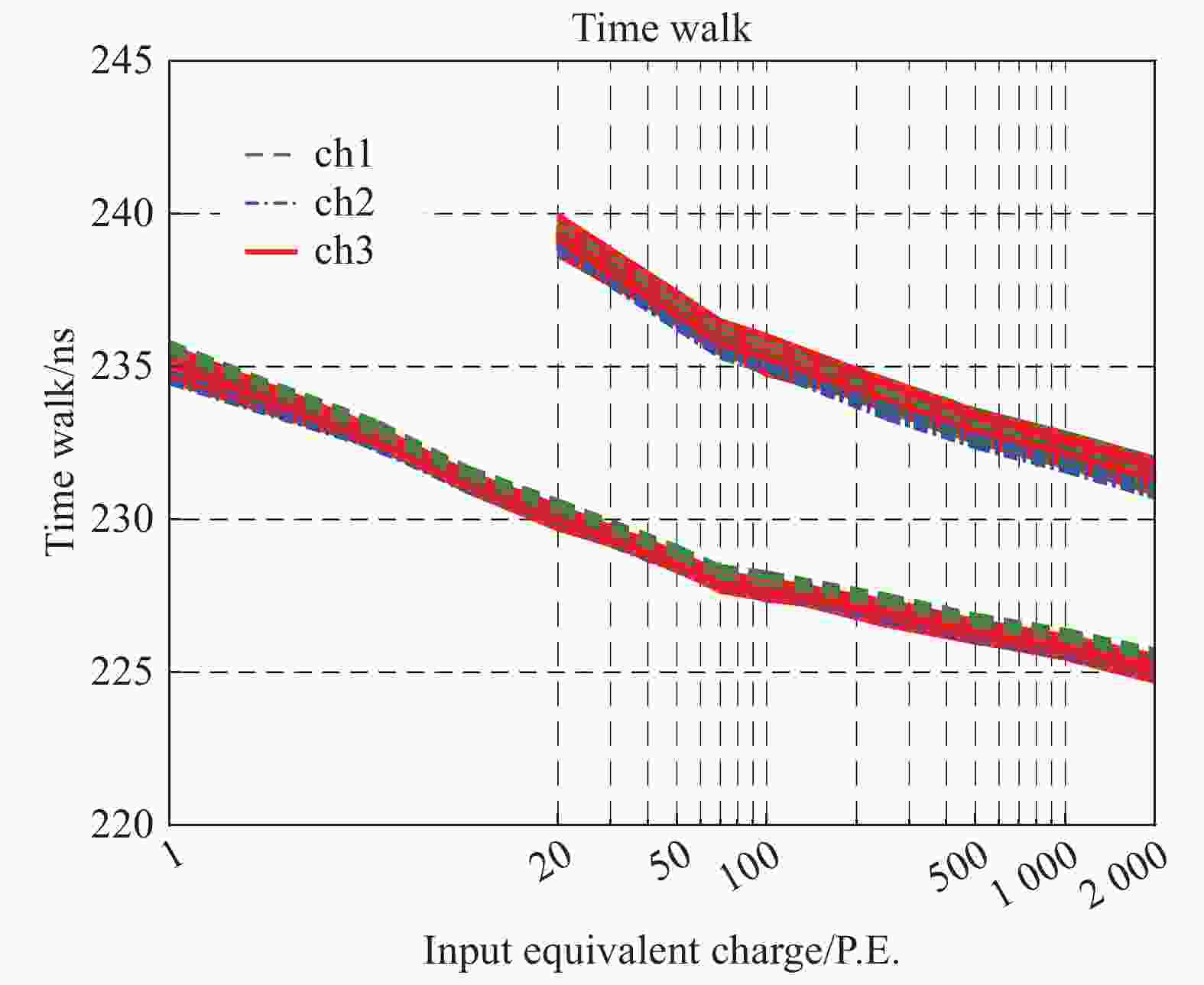

另外,由于时间测量采用前沿定时,对于同一时刻到达的信号,其过阈甄别时间会随信号幅度增大而提前,产生Time Walk效应。通过信号源另一通道输入与测试信号同步的基准方波脉冲到FPGA-TDC作为参考时间,测量得到的S.P.E.~2 000 P.E.范围内延时与输入信号幅度关系如图10所示,符合预期。在实际工程使用中,时间延迟还与PMT渡越时间、电缆传输等有关,需结合PMT进行标定。

-

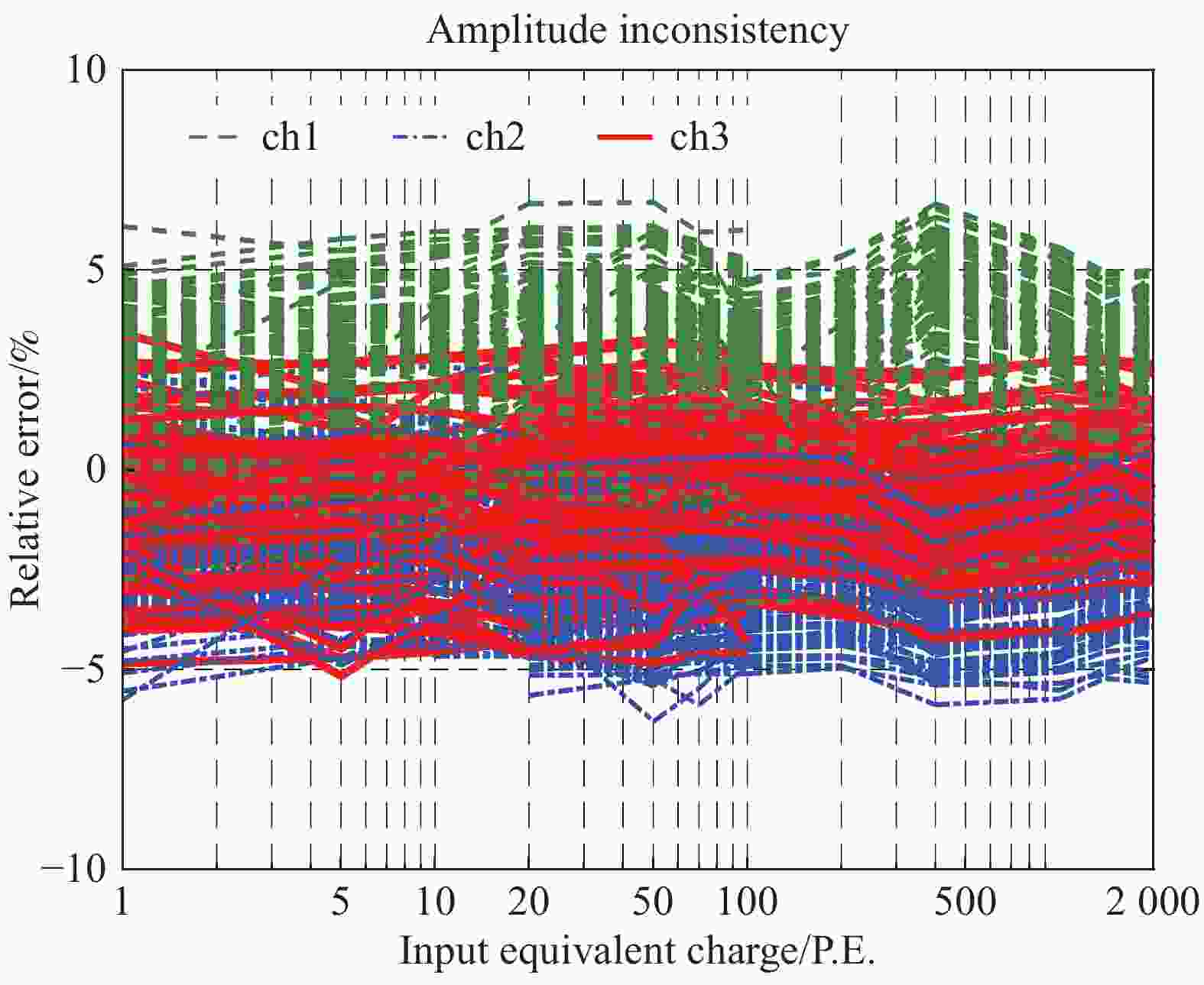

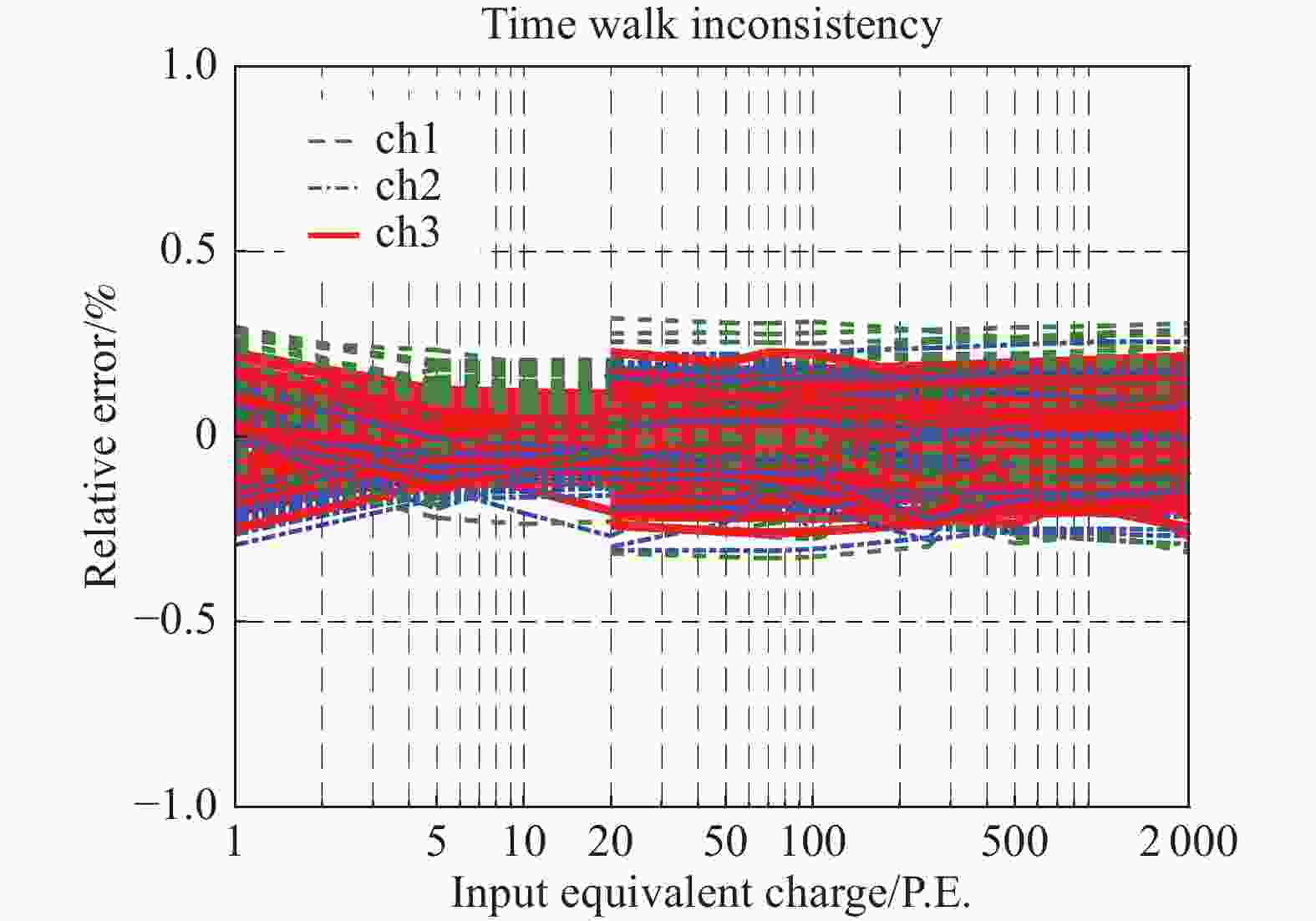

以100片芯片每个通道不同幅度下的数据与其平均值作相对误差,可得出电荷幅度不一致性与Time Walk不一致性的结果。

如图11和图12中结果所示,电荷幅度不一致性的相对误差分布在±7%以内,Time Walk不一致性的相对误差分布在±0.5%以内,通道间不一致性较小。并且,在实际应用时,电子学会结合探测器进行整体标定并修正,此不一致性会被扣除,所以上述不一致性偏差没有太大影响。

-

针对国家发改委十二五规划LHAASO项目中WCDA的读出,实验室自主研发了一款大动态范围前端读出ASIC。为了满足此芯片的测试需求设计了自动化测试系统,上述测试系统已实际投入使用,并进行了批量芯片的测试。通过对第一批100片PASC ASIC的测试,验证了芯片各项参数性能已达标,且证明了此自动化测试系统的可行性,能够达到测试要求和目标。

-

摘要: LHAASO(Large High Altitude Air Shower Observatory)WCDA(Water Cerenkov Detector Array)要求其读出电子学实现大动态范围下精确的时间和电荷测量,为此设计了一款前端读出芯片PASC(Pre-Amplifier and Shaping Circuit) ASIC(Application Specific Integrated Circuit),即将用于LHAASO WCDA第三水池的读出。为了满足对此芯片大批量测试需求,设计了此ASIC测试系统,实现了对芯片时间和电荷性能的自动化测试。在介绍此芯片基本工作原理的基础上,讨论了测试系统的设计方案和基本结构,包括硬件电路设计和自动化测试软件设计。该测试系统已应用于LHAASO工程项目的芯片筛选并且已完成了100片芯片的测试工作,能够通过中央控制软件,与多台仪器通讯,进行仪器控制,完成自动化测试和数据记录。这一自动化测试方法,更适用于大动态范围下、高精度读出芯片的性能测试和评估,大大简化测试流程,尤其能够大幅提升批量测试中大量重复性测试步骤的工作效率。文中展示了基于此测试系统已完成的100片芯片的测试结果,结果表明,芯片各项性能参数满足LHAASO第三水池工程应用需求。

-

关键词:

- LHAASO WCDA /

- ASIC /

- 自动化测试 /

- 电荷测量 /

- 时间测量

Abstract: In the readout electronics for the Water Cerenkov Detector Array(WCDA) of the Large High Altitude Air Shower Observatory(LHAASO), both high precision time and charge measurement are required. A front-end readout chip PASC(Pre-Amplifier and Shaping Circuit) ASIC(Application Specific Integrated Circuit)is designed, and will be actually applied in the third water pond of the WCDA. In order to evaluate the performance of the chips after massive production, it is important to design an automatic test system. This paper presents the design of the ASIC test system, which is used to achieve automatic testing of the time and charge measurement performance of the chips. After a brief introduction of the chip under test, the design scheme and structure of the test system is presented, including the hardware circuits and test software. This system has been applied in batch test of the LHAASO project, and 100 chips have been successfully tested. It can communicate with multiple instruments through the central control software to perform instrument control and complete automated testing and data recording. This automated test method is more suitable for performance testing and evaluation of high precision readout chips under a large dynamic range, which greatly simplifies the test process and can greatly improve the work efficiency of a large number of repetitive test steps in batch test. The test results show that the performance of these chips meet the application requirements of the third pond of the WCDA in LHAASO.-

Key words:

- LHAASO WCDA /

- ASIC /

- automatic testing /

- charge measurement /

- time measurement

-

表 1 芯片应用指标需求

项目 指标需求 动态范围 S.P.E.(Single Photoelectron)~ 2 000 P.E.(S.P.E.

约4 mV)电荷分辨精度 <30% @S.P.E., 3%@2 000 P.E. 时间分辨精度 <500 ps RMS -

[1] CAO Zhen. Chinese Physics C, 2010, 34(2): 249. doi: 10.1088/1674-1137/34/2/018 [2] HE Huihai. LHAASO Project: Detector Design and Prototype[C]. Proceedings of the 31st ICRC, 2009. [3] CHEN Mingjun, YAO Zhiguo, GAO Bo, et al. R&D of LHAASO-WCDA[C]. Proceedings of the 32nd ICRC, 2011. [4] YAO Z, WU H, CHEN M, et al. Design & Performance of LHAASO-WCDA Experiment[C]. Proceedings of the 32nd ICRC, 2011. [5] ZHAO Lei, LIU Shubin, AN Qi. Chinese Physics C, 2014, 38(1): 016101-1. doi: 10.1088/1674-1137/38/1/016101 [6] ZHAO Lei, MA Cong, CHU Shaoping, et al. IEEE Transactions on Nuclear Science, 2017, 64(6): 1367. doi: 10.1109/TNS.2017.2693296 [7] 马聪. LHAASO WCDA前端读出电子学的研究[D]. 合肥: 中国科学技术大学, 2017. MA Cong. Research of Front-end Electronics for the WCDA in LHAASO[D]. Hefei: University of Science and Technology of China, 2017. (in Chinese) [8] CALVO D, REAL D. Journal of Instrumentation, 2015, 10(01): C01015. doi: 10.1088/1748-0221/10/01/C01015 [9] 褚少平. LHAASO WCDA读出电子学时钟同步与数据传输研究[D]. 合肥: 中国科学技术大学, 2017. CHU Shaoping. Research of Clock Synchronization and Data Transmission in LHAASO WCDA Readout Electronics [D]. Hefei: University of Science and Technology of China, 2017. (in Chinese) [10] PENNEY A. Assembly Automation, 1995, 15(2): 20. doi: 10.1108/01445159510086407 -

下载:

下载:

甘公网安备 62010202000723号

甘公网安备 62010202000723号