Design of FDOA ASIC for Charge Measurement Circuit in Shaping and Peak Detection Method

-

摘要:

放大成形结合数字寻峰的技术路线在粒子物理实验电荷测量中有着广泛的应用。由于高精度模数转换器大多是差分电压输入,基于提高测量精度、减小共模干扰等因素考虑,需要将放大成形后的单端信号转换为差分信号。为了满足粒子物理实验读出电子学高精度、低功耗、多通道等需求,定制化设计了一款全差分运放(Fully Differential Operational Amplifier, FDOA) ASIC(Application Specific Integrated Circuit, ASIC)。为了在较低的功耗下实现更大的压摆率和带负载能力,融合电流复用技术和AB类推挽放大器结构完成了FDOA ASIC的设计。基于180 nm CMOS工艺完成了电路的设计、仿真和流片。测试结果表明,该芯片的单通道功耗约为28.3 mW,压摆率约为745.4 V/μs,带负载能力约为±50 mA,噪声约为173 μV,在20 MHz、2 Vpp的正弦波信号输入下实现了好于70 dB的总谐波失真。

Abstract:The technical route of amplification & shaping and digital peak detection has been widely used in charge measurement in particle physics experiments. Since most high-precision Analog to Digital Converters are differential voltage inputs, it is necessary to convert the single ended signal after amplification & shaping into differential signal based on factors such as improving measurement accuracy and reducing common mode interference. In order to meet the requirements of high precision, low power consumption and multi-channel of readout electronics in particle physics experiments, a FDOA (Fully Differential Operational Amplifier) ASIC (Application Specific Integrated Circuit) is customized and designed. In order to achieve larger slew rate and load capacity with lower power consumption, the FDOA ASIC is designed by combining current multiplexing technology and class AB push-pull amplifier structure. Based on 180 nm CMOS process, the circuit design, simulation and streaming are completed. The test results show that the single channel power consumption of the chip is about 28.3 mW, and the slew rate is about 745.4 V/μs. The load capacity is about ±50 mA, the noise performance is about 173 μV. And the THD (Total Harmonic Distortion) is better than 70 dB under the signal input of 20 MHz and 2 Vpp.

-

0. 引言

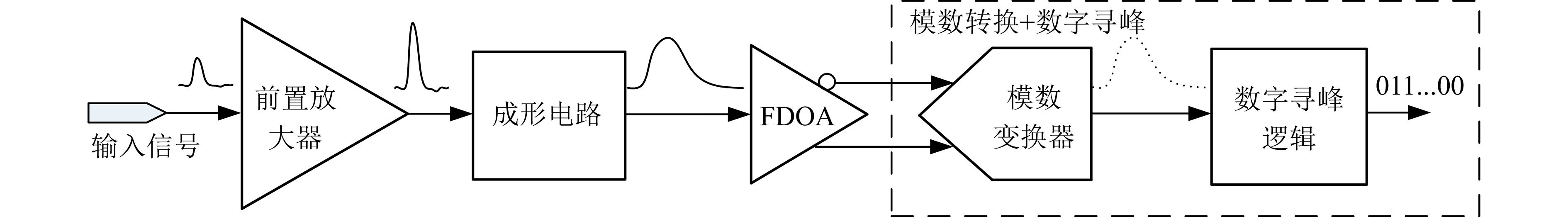

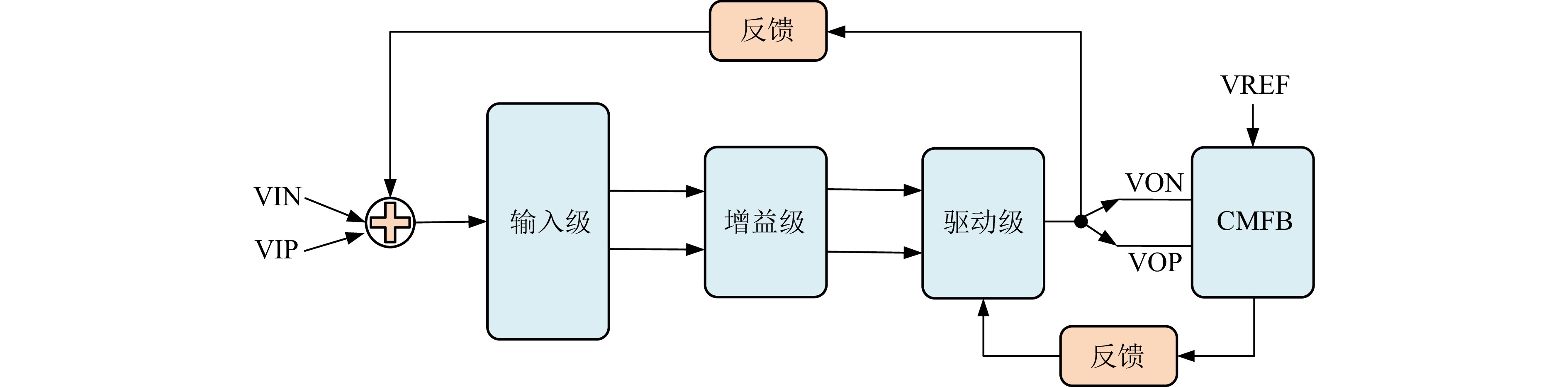

粒子物理实验是研究物质微观结构、基本粒子之间相互作用和运动规律的手段之一。通过测量探测器输出波形的时间和电荷信息,可以获得入射粒子的能量、类别、时间等信息。其中,放大成形结合数字寻峰的技术路线是提取微弱信号电荷信息的重要技术手段,如图1所示,来自探测器的信号首先进入前置放大器进行放大,然后进入成形电路将信号成形为准高斯脉冲,接着经过单端转差分的处理再送入模数转换器(Analog to Digital Converter, ADC)中进行采样和量化,有利于提升电荷测量的精度;最后结合数字寻峰技术,可以进一步降低功耗,简化系统的复杂度[1]。

实现电荷到电压转换的前置放大器主要包括电压灵敏放大器和电荷灵敏放大器,前者适用于能量分辨要求较低的系统,后者适用于能量分辨要求较高的系统。典型的放大成形专用集成电路(Application Specific Integrated Circuit, ASIC)主要包括应用于GEM探测器的VFAT3[2]和GEMROC2[3],应用于Micromegas探测器的VMM3[4],应用于Silicon Strip探测器的Beetle[5]等。中国科学技术大学核探测与核电子学国家重点实验室已完成了一款应用于MTPC探测器的ASIC[6],它们的共同特点是采用180 nm或130 nm CMOS工艺的制程,输出的是单端信号,动态范围约0~1 V,成形时间为25~200 ns,对应的信号频率在20 MHz以内。用作ADC驱动器的商用全差分运放(Fully Differential Operational Amplifier, FDOA)芯片通常采用Bipolar/BiCMOS工艺或定制化的工艺,具有更加优异的带负载能力但增加了较大的成本,如ADA4932、THS4541等,其允许通过的大信号带宽高达百兆赫兹,但功耗通常在百毫瓦的量级。针对粒子物理实验规模巨大、通道数多的特点,要求读出电子学系统具备较低的功耗、较高的信噪比等特性;过高的FDOA带宽不仅会带来更大的功耗,还会使无用的信号通过,进而降低系统的信噪比。

因此,为了接收来自典型的放大成形ASIC输出的单端信号,输出差分信号并驱动ADC正常工作,需要定制化地设计一款FDOA ASIC。针对前端放大成形ASIC输出信号的特点,FDOA ASIC的输入共模范围设计为0~1 V,大信号带宽设计为20 MHz,对应的压摆率至少为125.6 V/μs,为保证信号的精度,压摆率应设计为理论值的5倍以上,为700 V/μs;噪声应小于12 bit ADC的1 LSB,设计为300 μV;FDOA ASIC的总谐波失真应不低于后端ADC的总谐波失真,即好于70 dB。表1中总结了FDOA ASIC的设计指标。

表 1 FDOA ASIC的设计指标参数名称 设计指标 工艺 180 nm CMOS 开环增益/dB >80 输入共模范围/V 0~1 大信号带宽/MHz 20 压摆率@10 pf/ (V/μs) >700 噪声@0.01 Hz~1 GHz/μV <300 总谐波失真/dB >70 共模抑制比/dB >100 电源抑制比/dB >80 功耗 <30 mW/ch 1. FDOA ASIC设计

1.1 整体结构

FDOA的一般结构如图2所示,主要包括输入级、增益级、驱动级和共模负反馈(Common Mode Negative Feedback Circuit, CMFB),三级电路需要复杂的密勒补偿调整频率响应。

为了降低功耗,简化电路结构,在本设计中将输入级和增益级糅合到了一起;由于前端放大成形ASIC输出信号具有较大的动态范围,输入级电路需要保证较大的共模输入范围,同时具备中等的增益和较低的噪声。在用作ADC驱动器的FDOA ASIC的设计中,输出驱动级的设计希望在尽量小的静态功耗下输出更大的电流,实现良好的驱动能力和尽可能小的谐波失真。为了解决差模负反馈无法确定输出共模电压的问题,通常在FDOA中添加CMFB,稳定输出共模电压;CMFB主要包括共模电平检测电路和反馈电路组成,需要重点关注共模环路稳定性的问题,且要求具有较好的PVT(Process, Voltage and Temperature)效应。由于不同工艺角下MOS管的阈值电压不同,因此在偏置电路的设计中,通过二极管接法的MOS管产生电压后进行偏置。

1.2 输入级

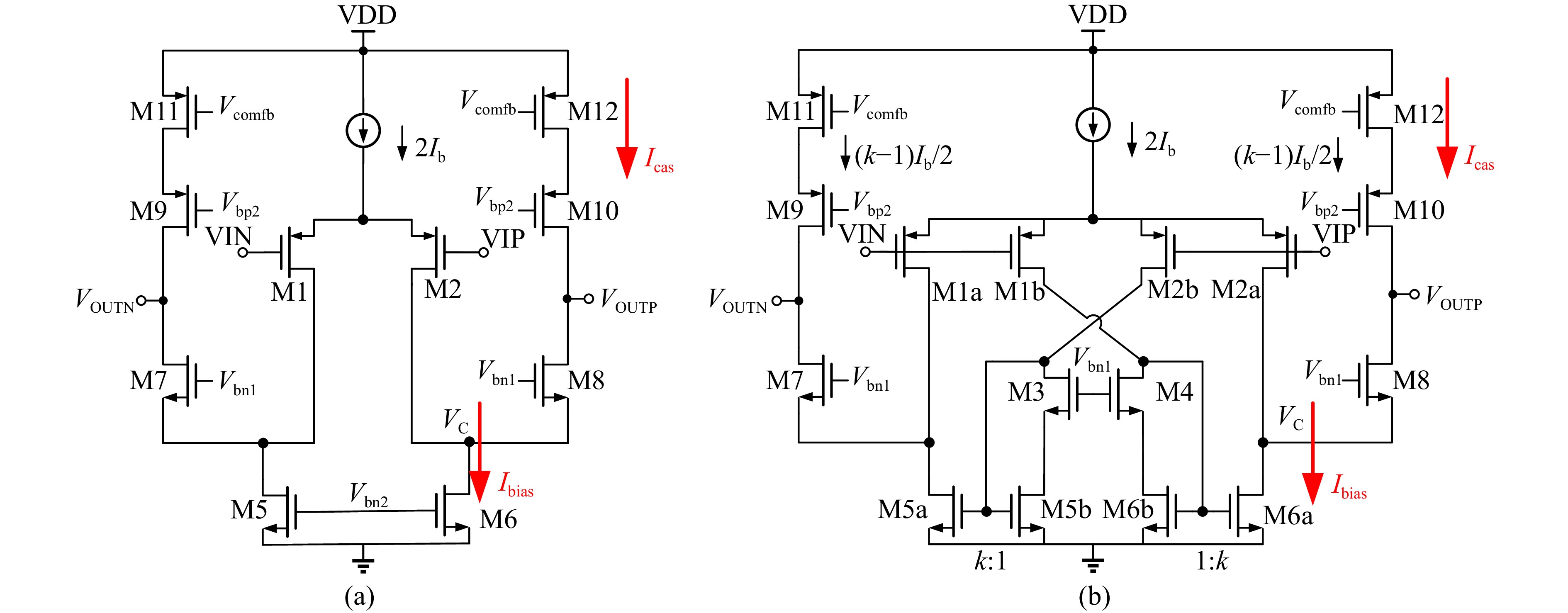

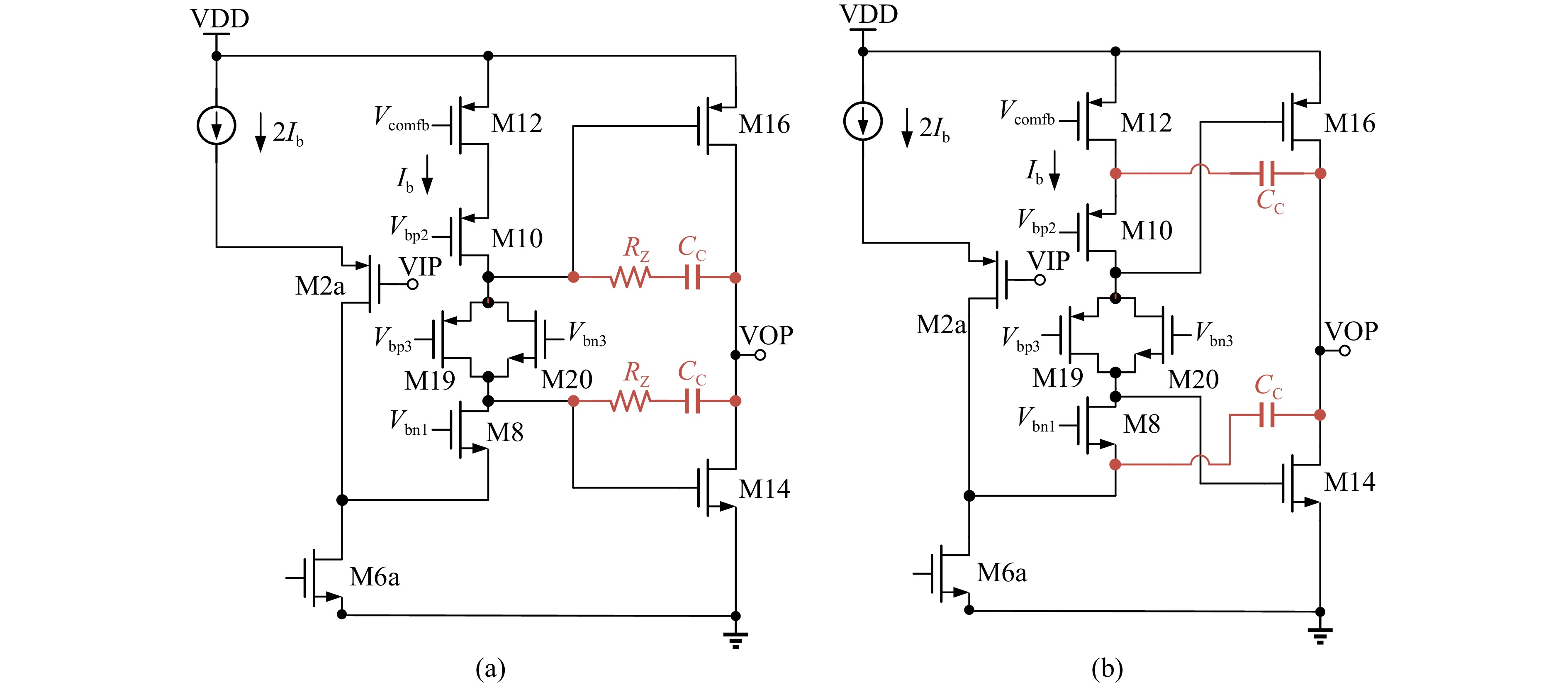

目前主流的前端放大成形ASIC通常采用的是180 nm或130 nm的制程,其共模输出电压的范围通常在0~1 V。为了获得较大的共模输入范围和中等的增益,采用了折叠式共源共栅结构,代价是功耗略有增加;基于提高测量精度、减小共模干扰等因素考虑,输入级电路采用了差分输入,相较于单端输入,差分输入的优势在于具有更好的抗共模干扰能力,共模抑制比高。考虑较低的共模输入范围,即VIN,CM<1 V,输入级采用PMOS差分对,具有较低的闪烁噪声,同时消除了体效应带来的影响。整体结构如图3(a)所示。

传统折叠式共源共栅结构的压摆率(SR)与运放的偏置电流(Ib)成正比,即$ SR = {{{I_{\text{b}}}} \mathord{\left/ {\vphantom {{{I_{\text{b}}}} {{C_{\rm L}}}}} \right. } {{C_L}}} $(CL为输出端负载),电流利用效率有限。为了在同等的功耗下,进一步提升电路的压摆率,增加电路的驱动能力,本设计中输入级采用了电流复用技术[7−8],如图3(b)所示,输入对管M1、M2拆分成四个尺寸一样的管子(M1a、M1b和M2a、M2b),折叠点处的电流源M5、M6拆分成电流镜的形式(M5a、M5b和M6a、M6b);为了保证使电流镜的复制更加准确,同时减小运放输出共模点的偏差,增加了M3、M4管以使两组电流镜的漏级电压近似相等,M3、M4管与M7、M8的尺寸相近。为了使折叠式共源共栅支路上的电流保持不变,电流镜的尺寸比例k通常取3。

当VIP电压上升,M2a和M2b关断,同时M5a和M5b关断;流经M1a和M7的电流会流进M5a的漏级,使M5a漏级电位升高,将M1a和M7推向截止区;此时尾电流源的电流全部流向M1b,M1b支路的电流经过电流镜(M6a, M6b)的3倍镜像对负载电容进行充放电,此时VOUTP端的压摆率为$ S{R^ + } = {{5{I_{\text{b}}}} \mathord{\left/ {\vphantom {{5{I_{\text{b}}}} {{C_L}}}} \right. } {{C_L}}} $,VOUTN端的压摆率为$ S{R^ + } = {{{I_{\text{b}}}} \mathord{\left/ {\vphantom {{{I_{\text{b}}}} {{C_L}}}} \right. } {{C_L}}} $;VOUTP和VOUTN充放电的不平衡被迅速转换为共模误差,并通过CMFB电路进行调整,最终得到VOUTP和VOUTN相近的压摆率为$ SR = {{3{I_{\text{b}}}} \mathord{\left/ {\vphantom {{3{I_{\text{b}}}} {{C_L}}}} \right. } {{C_L}}} $。电流复用技术的优势在于,相较于传统折叠式共源共栅结构,将摆率提升了3倍。当然,由于寄生电容的存在及M1a和M5a的不完全关断,所以达不到理想的3倍。该电路的代价是在M5a、M5b和M6a、M6b引入了镜像极点,降低了相位裕度。

图3所示的两种输入级电路具有相似的噪声性能,本设计应用于20 MHz以内的宽带系统,主要关注的是热噪声,单位带宽的等效输入噪声为

$$ \overline {V_{\text{n}}^2} = 8kT\left(\frac{2}{{3{g_{{\text{m}}1}}}} + \frac{{2{g_{{\text{m5}}}}}}{{g_{{\text{m}}1}^2}} + \frac{{2{g_{{\text{m}}11}}}}{{3g_{{\text{m}}1}^2}}\right) \text{,} $$ (1) 其中:k为玻尔兹曼常数;T为绝对温度;gm1、gm5、gm11分别为M1、M5、M11的跨导。可以看到,小的噪声需要大的输入跨导,两个电流源同样贡献了较大的噪声,需要减小它们的跨导。

输入差分对是主要的非线性来源,将输入对管偏置在亚阈值区有利于改善电路的非线性,并且可以得到较高的跨导[9],但弱反型区的速度比较慢,使得电路工作频率不可能很高。因此,为了保证电路的非线性,同时具有较宽的工作频率,在本设计中将输入对管的过驱动电压设置在150 mV左右;为避免在大信号转换时较低的源漏电压引入的非线性,将输入对管的源漏电压设置在900 mV左右。

1.3 驱动级

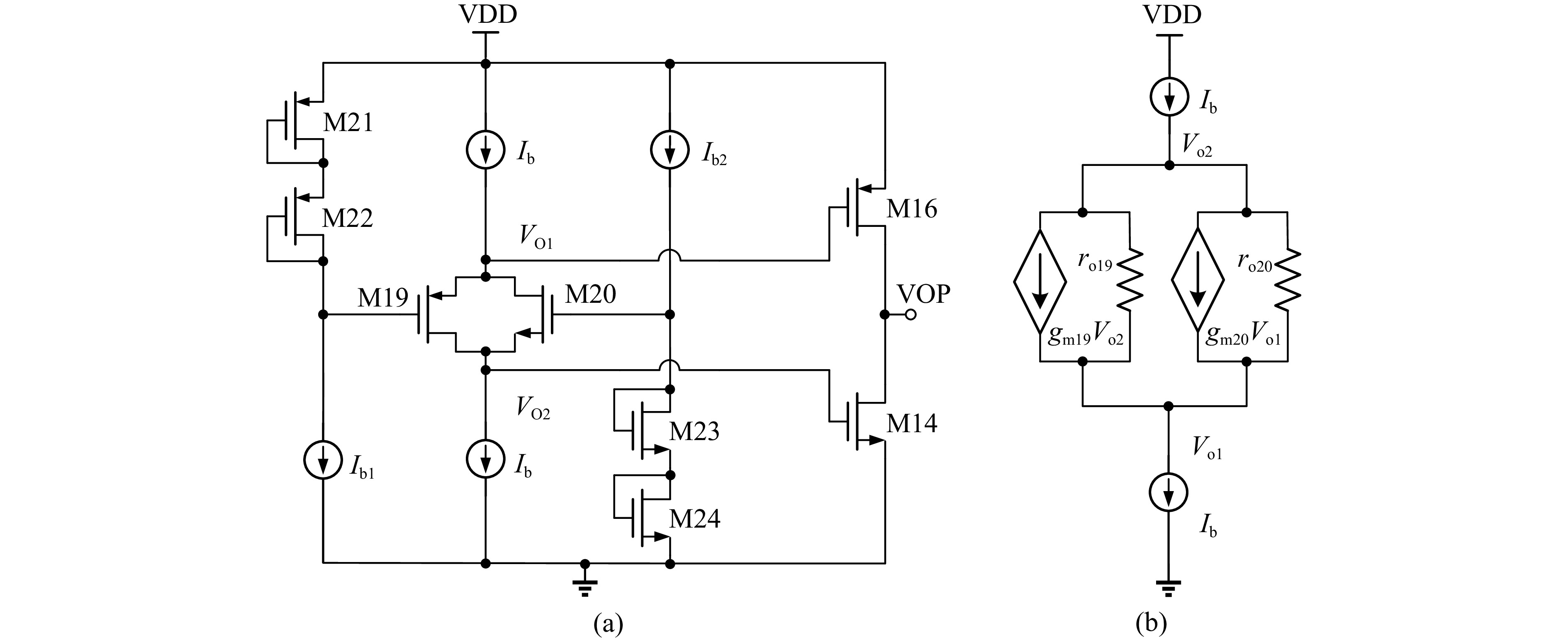

在用作ADC驱动器的FDOA ASIC的设计中,输出驱动级的设计希望在尽量小的静态功耗下输出更大的电流,实现良好的驱动能力和尽可能小的谐波失真。针对运算放大器工作模式的不同,将输出驱动级分为A类、B类和AB类,划分的方式主要依据失真程度和电流效率。为了综合A类和B类运放的特点,AB类运放在驱动级的设计中得到了广泛的应用。

实现AB类输出的结构,需要实现大信号电平移位,小信号交流短路的功能。一种实现AB类输出的结构如图4(a)所示,称为跨导线性环(Trans-linear Loop)[10]。M16、M19、M21、M22和M14、M20、M23、M24分别构成了两个线性回路,决定了输出级的静态电流。为了减小跨导线性环结构引起的噪声和失调,在放大器第一级的输出端插入了跨导线性环[11],关键电路结构如图5所示。通过合理的调节VO1和VO2的差使输出级偏置在AB类,同时保证VO1和VO2的差值恒定,也就是等价于小信号增益为0。图4(b)是对它的小信号分析,当VO1上升时,M20管的Vgs20(M20管的栅源电压)降低,流经M20管的电流降低:

$$ \Delta I = {{{g}}_{{\text{m}}20}} \times \Delta {V_{{\text{O1}}}} \text{,} $$ (2) 其中:∆I为流经M20管电流的变化值;gm20为M20管的跨导;∆VO1为VO1点电压的变化值。

在Ib不变的情况下,此时流经M19管的电流增加∆I,M19管的源端电压VO2上升:

$$ \Delta {V_{{\text{O}}2}} = \frac{{{{{g}}_{{\text{m}}20}} \times \Delta {V_{{\text{O}}1}}}}{{{g_{{\text{m}}19}}}} \text{,} $$ (3) 其中:gm19为M19管的跨导;∆VO2为VO2点电压的变化值。因此,在设计中若保证gm19=gm20,则VO2-VO1保持恒定,也就是等价于交流短路。

在大信号转换时,输出级最大的推挽电流可以表示为

$$ \begin{split} {I_{{\text{pull}}}} = & {(W/L)_{14}} \times {\left({\text{2}}\sqrt {\frac{{{I_{{\text{dsp}}23}}}}{{{{(W/L)}_{23}}}}} \right)^{\text{2}}}{{ - }}{(W/L)_{16}} \times \\ & {\left({\text{2}}\sqrt {\frac{{{I_{{\text{dsp22}}}}}}{{{{(W/L)}_{22}}}}} - \sqrt {\frac{{{I_{{\text{bias}}}}}}{{{{(W/L)}_{19}}}}} \right)^{\text{2}}} \text{,} \end{split} $$ (4) $$ \begin{split} {I_{{\text{push}}}} = & {(W/L)_{16}} \times {\left({\text{2}}\sqrt {\frac{{{I_{{\text{dsp}}22}}}}{{{{(W/L)}_{22}}}}} \right)^{\text{2}}} - {(W/L)_{14}} \times \\ & {\left({\text{2}}\sqrt {\frac{{{I_{{\text{dsp}}23}}}}{{{{(W/L)}_{23}}}}} - \sqrt {\frac{{{I_{{\text{bias}}}}}}{{{{(W/L)}_{20}}}}} \right)^{\text{2}}} \text{,} \end{split}$$ (5) 其中:W和L分别是晶体管的宽度和长度;Idsp为晶体管的电流;Ibias为折叠式共源共栅支路的电流。由式(4)~(5)可以看出,跨导线性环的效率也是有限的,摆率的提升会受到电流的限制。为了在同等功耗下进一步提升输出级的最大推挽电流,本设计中采用电流复用技术,结合跨导线性环结构,提高电流利用的效率,进一步提升输出级的推挽电流,增大电路的带负载能力。

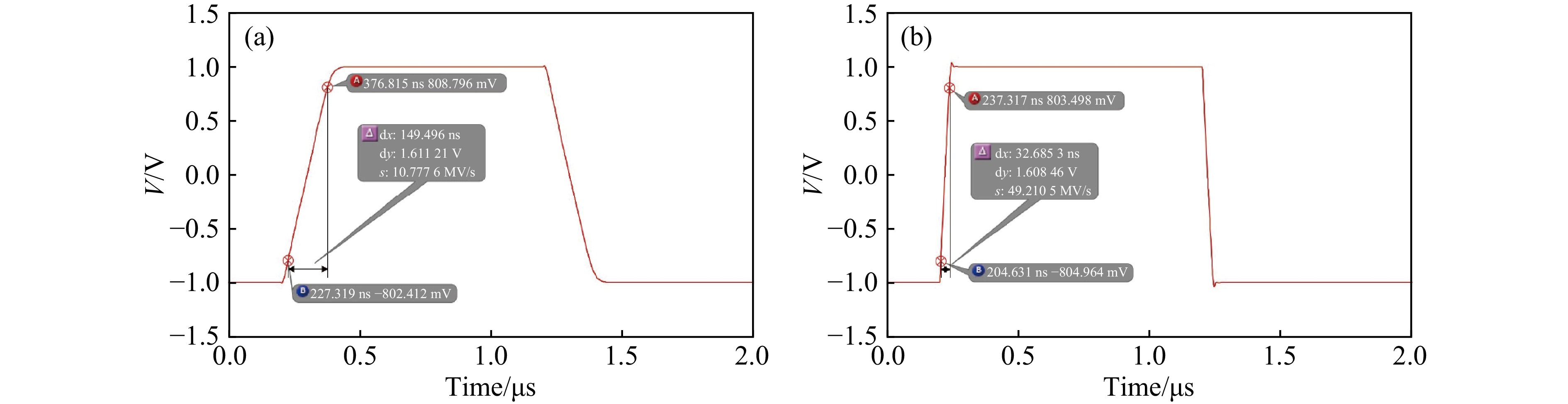

首先在较小的功耗水平下分别对如图2所示的两种输入级电路结构进行了整体电路的前仿真,如图6给出了约1.2 mW功耗下的压摆率性能,图6(a)为传统的折叠式共源共栅输入级,压摆率为10.7 V/μs;图6(b)为采用了电流复用技术的折叠式共源共栅输入级,压摆率为49.2 V/μs,关键指标总结如表2所列。从图6中可以看见,在相似的功耗下,摆率提升了约5倍左右。代价是降低了相位裕度,从图6(b)中也可以看见阶跃响应中存在过冲现象。

表 2 两种输入级电路结构的仿真指标总结参数名称 仿真指标 电路(a) 电路(b) 工艺 180 nm CMOS 180 nm CMOS 电源电压/V +1.8 +1.8 静态电流/mA 0.68 0.64 压摆率/(V/μs) 10.7 50.3 相位裕度/(°) 68 61 1.4 补偿电路

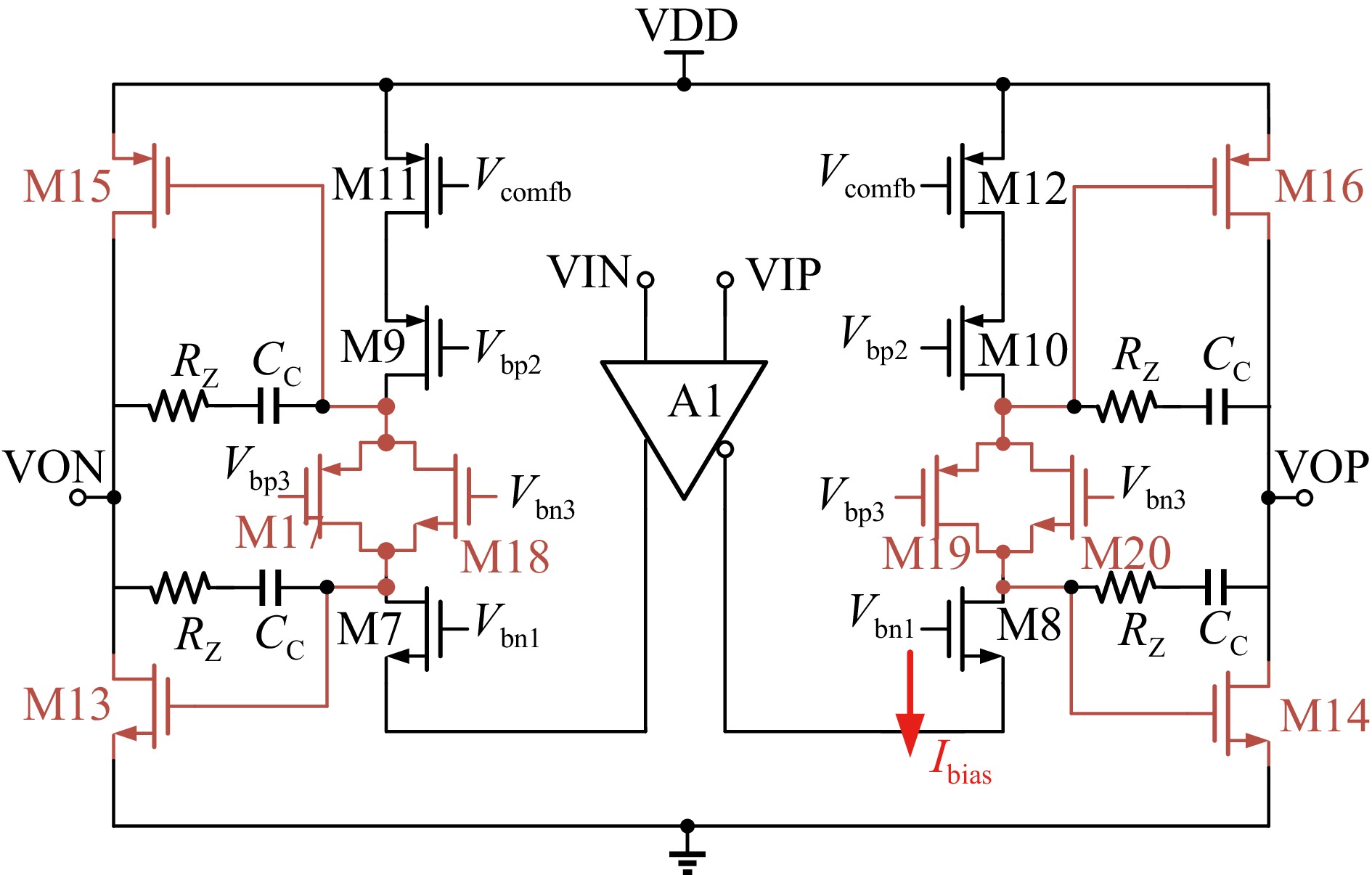

常见的电路补偿方式为密勒补偿,如图7(a)所示,它通过引起主、次极点分裂,增大带宽和电路稳定性,此时输出极点为

$$ {{\text{w}}_{{\text{out}}}} = \frac{{{g_{{\text{m14}}}}{g_{{\text{m16}}}}}}{{{C_{\text{L}}}({g_{{\text{m}}14}} + {g_{{\text{m}}16}})}} \text{,} $$ (6) 其中:gm14、gm16分别为M14管和M16管的跨导;CL为负载电容。

但该种补偿方式会引入右半平面的零点,通过选取合适的调零电阻RZ可以将零点移到左半平面,消除第二极点,但调零电阻在实际制作过程中实现困难;高频时,电源上的噪声通过M16栅漏之间的低阻抗通路耦合到输出端,造成电源抑制比降低。

如图7(b)所示,cascode补偿[12]的意义在于将次级点推向了更加远离原点的位置,增大了小信号带宽,同时消除了高频下的前馈通路,提升了电源抑制比的性能,此时输出极点为

$$ {w_{{\text{out}}}} = \frac{{{g_{{\text{m}}14}}{g_{{\text{m}}16}}}}{{{C_{\text{L}}}({g_{{\text{m14}}}} + {g_{{\text{m}}16}})}} \times \frac{{2{C_{\text{C}}}}}{{{C_{{\text{gs}}16}} + {C_{{\text{gs}}14}}}} \text{,} $$ (7) 其中:Cgs14、Cgs16分别为M14管和M16管的栅源电压;CC为负载电容。但该种补偿方式将原来的次极点变成了一对共轭复极点,这会导致增益裕度的下降,即使有足够的相位裕度,瞬态响应也会有过冲产生[13]。

在确定芯片的核心电路后,本文对普通密勒补偿和cascode补偿分别进行了研究和仿真。需要指出,该部分的仿真在最终版的芯片上完成的。其中,普通密勒补偿的带宽功耗比为7.5 MHz/mW,而cascode补偿的带宽功耗比为18.2 MHz/mW;cascode补偿比普通密勒补偿的电源抑制比提升了约3 dB。

1.5 CMFB

本文选择了电阻结合误差放大器的形式实现共模负反馈,如图8所示。使用两个电阻即可得到输出共模电平,这个方法的缺点在于此电阻将作为输出负载直接加在运放的输出端,因此,为了不影响运放的开环增益,此电阻阻值一般较大,本设计中电阻取值为10 kΩ,占用较大的面积,但是该方法精确简单。误差放大器采用的是两级放大器来实现,第一级放大器为M25、M26作为输入管,通过M27和M28组成的电流镜对第一级的输出进行偏置,第二级和差分回路是一样的。VREF为外部提供参考输出共模电压,设计为1 V,Vcomfb是共模环路反馈到主运放中的控制电压,这里连接到M11、M12栅极。

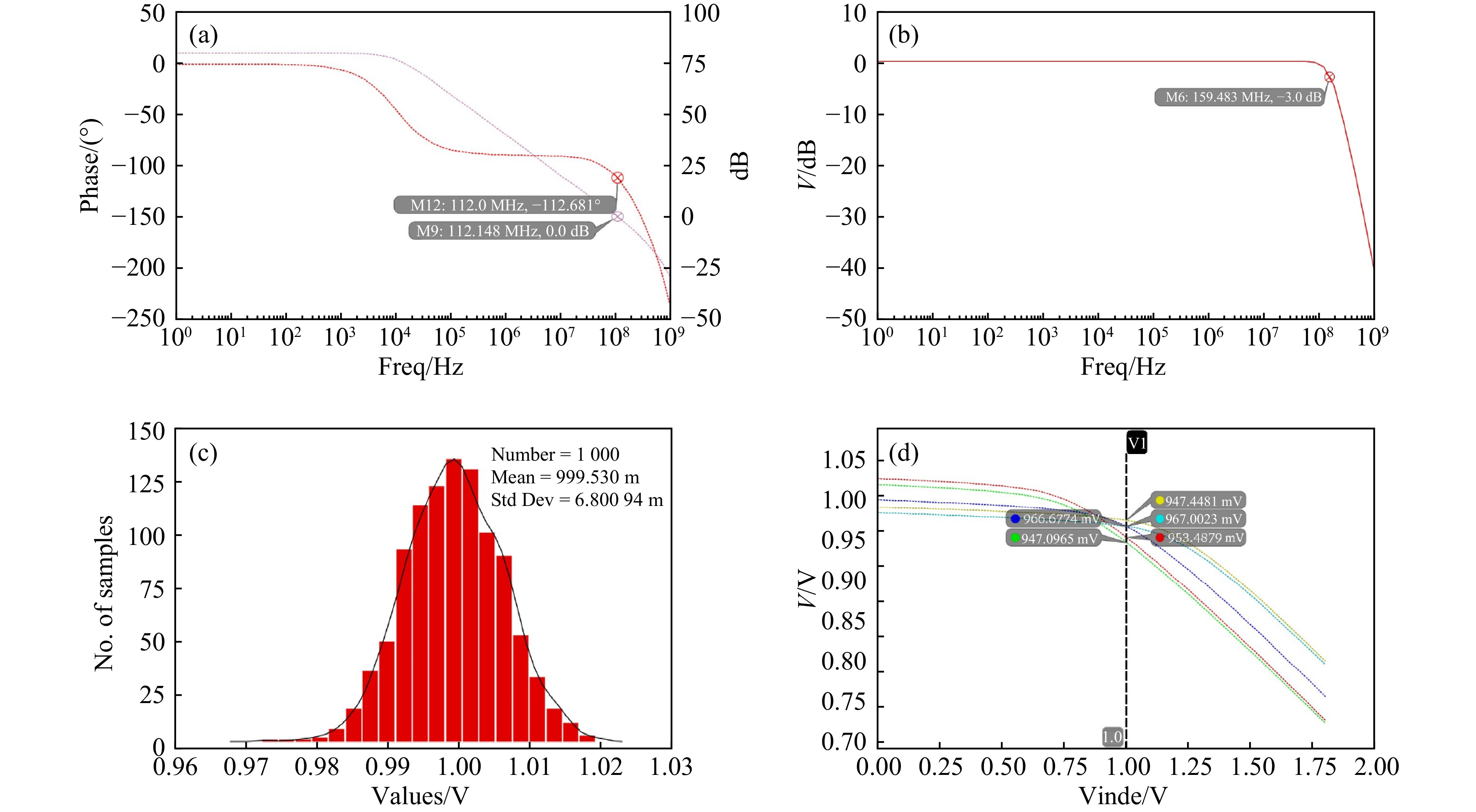

CMFB的回路同样需要关注带宽和稳定性的问题。为确保设计的合理性,首先对共模负反馈回路进行了增益和相位裕度的仿真,如图9(a)所示,增益约80 dB,相位裕度约68°;如图9(b)所示,共模回路的−3 dB小信号带宽约160 MHz;其次,对共模输出电压进行了1 000次蒙特卡罗仿真,包含工艺角和失配这两种随机变化,如图9(c)所示,仿真结果表明均能输出1 V左右的共模电压;最后,不同工艺角下共模输入范围的仿真结果如图9(d)所示,仿真结果表明,在0~1 V内均能稳定工作。

2. 版图设计与后仿真

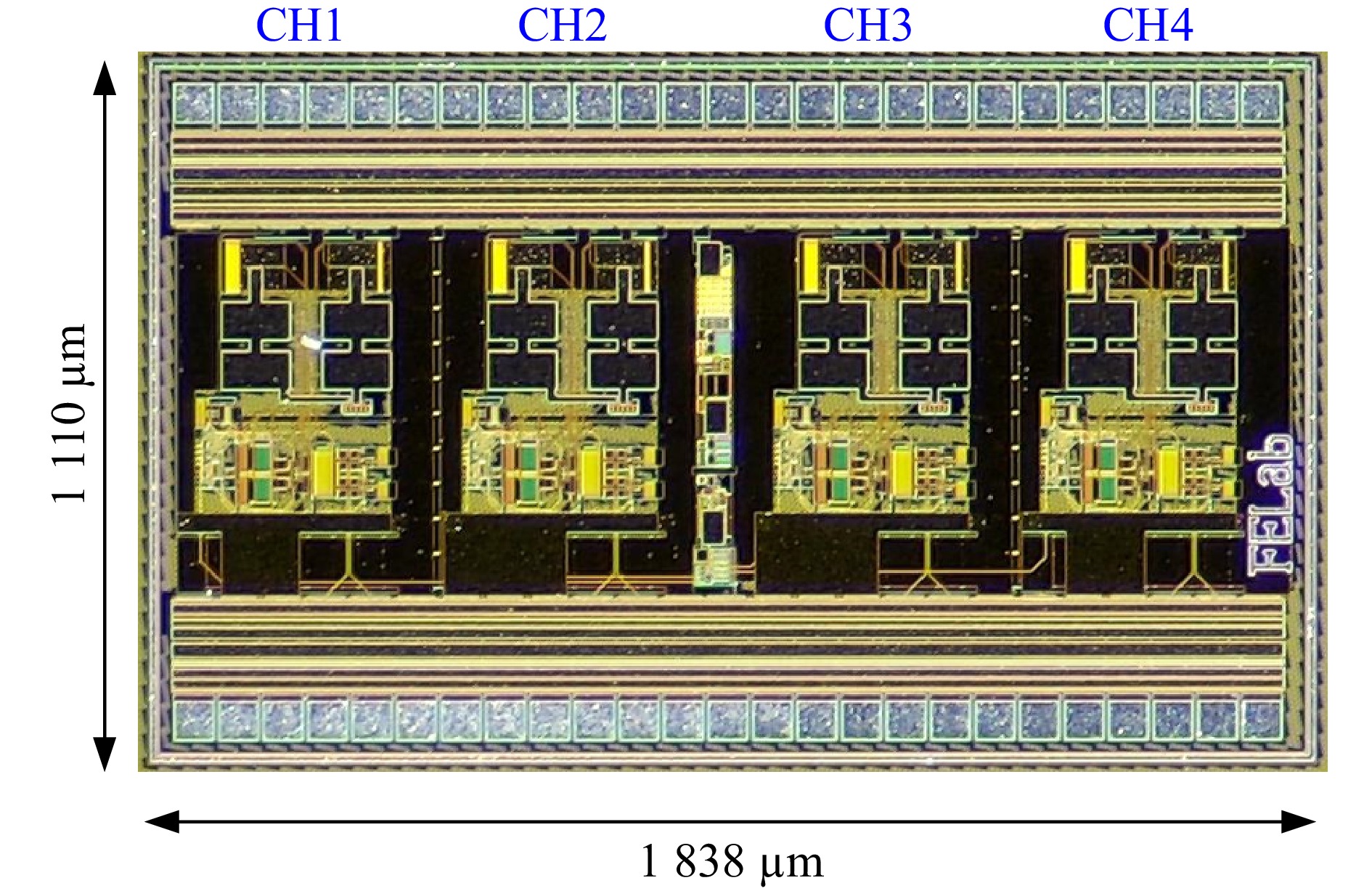

本设计基于180 nm CMOS工艺设计了FDOA ASIC的版图,如图10所示。尺寸为1 110 μm×1 838 μm,包含四个通道,采用Bandgap进行内部偏置。对FDOA ASIC单通道的版图提取RC寄生参数,进行PVT仿真,详细的指标总结如表3所列。在用作ADC驱动器的FDOA ASIC的设计中,关注的主要指标性能为压摆率、电路稳定性、噪声和带负载能力,依次给出详细的仿真结果。

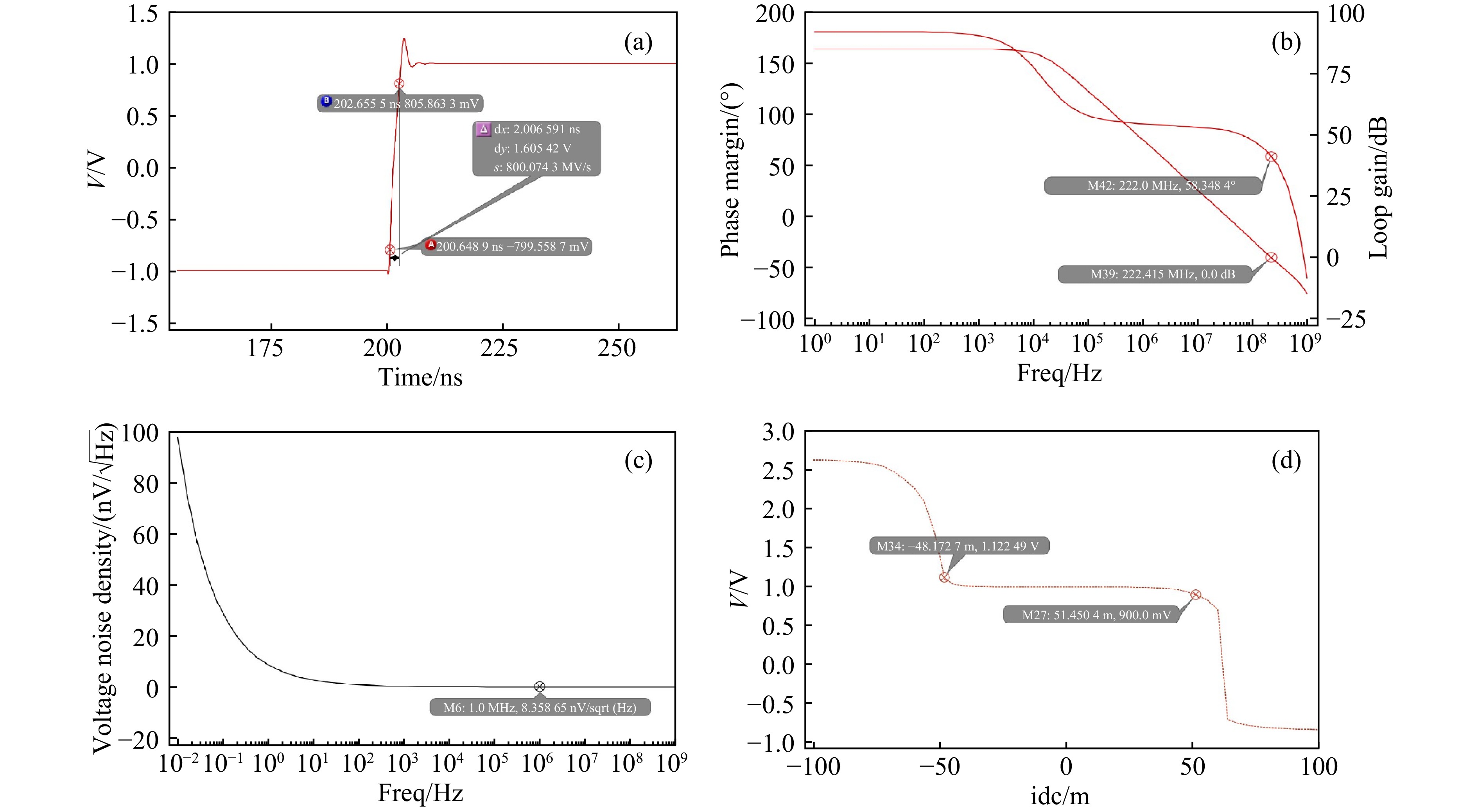

表 3 FDOA ASIC的指标总结指标 FDOA ASIC 工艺 180 nm CMOS 开环增益*/ dB 82 输入共模范围*/ V 0~1 共模抑制比*/ dB 103 电源抑制比*/ dB 86 电压裕度*/ V 1.6~2.0 功耗/ mW <28.3 压摆率/(V/μs) 745.4 THD@15.5 MHz, 2 Vpp/ dB 73.2 噪声/μV 173 输出驱动能力/ mA ±50 注:* 表示后仿性能。 图11(a)给出了ss corner下的瞬态仿真,其中压摆率大于800 V/μs,后仿真结果显示未达到电流复用技术中理想情况下的五倍,这是由于随着管子尺寸的增大,寄生电容产生了较大的影响。同时可以看到ss corner下瞬态响应有明显的过冲现象,这是由于电路采用的cascode补偿方式将原来的次极点变成了一对共轭复极点,这会导致增益裕度的下降,即使有足够的相位裕度,瞬态响应也会有过冲产生,这在ss corner下表现得更为明显。图11(b)给出了ss corner下的幅频和相频特性曲线,其中开环增益大于80 dB,相位裕度大于58°。图11(c)给出了ss corner下的等效输入噪声曲线,本设计应用于20 MHz以内的宽带系统,主要关注的是热噪声,为8.3 nV/$ \sqrt{{\mathrm{Hz}}} $ @1 MHz。图11(d)给出了ss corner下的带负载能力,当输出共模电压变化10 %时,对应的电流值即运放的带负载能力。后仿真结果显示输出驱动能力达±50 mA,实现了约1∶16的动静态电流比。

3. 测试结果

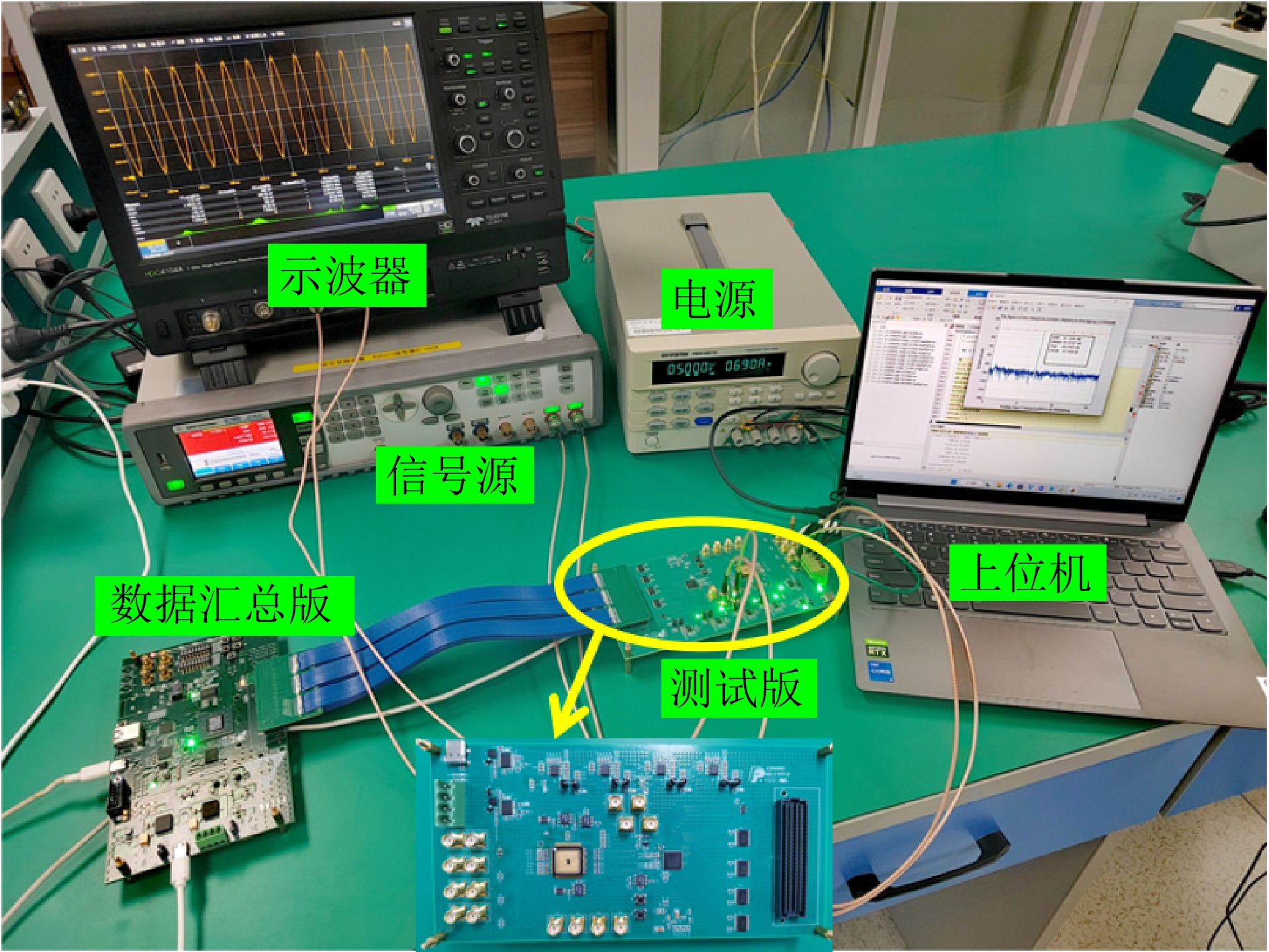

FDOA ASIC采用CQFP100的封装,完整的测试平台如图12所示[14−15]。测试板选用了一款商用ADC芯片采集待测芯片的输出信号,并送入数据汇总板进行数据读出,最后由上位机软件进行数据处理与分析。

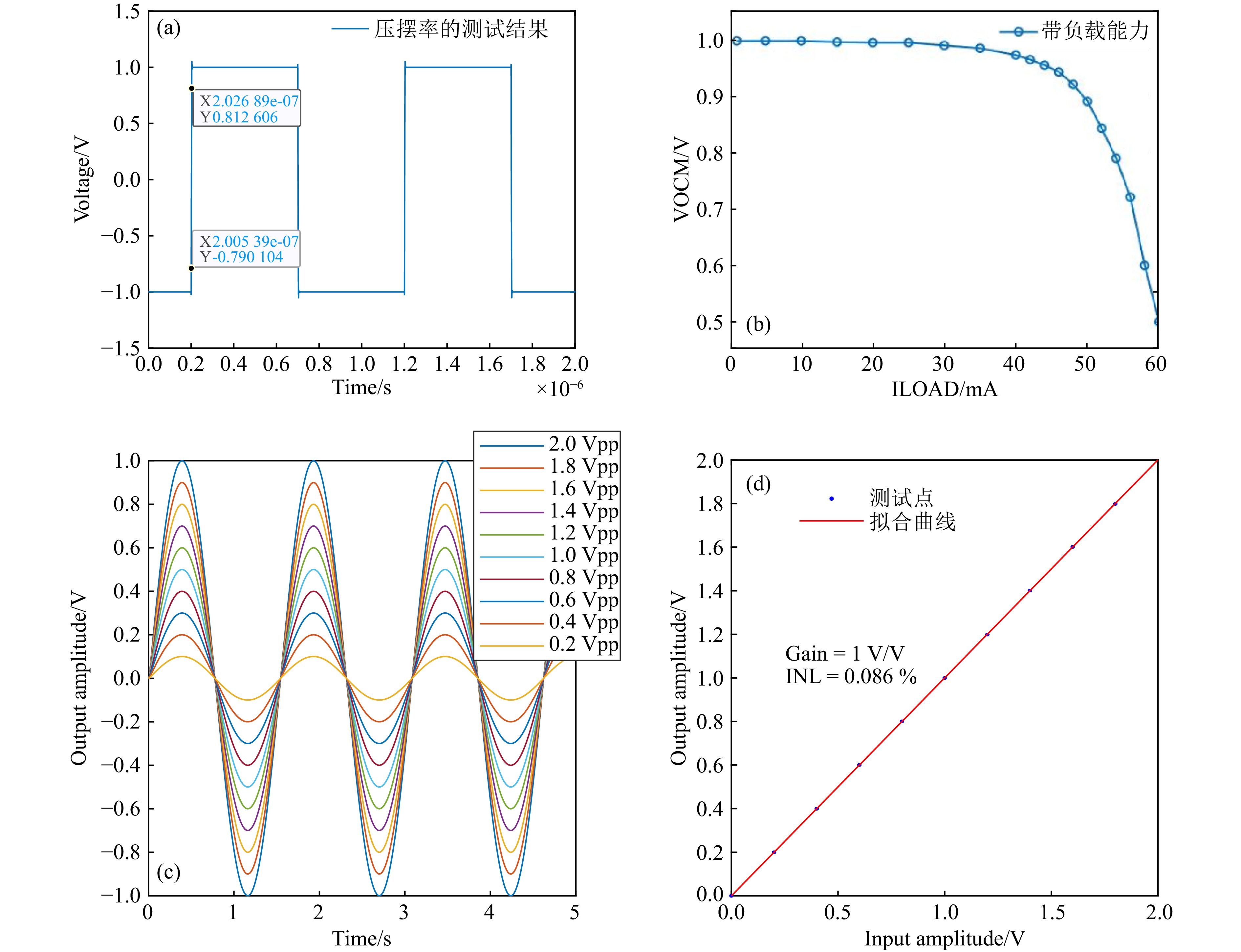

如表3所列,首先测量了芯片单通道的功耗,约为28.3 mW,噪声约173 μV,与后仿真指标相吻合。其次对压摆率进行了测试,如图13(a)所示,测试结果显示,压摆率约为745.4 V/μs,相较于后仿结果降低了约60 V/μs,这是由于在测试过程中为增加电路稳定性,增加了一个1.8 pf的反馈电容;同时,对待测芯片的带负载能力进行了测试,如图13(b)所示,测试结果显示,带负载能力约为50 mA,与后仿结果近似;通过向待测芯片送入不同幅值的正弦波信号,对待测芯片的积分非线性(Integral Non-Linearity, INL)进行了测试,如图13(c)~(d)所示,测试结果显示,INL的最差结果为0.086%。

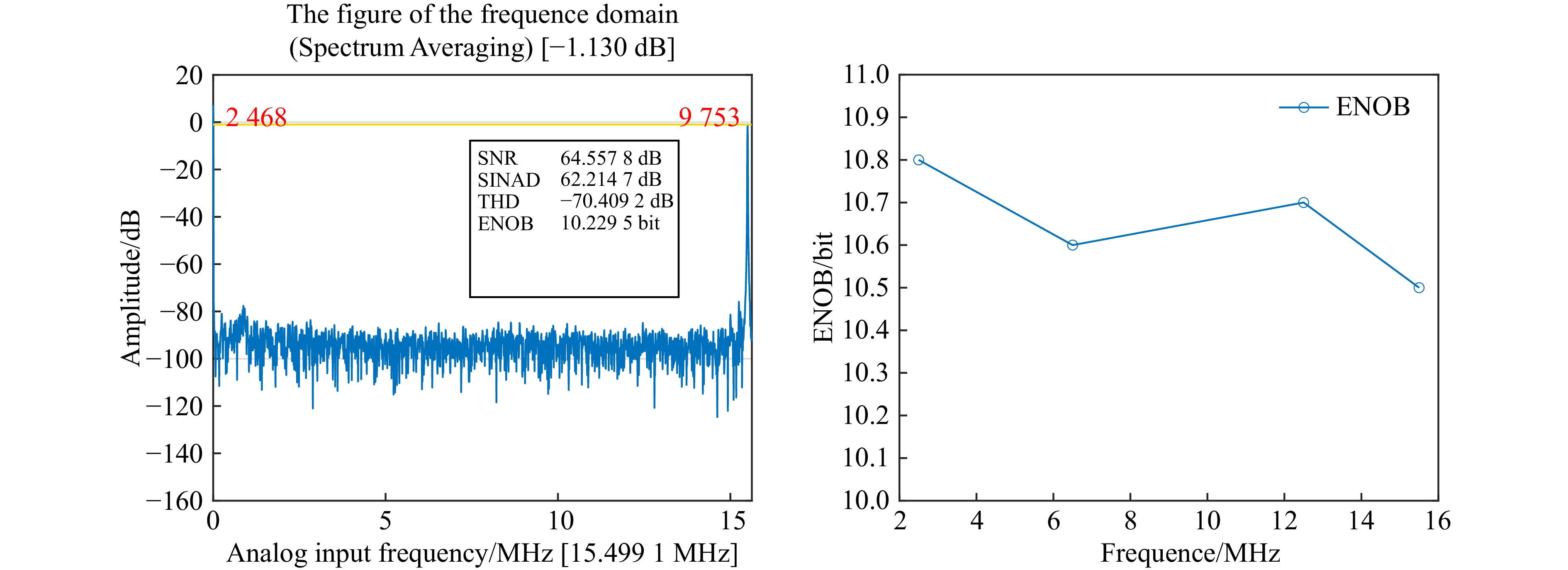

最后对芯片的动态性能进行了测试,ADC采样率设置为31.25 MSPS,输入正弦波信号进行性能测试。图14(a)给出在15.5 MHz,2 Vpp的正弦波信号输入下可以达到73.2 dB的总谐波失真,实现了10.5 bit的有效位;图14(b)给出了在采样率为31.25 MSPS,不同输入信号频率下动态性能的变化曲线,从图中可以看出,随输入频率升高,有效位大体上逐渐降低。

4. 总结

本文针对粒子物理实验中基于放大成形结合数字寻峰技术进行电荷测量的需要,为了满足粒子物理实验读出电子学高精度、低功耗、多通道等需求,定制化设计了一款融合电流复用技术和AB类推挽放大器结构的FDOA ASIC,在较低的功耗下实现了更大的压摆率和带负载能力。

测试结果表明,该芯片的单通道功耗约为28.3 mW,压摆率约为745.4 V/μs,带负载能力约为±50 mA,噪声约为173 μV,在20 MHz、2 Vpp的正弦波信号输入下实现了好于70 dB的总谐波失真,满足成形寻峰电路中电荷测量的需要。

-

表 1 FDOA ASIC的设计指标

参数名称 设计指标 工艺 180 nm CMOS 开环增益/dB >80 输入共模范围/V 0~1 大信号带宽/MHz 20 压摆率@10 pf/ (V/μs) >700 噪声@0.01 Hz~1 GHz/μV <300 总谐波失真/dB >70 共模抑制比/dB >100 电源抑制比/dB >80 功耗 <30 mW/ch 表 2 两种输入级电路结构的仿真指标总结

参数名称 仿真指标 电路(a) 电路(b) 工艺 180 nm CMOS 180 nm CMOS 电源电压/V +1.8 +1.8 静态电流/mA 0.68 0.64 压摆率/(V/μs) 10.7 50.3 相位裕度/(°) 68 61 表 3 FDOA ASIC的指标总结

指标 FDOA ASIC 工艺 180 nm CMOS 开环增益*/ dB 82 输入共模范围*/ V 0~1 共模抑制比*/ dB 103 电源抑制比*/ dB 86 电压裕度*/ V 1.6~2.0 功耗/ mW <28.3 压摆率/(V/μs) 745.4 THD@15.5 MHz, 2 Vpp/ dB 73.2 噪声/μV 173 输出驱动能力/ mA ±50 注:* 表示后仿性能。 -

[1] LIU J F, ZHAO L, YU L, et al. Chinese Physics C, 2016, 40(6): 49. DOI: 10.1088/1674-1137/40/6/066101

[2] PETROW H, ASPELL P, CIAGLIA D, et al. Journal of Instrumentation, 2021, 16(2): P02005. DOI: 10.1088/1748-0221/16/02/P02005

[3] FIUTOWSKI T, DABROWSKI W, MINDUR B, et al. Design and Performance of the GEMROC ASIC for 2-D Readout of Gas Electron Multiplier Detectors[C]//IEEE. New York: IEEE, 2011.

[4] ZHANG Z, WANG X, MIAO P, et al. Journal of Instrumentation, 2020, 15(08): T08007. DOI: 10.1088/1748-0221/15/08/T08007

[5] KOSTNER S, STRAUMANN U. Noise Considerations of the Beetle Amplifier Used with Long Silicon Strip Detectors[R]. Geneva: CERN, 2005.

[6] LI J M, ZHAO L, QIN J J, et al. IEEE Transactions on Nuclear Science, 2023, 70: 1030. DOI: 10.1109/TNS.2022.3210754

[7] ASSAAD R, SILVA-MARTINEZ J. Electronics Letters, 2007, 43(23): 1243. DOI: 10.1049/el:20072031

[8] ASSAAD R, SILVA-MARTINEZ J. IEEE Journal of Solid-State Circuits, 2009, 44(9): 2535. DOI: 10.1109/JSSC.2009.2024819

[9] CORNER D J, CORNER D T. IEEE Transactions on Circuits & Systems II Express Briefs, 2004, 51(1): 8. DOI: 10.1109/TCSII.2003.821517

[10] RAKSHITDATTA K S, MITIKTRI Y, KRISHNAPURA N. IEEE Transactions on Circuits and Systems II: Express Briefs, 2015, 63(5): 443.

[11] HOGERVORST R, TERO J P, ESCHAUZIER R, et al. EEE Journal of Solid-State Circuits, 1994, 29(12): 1505. DOI: 10.1109/4.340424

[12] BASUMATA U, MONDAL A, DAS S, et al. Design of Two-Stage Fully-Differential Driver in SAR ADC with Indirect Feedback Compensation Technique[C]//2021 International Symposium on Devices, Circuits and Systems (ISDCS). 2021.

[13] AHUJA B K. IEEE Journal of Solid-State Circuits, 2003, 18(6): 629. DOI: 10.1109/JSSC.1983.1052012

[14] YUSUF S I, SHAFIE S, MAJID H A, et al. Indonesian Journal of Electrical Engineering and Computer Science, 2020, 17(2): 750. DOI: 10.11591/ijeecs.v17.i2.pp750-758

[15] ARDIZZONI J, PEARSON J. Analog Dialogue, 2009, 43(5): 3.

下载:

下载:

甘公网安备 62010202000723号

甘公网安备 62010202000723号