文章编号: 1007-4627(2016) 04-0449-06

# HIRFL-CSR 外靶实验 T0 探测器前端电子学原型模块设计

夏品正<sup>1,2</sup>, 赵 雷<sup>1,2</sup>, 邓佩佩<sup>1,2</sup>, 董若石<sup>1,2</sup>, 刘树彬<sup>1,2</sup>, 安 琪<sup>1,2</sup>

(1. 中国科学技术大学核探测与核电子学国家重点实验室,合肥 230026; 2. 中国科学技术大学近代物理系,合肥 230026)

摘要:介绍了兰州重离子加速器冷却储存环 (HIRFL-CSR) 外靶实验中时间起点探测器 (T0) 的前端电子学原型模块的设计与测试。探索了基于过阈时间法和专用集成电路 NINO 芯片进行多气隙电阻板室探测器信号读出的模拟前端电路的设计技术,并实际完成了原型电子学模块的设计。此模块共集成 6 个测量通道,可以进行前沿甄别及电荷时间变换。目前已经在实验室条件下完成了各项电子学性能测试,包括不同甄别阈值下的时间精度测试以及不同输入信号幅度下的输出脉宽测试。测试结果表明,在 100 fC 至 2 pC 的动态范围内,此模块时间精度好于 20 ps,满足应用需求,这也为进一步的电子学系统设计做好了准备。

关键词: T0探测器; 时间测量; NINO; TOT; HIRFL; CSR; 外靶实验

中图分类号: O571.42 文献标志码: A **DOI**: 10.11804/NuclPhysRev.33.04.449

## 1 引言

兰州重离子加速器 (HIRFL)<sup>[1-2]</sup>是我国规模最大的重离子研究装置,具有加速全离子的能力,可提供多种类,宽能量范围,高品质的稳定核束和放射性束,用以开展重离子物理及交叉学科研究。在HIRFL实验装置中,从电子回旋共振(ECR)离子源产生的离子经过扇聚焦回旋加速器 (SFC)和分离扇回旋加速器 (SSC)后,经放射性束流线 (RIBLL1)引出至重离子冷却储存环 (CSR)。CSR由主环 (CSRm)、实验环 (CSRe)、RIBLL2以及外靶实验装置组成,实现了离子的累积、冷却、存储、加速,是一个大型多功能的物理实验装置。

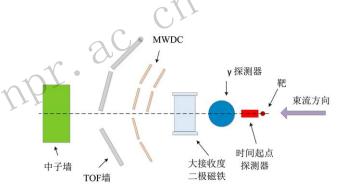

外靶实验的探测器布局如图 1<sup>[3]</sup>所示,利用大接收度的二极磁铁,配合时间起点探测器 (T0), γ探测器,多丝漂移室 (Multi-Wire Drift Chamber,MWDC)、飞行时间 (Time Of Flight,TOF) 谱仪和中子墙探测器实现对重离子打靶产物的探测和鉴别。T0 探测器位于整个探测器系统的前端,为物理实验提供精确的时间起点。针对T0 探测器高精度时间测量的应用需求,本文基于TOT 技术,对T0 探测器前端电子学 (Front End Electronics,FEE) 原型模块进行了设计,并对其电子学设计与性能测试两方面展开了阐述。

图 1 (在线彩图)外靶实验装置布局图

## 2 FEE原型模块设计

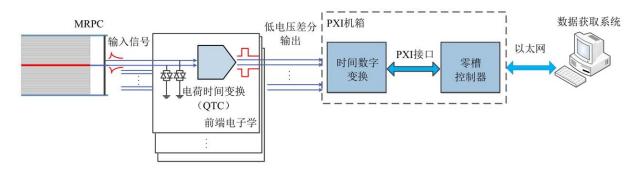

TO 探测器的读出电子学系统结构如图 2 所示,MRPC探测器产生的输出信号经过前端电子学模块实现基于过阈时间法 (Time Over Threshold, TOT) 技术的电荷-时间变换(Charge-to-Time Converting, QTC), 其输出信号前沿包含输入信号的时间信息, 其脉宽对应于输入信号的电荷量大小,将此信号输入后端的时间数字变换器 (Time-to-Digit Converter, TDC) 完成时间数字化,同时得到前沿与脉宽信息,从而完成时间与电荷测量。后端数字化模块基于工业智能总线 PXI<sup>[4]</sup>设计,测量数据通过 PXI 接口汇总到机箱零槽控制器并最终通过以太网传输至数据获取 (DAQ) 系统。

收稿日期: 2015-11-19; 修改日期: 2015-12-09

基金项目: 国家自然科学基金资助项目(11079003,U1232206); 中国科学院知识创新工程重要方向性项目(KJCX2-YW-N27); 中国科学院 院粒子物理前沿卓越创新中心支持

作者简介: 夏品正(1991-), 男, 安徽人, 硕士研究生; E-mail: xpz91@mail.ustc.edu.cn

通信作者: 赵雷, E-mail: zlei@ustc.edu.cn。

图 2 (在线彩图) T0探测器读出电子学系统结构

## 2.1 FEE设计方案

T0 探测器系统对于 FEE 的性能要求是在 100 fC 至 2 pC 的输入信号动态范围内时间精度好于 25 ps,此外还要求 FEE 模块可以实现多通道集成,以便在未来的工程化应用中单模块实现 16 通道甚至 24 通道的 TOT 测量。

基于以上考虑,FEE原型模块选用了NINO 芯片 $^{[5]}$ 实现电荷-时间变换。NINO芯片采用 $0.25~\mu m$  CMOS 工艺制作,单片集成8路测量通道,其性能指标 $^{[6]}$ 显示,输出信号的上升时间为1~n s,输入信号的动态范围为100~f C至2~p C,电荷测量噪声性能好于5~000~e - RMS (5~000~h e - F所携带电荷量,约为0.8~f C),前沿时间抖动性能好于25~p s RMS,甄别阈值为10~E = 100~f C。

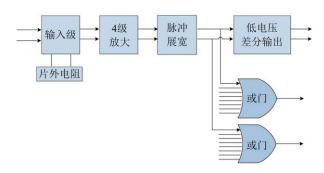

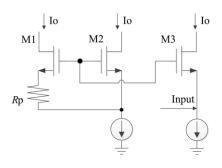

图 3 为 NINO 内部结构示意图<sup>[6]</sup>, NINO 采用了全差分结构,输入级利用片外电阻设置输入阻抗,实现阻抗匹配,输入信号经过四级放大,最后通过低电压差分信号 (LVDS) 驱动级输出,此外,在驱动级前对8通道做逻辑或,其输出可用做简单的触发信号。

图 3 (在线彩图) NINO结构示意图

## 2.2 输入保护电路及阻抗匹配设计

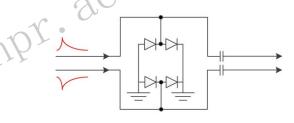

在FEE 原型模块的设计中,FEE 直接接收探测器信号,在最前端将探测器输出的模拟信号进行电荷-时间转换,最大程度避免探测器输出信号在传输过程中的质量下降。为了防止探测器在非正常工作状

态下输出过大的信号,对FEE造成损坏,在信号输入端设计保护电路,所选用的保护器件为SEMTECH公司的RClamp0502A TVS(Transient Voltage Suppressor)阵列,该器件包含4个限幅二极管以及一个TVS管,可以支持多种连接方式的设计实现不同的应用需求。图4为保护电路设计,利用了RClamp0502A中的限幅二极管对信号的正负幅度进行限制,避免过大的信号送入NINO芯片。

图 4 输入保护电路设计

为最大程度降低反射等信号完整性问题对测量性能的影响,需要对探测器产生的信号进行阻抗匹配。 FEE设计时利用了可调的片外电阻设置 NINO 芯片的输入阻抗,实现所有通道的阻抗匹配。

NINO的输入级结构<sup>[6]</sup>如下图 5 所示,信号从 M3 管的源级送入,输入阻抗为

$$Z_{\rm in} = \frac{1}{gmsb_{\rm M3}} \ , \eqno(1)$$

其中 $gmsb_{M3}$ 为M3管的跨导。

图 5 NINO输入级原理图

通过片外电阻设置输入管 M3 的偏置电压,从而改 变输入阻抗。NINO芯片通过设计合适的物理尺寸,最 终使得输入阻抗直接由进行调节

$$Z_{\rm in} = \frac{1}{gmsb_{\rm M3}} = \frac{1}{gmsb_{\rm M2}} = R_{\rm p}$$

, (2)

在FEE 原型模块的设计中,为NINO 外接50 欧姆电 阻,以实现对传输线的阻抗匹配。图6为设计完成的 FEE模块照片。

## FEE模块测试

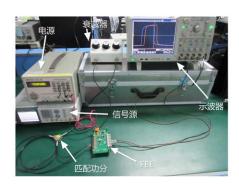

为评估此原型模块的性能指标,针对此模块进行了 一系列实验室条件下的电子学性能测试。测试平台如 图 7 所示,通过 Agilent 81180A 信号源产生信号波形, 再通过衰减器和匹配功分器得到测试信号,改变衰减 器的衰减值,可以调节测试信号的幅度,将测试信号 输入 FEE 模块, 最终将 FEE 模块输出的信号输入示波 器,实现各种电子学性能测试。

图 7 (在线彩图)测试平台

完成的主要测试有阈值标定测试、时间精度测试、 输入输出转换曲线测试以及触发信号输出功能测试。

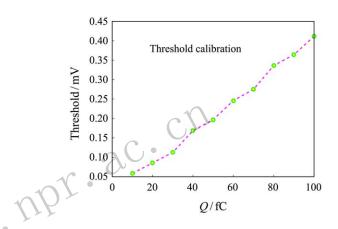

#### 3.1 阈值标定

FEE 模块通过改变 NINO 芯片的阈值设置管脚的 电压来调节甄别的电荷量阈值, 此设置管脚的电压幅度 并不直接对应于电荷量阈值,因此首先需要对FEE模块 的阈值进行标定。具体测试方法为S-curve<sup>[7]</sup>方法,为 标定某一特定电荷量阈值所对应的设置电压,首先输入 该电荷量对应的测试信号,再连续调节设置电压,使得 触发率变为信号源输出事例率的二分之一, 即认为此时 的设置电压为当前输入电荷量所对应的甄别电压。

阈值标定结果如图8所示,阈值曲线接近线性。

图 8 (在线彩图) 阈值标定曲线

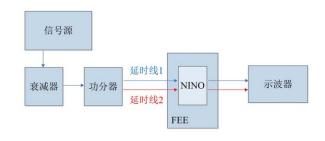

#### 3.2 时间精度测试

T0 探测器最重要的功能是实现高精度的时间测量, 因此必须对此FEE模块的时间精度性能进行测试。为 了更准确的测试FEE模块的时间精度性能,测试中采 用延迟线方法,以消除信号源本身的 Jitter 对测试结果 的影响,测试原理图如图9所示。

图 9 (在线彩图)延时线方法测试原理图

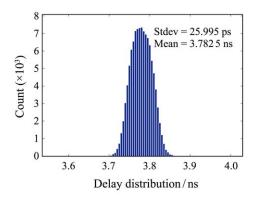

信号源产生的脉冲信号送入衰减器和功分器,得到 两路等幅的输入信号,分别经过不同长度的延时线1.2 后进入FEE上的两路测量通道,经过QTC芯片NINO 甄别后的两路输出信号分别送入示波器, 利用示波器 测量这两路输出信号前沿的时间差,并统计时间差测 量结果的标准差。由于不同测量通道之间不存在相关 性,因此测量得到的标准差除以即得到此FEE 模块的 RMS Jitter,对于某一典型输入幅度下的两路输出信号的时间差测量结果,其分布如下图 10 所示,标准差为 25.995 ps,对应单通道 Jitter 为 18.38 ps。

图 10 (在线彩图)输出信号延时差分布

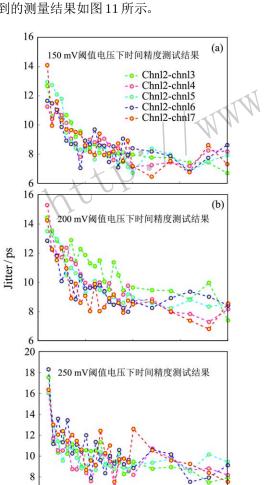

在不同阈值条件下,测试FEE模块的时间精度性能,得到的测量结果如图11所示。

图 11 (在线彩图) 不同阈值电压下FEE时间精度测试结果

10

Q/fC (×10<sup>2</sup>)

15

20

从图中可看出,对于相同的阈值,随着输入信号幅度增加,FEE输出信号的Jitter快速下降,并最终稳定,这是因为输入信号幅度越大,前沿越陡峭,噪声对前沿时间影响越小。在100 fC~2 pC的动态范围内,Jitter测量结果好于20 ps,测试结果符合预期的性能要求。

## 3.3 输入输出转换曲线测试

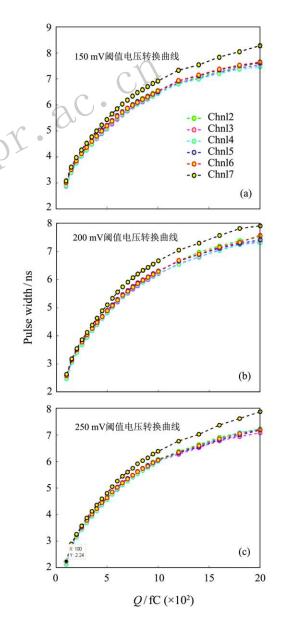

此FEE模块基于TOT技术设计,其输出信号的脉宽包含了输入信号的电荷量信息,因此需要对输入输出转换曲线进行测试。

选取3组不同的阈值,150,200,250 mV,测试输入电荷量与输出脉宽的转换曲线,如图12所示。

图 12 (在线彩图) 不同阈值电压FEE输入输出转换曲线

随着输入电荷量的增加,输出脉宽的变化趋势一致。对于相同输入电荷量,甄别阈值越高,输出脉宽越窄,这是符合预期的。

以上的输入输出转换曲线的测试结果显示:此FEE 模块在无展宽的情况下,输出脉宽在输入400 fC 以下信号时小于4 ns。考虑到某些后端TDC 模块对于脉冲

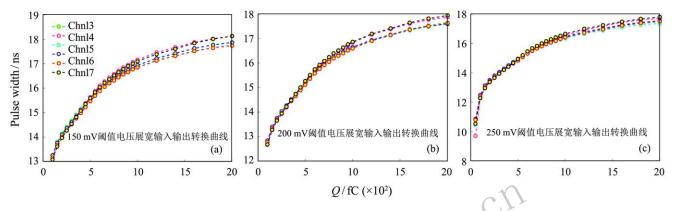

宽度的要求,宽度小于4 ns 的脉冲难以被TDC 有效测量,因此需开启 FEE 模块的展宽功能,开启展宽功能后,测试得到的输入输出转换曲线如图 13 所示。

针对展宽功能的测试结果显示,开启展宽功能后,此 FEE 模块在  $100~{\rm fC}\sim 2~{\rm pC}$  的动态范围内,输出信号的脉宽都大于  $10~{\rm ns}$ ,符合预期。

图 13 (在线彩图)不同阈值电压FEE展宽输入输出转换曲线(开启展宽)

## 3.4 触发信号输出功能测试

此FEE模块可以通过对所有通道的输出级做逻辑或,求或的结果输出可作为触发信号使用,下面对这一触发信号输出功能进行了测试。

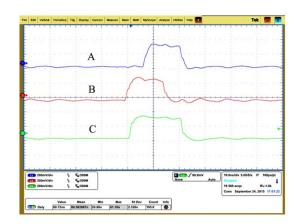

图 14 为 NINO 芯片触发输出的波形,其中波形 A 和波形 B 为 FEE 模块两路测量通道的输出信号,波形 C 为 FEE 模块输出的触发信号,由此可以验证输出的触发信号是测量通道输出波形逻辑求或的结果,触发信号输出功能正常,可以考虑在未来的系统中利用此 FEE 模块输出的触发信号实现简单的触发功能。

图 14 (在线彩图) FEE模块触发信号输出波形

### 4 总结

针对HIRFL-CSR TO探测器的应用需求,进行了

基于TOT技术的FEE原型模块的设计,并在实验室完成了一系列电子学性能测试,测试结果显示,此FEE模块功能正常,各项指标满足应用需求。在本工作的基础上,需要进一步结合TO探测器的最新需求,进行更完善的FEE模块设计,并开展与后端数字化系统的联合测试。

#### 参考文献:

- ZHENG Chuan, XIAO Zhigang, XU Hushan, et al. High Energy Physics and Nuclear Physics, 2007, 31(12): 1177. (in Chinese)

- (郑川, 肖志刚, 徐瑚珊, 等. 高能物理与核物理, 2007, **31**(12): 1177)

- [2] XIA J W, ZHAN W L, WEI B W, et~al. Nucl Instr and Meth A, 2002,  ${\bf 488}(1)\colon$  11.

- [3] ZHAO Lei, KANG Longfe. Nuclear Science and Techniques, 2014, 25(1): 010401.

- [4] PXI Hardware Specification Revision 2.2[OL], [S.l.]: [S.N.], September 22, 2004. http://www.pxisa.org/userfiles/files/ Specifications/PXIHWSPEC22.pdf.

- [5] ANGHINOLFI F, JARRON P, MARTEMIYANOV A N, et al. Nucl Instr and Meth A, 2004, 533(1): 183.

- [6] ANGHINOLFI F, JARRON P, KRUMMENACHER F, et al. Nuclear Science, IEEE Transactions on, 2004, 51(5): 1974.

- [7] ANGELO RIVETTI. CMOS: Front-End Electronics for Radiation Sensors[M]. Boca Raton: CRC Press, 2015: 37.

# Prototype Front End Electronics of T0 Detector in the External Experiment of CSR in HIRFL

XIA Pinzheng<sup>1,2</sup>, ZHAO Lei<sup>1,2</sup>, DENG Peipei<sup>1,2</sup>, DONG Ruoshi<sup>1,2</sup>, LIU Shubin<sup>1,2</sup>, AN Qi<sup>1,2</sup>

(1. State Key Laboratory of Particle Detection and Electronics, University of Science and Technology of China, Hefei 230026, China;

2. Department of Modern Physics, University of Sciences and Technology of China, Hefei 230026, China)

**Abstract:** A prototype front end electronics (FEE) module is designed for the T0 detector in the External Experiment in CSR (Cooling Storage Ring) of HIRFL (Heavy Ion Research Facility in Lanzhou). Based on the Time-Over-Threshold method and NINO ASIC, a total of 6 channels are integrated in the module, and both high precision leading edge discrimination and Charge-to-Time Conversion can be achieved, which satisfies the readout requirement of MRPC (Multi-gap Resistive Plate Chamber). A series of tests were also conducted in the laboratory, including time precision tests with different thresholds and output pulse width tests with different input signal amplitudes. Test results indicate that this prototype module functions well, and the time precision is better than 20 ps in the dynamic range from 100 fC to 2 pC, which is beyond application requirement. Through nttp. this work, preparation is made for the future readout system design.

Key words: T0 detector; time measurement; NINO; TOT; HIRFL; CSR; external target experiment

Received date: 19 Nov. 2015:

Foundation item: National Natural Science Foundation of China (11079003,U1232206); Knowledge Innovation Program of Chinese Academy of Sciences (KJCX2-YW-N27); Center for Excellence in Particle Physics of Chinese Academy of Sciences(CCEPP)

Revised date: 9 Dec. 2015

Corresponding author: ZHAO Lei, E-mail: zlei@ustc.edu.cn.