文章编号: 1007-4627(2014)04-0499-06

## 基于ASIC芯片的硅微条阵列探测器多通道前端电子学模块设计

赵兴文1,2,苏弘1,千奕1,孔洁1,章学恒1,闫铎1,2,李占奎1,李海霞1

(1. 中国科学院近代物理研究所, 兰州 730000;

2. 中国科学院大学, 北京 100049)

摘要: 描述了为兰州重离子加速器冷却储存环 (HIRFL-CSR) 外靶实验系统硅微条阵列探测器而设计的前端电子学模块。该模块采用专用 ASIC 芯片,可以处理 96 路能量信号。对前端电子学模块的性能进行了测试,结果表明,该模块在  $0.1 \sim 0.7$  V 范围内的积分非线性好于 0.3%; 其电子学分辨好于 0.45%,最大串扰小于 10%; 通道一致性测试结果好于 1.3%; 在室温下连续工作 24 h后,零点峰位最大漂移为 1.48 mV。

关键词: 前端电子学; 硅微条阵列探测器; ASIC

中图分类号: TN492 文献标志码: A **DOI**: 10.11804/NuclPhysRev.31.04.499

### 1 引言

随着半导体技术的迅速发展,各种半导体探测器都有了很多新的发展,其中硅微条探测器的发展非常突出,被广泛应用于核物理、高能物理、天体物理等实验中<sup>[1]</sup>。双面硅微条探测器因具有较好的位置和能量分辨、较宽的线性范围等优点而被广泛使用<sup>[2]</sup>。另外高集成化低噪声前端电子学的发展,进一步推动了硅微条探测器的发展提高<sup>[3]</sup>。在过去的三十年里,硅微条探测器与其电子学系统都获得了长足发展,国际上许多实验室都成功设计开发了针对不同硅微条探测器的ASIC芯片,如美国费米国家实验室(FNAL)质子-反质子对撞机系统CDF采用的SVX

芯片<sup>[4]</sup>,欧洲核子研究中心 (CERN) 大型强子对撞机 上 CMS 实验所采用的 APV25 芯片<sup>[5]</sup>和ALTAS实验 所采用的 ABCD3TA 芯片<sup>[6]</sup>等。中国兰州重离子加速 器冷却储存环 (HIRFL-CSR) 外靶实验终端 (ETF) 大 型探测系统中,硅微条阵列探测器的前端电子学系统 也采用基于 ASIC 芯片 (ATHED) 的方式。本文将介 绍利用 ATHED 芯片设计的前端电子学模块。

## 2 硅微条探测器阵列

CSR 外靶硅微条阵列探测器阵列包含 12 个望远镜单元,其结构如图 1(a) 所示,每个单元由两块双面硅微条探测器组成;图 1(b) 是单个望远镜单元的双面

图 1 (在线彩图) 硅微条阵列探测器

收稿日期: 2014-01-16; 修改日期: 2014-02-21

基金项目: 国家自然科学基金(11005135, 11079045); 中国科学院知识创新工程重大项目(KJCX2-YW-N27); 中国科学院近代物理

研究所所长基金(Y207170SZ0)

作者简介: 赵兴文(1987-), 男, 山东泰安人, 博士研究生, 从事核电子学研究; E-mail: zwl1671@163.com

通信作者: 苏弘, E-mail: suhong@impcas.ac.cn。

硅微条探测器实物图,其灵敏面积为 50 mm×50 mm, P面和 N 面都由相互平行、宽度相等的 96 条硅条组成,每一条硅条的规格为450 μm×48 mm,厚度为 300 μm,相邻条间间距为 50 μm,均为双面读出<sup>[7]</sup>。每面分为 96 条,因此每个单元共有 384 路输出,CSR 外靶硅微条阵列探测器总计电子学路数为 4 608 路。

硅微条探测器工作原理: 当带电粒子穿过或被阻止在硅微条探测器的耗尽区时,该粒子在硅条中损失的能量会产生电子-空穴对,所产生的电子-空穴对数量与损失的能量成正比。在电场作用下,这些产生的电子和空穴分别向硅条的背电极和前电极运动,电极上的收集信号即反映了粒子能损的信息,且每一条硅条均可视为一个独立的探测器,从而给出入射粒子的能量信息和位置信息<sup>[8]</sup>。

### 3 前端电子学模块

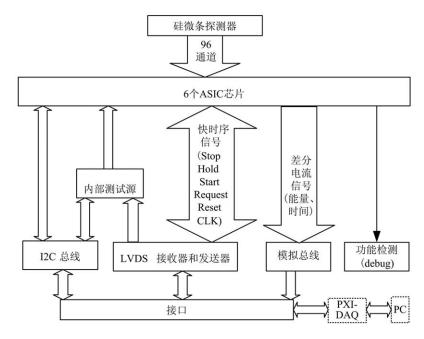

由于探测器机械尺寸的限制,CSR外靶实验要求前端电子学模块电路板宽55 mm,长度在250 mm 以内;由于双面硅微条单面输出96路信号,即要求电子学模块单板可以处理96路信号;为了实现 A ≤ 10粒子的鉴别,要求电子学分辨好于2%。为了满足CSR外靶实验的要求,设计了相应的前端电子学模块(长235 mm,宽55 mm),其作用就是处理硅微条探测器输出的携带入射粒子能量等信息的信号。如图2所示,前端电子学模块主要由6片16通道的ASIC芯片构成,另外它还包括测试模块、LVDS收发模块、输出模块、I2C模块和检测模块。硅微条探测器单面的96路信号,只需一块前端电路板

图 2 前端电路板框图

就可处理,获得的96路能量信息通过模拟总线以差分电流信号的形式输送到PXI-DAQ采集板,经PXI-DAQ采集板处理后,数据保存到上位机以便进行离线分析。

### 3.1 ASIC 芯片

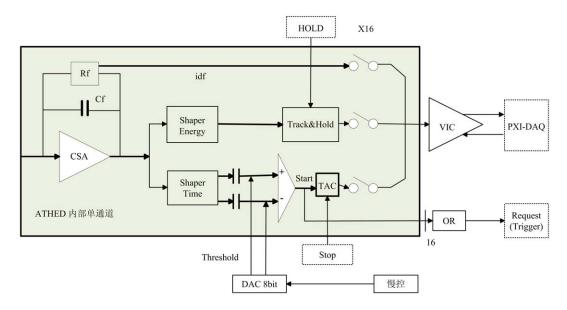

此前端电路板中所使用的ASIC 芯片是由法国 Saclay 设计的16通道ATHED 芯片。该ASIC 芯片每 个通道可处理三种类型的模拟信号:飞行时间信号、 能量信号以及探测器的直流漏电流。ATHED 芯片单 个通道的内部结构框图如图3所示<sup>[9]</sup>,按信号流方向,首先是一个电荷灵敏前放(CSA),主要完成对探测器输出的正负极性电荷的收集。经过CSA后,信号分为两路:一路信号送到能量测量路中,它包括主放(用于信号的放大成形)和Track&Hold电路(用于单路能量信号的保持和输出);另外一路是送到时间测量路中,它包括快成形电路、双阈差分甄别电路(当信号超过阈值时送出 start 信号)和时幅转换电路(TAC)。ATHED芯片16个通道给出的Start 信号经过"或"运算,输出 request 信号,此信号可作为

http://www.npr.ac.cn

事件触发信号。单通道能量信号和时间信号经过一个 多路复用器在外围快时钟控制下(时钟上升沿输出能量信号,时钟下降沿输出时间信号),输出到电压电流转换电路(VIC)。16通道的能量信号和时间信号需 要经过16个时钟周期依次输出到VIC,最后以时分复用方式输出差分电流信号。另外,ASIC芯片内部集成了基于I2C的慢控总线接口,用于芯片内部参数的控制。

图 3 ATHED 芯片单个通道的内部结构框图

### 3.2 输出模块

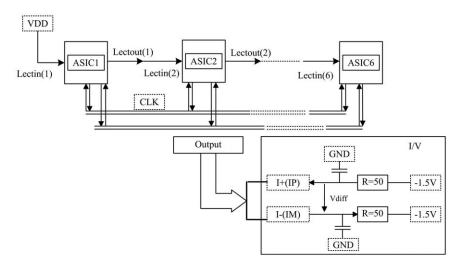

如图4所示,前端电路板的输出信号,通过模拟总线以时分复用方式输出给PXI-DAQ采集板,经过电流电压转换(I/V)、滤波和放大后进入ADC。前端板上的6片ASIC芯片被接成菊花链形式,Lectin和Lectout作为一对信牌令信号。当某个ASIC芯片的Lectin信号被激活后(高电平),当前ASIC芯片会独占模拟总线(其它ASIC芯片处于

等待状态),并且在外围快时钟控制下依次输出16个通道的能量信号和时间信号,完成所有信号的输出后,当前ASIC 芯片会拉高自身的Lectout 信号以释放模拟总线,同时Lectout 信号会激活下个ASIC 芯片的Lectin 信号,这样下个ASIC 芯片便获得了模拟总线的控制权,同样地完成模拟信号的输出。周而复始,各个ASIC 芯片会依照自己在菊花链中的顺序,依次完成模拟信号的输出。6片 ASIC 芯片完成数据依次读出的最小时间小于61 µs。

图 4 前端板 6片 ATHED 芯片信号输出示意图 http://www.npr.ac.cn

#### 3.3 其它模块

测试模块:包括内部测试模块和外部测试模块。 内部测试模块利用板上测试源为6片ASIC芯片的 每个通道提供测试信号,用于系统测试。内部测 试模块由基于I2C总线的I/O扩展器(PCA9555)和 数模转换模块(DAC)组成。可以通过I2C总线来控 制PCA9555的输出,进而改变DAC输出,以达到改 变测试信号幅度的目的。外部测试模块利用脉冲信 号发生器为6片ASIC芯片的每个通道提供脉冲信号, 用于系统刻度。

LVDS 收发模块:包括快时序控制模块和触发输 出模块。快时序控制模块为前端 ASIC 的正常工作和 模拟信号输出提供必要的外围快时序信号, 其快时 序信号由 PXI-DAQ 板产生, 转化为 LVDS 信号进行 传输,以减少干扰。触发输出模块通过LVDS 收发 器将 request 信号传输给 PXI-DAQ, 以便进行数据采 集。

I2C 慢控模块:基于 I2C 总线的慢控模块可以用 来对前端ASIC芯片的各种内部参数进行配置,以实 现对ASIC的远程控制。我们所选用的ASIC芯片的 地址分配采用的是动态分配方式,所以在I2C总线 的基础上还要添加一根辅助控制信号线 chain, 所有 的ASIC芯片被连成菊花链形式。内部测试模块输出

的测试信号的参数也由 I2C 慢控模块进行配置。

检测模块: 主要用来检测 ASIC 芯片的工作状态。 通过对 ASIC 芯片 debug 输出的监控,确定 ASIC 芯 片是否工作正常。通过改变参数设置, debug 可以分 别输出 CSA 输出信号、能量输出信号以及差分阈值 输出信号。在示波器上观察 debug 输出的信号波形是 否正常,来判断芯片工作是否正常。

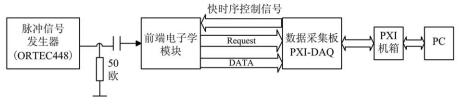

#### 电子学测试 4

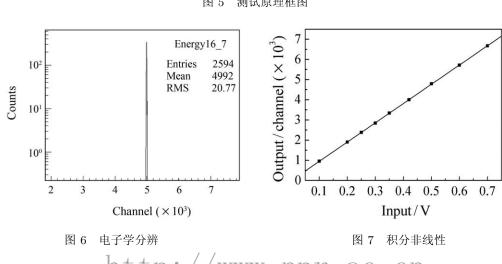

测试原理如图 5 所示,脉冲发生器 (ORTEC448) 输出的电压脉冲信号,送入前端电路板的测试输入 端,模拟输入信号。利用 ASIC 芯片产生的 Request 信号,作为数字板PXI-DAQ(PXI-DAQ 读出板是我 们为硅微条阵列探测器专门开发设计的)的触发信号, 触发数字板 PXI-DAQ 产生快时序信号 (Stop, Hold, Reset, Clk), 并提供给前端电路板; 同时数字板 PXI-DAQ完成对前端电路板各通道输出信号的采集。对 采集的数据在Root 软件下进行分析即可以得到信号 能谱。由图6所给出的能谱可以看出,电子学分辨好 于0.45%。设定脉冲发生器输出最大幅度为0.7 V,采 集得到能谱;不断衰减脉冲发生器的输出幅度,分别 采集, 直到最小输出幅度为0.1 V, 利用所得到的各 个能谱的中心值和输入信号进行线性 拟合,得到图7

图 5 测试原理框图

http://www.npr.ac.cn

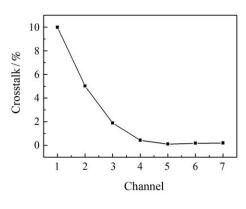

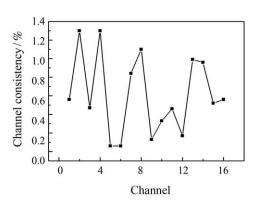

所示的量程在 0.1~0.7 V 时的积分非线性,其结果好于 0.3%。我们对电路板的串扰也进行了测试,只给一个通道输入信号,测试其相邻通道的信号大小,即可得到串扰大小,结果如图 8 所示,最大串扰小于 10%。我们还对各通道一致性进行了测试,分别向 16 通道的输入端输入幅度相同的信号,并进行采集,分析采

图 8 串扰测试

### 5 结论

本文介绍了为HIRFL-CSR 外靶系统硅微条阵列 探测器所设计的前端电路板。此前端电路板的设计采 用了先进的 ASIC 芯片,集成度高,单个板即可以实 现96路信号的测量,满足当前实验要求,该电路板 已应用于硅微条测量[7]。我们还在前端电路板上设计 了测试模块和检测模块,以确保前端电路板的工作正 常稳定。对前端电路板进行了电子学测试。测试结果 表明,该前端电路板在0.1~0.7 V范围内的积分非 线性好于0.3%, 电子学分辨好于0.45%, 最大串扰小 于10%,通道一致性测试结果好于1.3%,在室温下连 续工作24 h后,零点峰位最大漂移为1.48 mV。由于 探测器机械尺寸的要求, 电路板布局很密, 输入排针 也选择的是1.27 mm间距的表贴排针,通道间串扰相 对较大。由于噪声对粒子鉴别有很大的影响,这需要 我们进一步优化设计,降低噪声,以便提高系统的粒 子鉴别能力。

### 参考文献:

QIAN Yi, SU Hong, KONG Jie, et al. Chinese Physics C, 2013, 37(1): 016101. 集到的能谱,得到峰位,求出各通道峰位与平均峰位的比值,如图 9 所示,各通道一致性测试结果最大偏移小于 1.3%。对电路板长时间工作稳定性进行测试,电路板在室温下连续工作 24 h 后,零点峰位最大漂移为 1.48 mV。

图 9 通道一致性

- [2] LI Zhankui, GONG Wei, TAN Jilian, et al. Nuclear Physiscs Review, 2011, 28(3): 305. (in Chinese)(李占奎, 巩伟, 谭继廉, 等. 原子核物理评论, 2011, 28(3): 305.)

- [3] MONTAÑO L M. AIP Conference Proceedings, 2006, **857**: 143.

- [4] QIAN Yi, SU Hong, KONG Jie, et al. Nuclear Techniques, 2009, 9: 015. (in Chinese)(千奕, 苏弘, 孔洁, 等. 核技术, 2009, 9: 015.)

- [5] RAYMOND M, CERVELLI G, FRENCH M, et al. Sixth Workshop on Electronics for LHC Experiments, CERN/LHCC/2000-041.

- [6] CAMPABADAL F, FLETA C, KEY M, et al. Nucl Instrum and Meth A, 2005, 552(3): 292.

- [7] WANG Pengfei, LI Zhankui, LI Haixia, et al. Nuclear Physics Review, 2014, 31(1): 63. (in Chinese)

(汪鹏飞, 李占奎, 李海霞, 等. 原子核物理评论, 2014, 31(1): 63)

- [8] QIAN Yi, SU Hong, XU Sijiu, et al. Nuclear Techniques, 2008, 31(3): 229. (in Chinese)(千奕, 苏弘, 徐四九, 等. 核技术, 2008, 31(3): 229.)

- [9] BARON P, ATKIN E, BLUMENFELD Y, et al. MATE, Nuclear Science Symposium Conference Record, IEEE, 2003, 1: 386.

# Development of a Multi-channel Front-end Electronics Module based on ASIC for Silicon Strip Array Detectors

ZHAO Xingwen<sup>1,2</sup>, SU Hong, QIAN Yi<sup>1</sup>, KONG Jie<sup>1</sup>, ZHANG Xueheng<sup>1</sup>, YAN Duo<sup>1,2</sup>, LI Zhan kui<sup>1</sup>, LI Haixia<sup>1</sup>

(1. Institute of Modern Physics, Chinese Academy of Sciences, Lanzhou 730000, China;

2. University of Chinese Academy of Sciences, Beijing 100049, China)

**Abstract:** The silicon strip array detector is one of external target facility subsystems in the Cooling Storage Ring on the Heavy Ion Research Facility at Lanzhou (HIRFL-CSR). Using the ASICs, the front-end electronics module has been developed for the silicon strip array detectors and can implement measurement of energy of 96 channels. The performance of the front-end electronics module has been tested. The energy linearity of the front-end electronics module is better than 0.3% for the dynamic range of  $0.1 \sim 0.7$  V. The energy resolution is better than 0.45%. The maximum channel crosstalk is better than 10%. The channel consistency is better than 1.3%. After continuously working for 24 h at room temperature, the maximum drift of the zero-peak is 1.48 mV.

Key words: front-end electronics; silicon strip array detector; ASIC

Received date: 16 Jan. 2014; Revised date: 21 Feb. 2014

Foundation item: National Natural Science Foundation of China(11005135, 11079045); Knowledge Innovation Program of Chinese Academy Sciences(KJCX2-YW-N27); Foundation of Director of Institute Modern Physics, Chinese Academy of Sciences(Y207170SZ0)

Corresponding author: SU Hong, E-mail: suhong@impcas.ac.cn.