-

兰州重离子研究装置(Heavy Ion Research Facility in Lanzhou, HIRFL),强流重离子加速器装置(High Intensity Heavy-ion Accelerator Facility, HIAF)分别是国家“九五”与“十二五”计划重点工程[1-2],束流位置探测与反馈是束流调试的重要手段之一。

束流位置探测器(Beam Position Monitor, BPM)极板在束流经过时产生感应信号,信号经过数十米的电缆传输至数字采集系统[3-5]。考虑到束团粒子纵向近似为高斯分布,对探针引出信号傅里叶变换频域展开有n次谐波,为在最大化还原信号的同时减小计算量,前置放大器的通频带至少将0~15次谐波包含在内,即通频带大于等于0.1~30.0 MHz。束流流强最小为μA量级,BPM等效传输阻抗约百Ω以下,要使最小感应信号放大后能够达到数字采集系统的最小分辨率50 mV,放大器增益设计指标为30 dB,此外放大器输出阻抗50 Ω与负载的输入阻抗50 Ω会对信号等幅平分,故放大器增益设计指标为36 dB。综合BPM极板探测的灵敏度与放大电路信噪比,输入电压噪声密度须小于等于1 nV/

$ \sqrt{\mathrm{H}\mathrm{z}} $ 。国内外已有许多低噪声放大器的研究与设计,2021年海军工程大学设计出一款低噪声前置放大器,截止频率1 MHz,输入电压噪声密度0.99 nV/

$ \sqrt{\mathrm{H}\mathrm{z}} $ [6]。调研发现,低噪声放大器在低频领域的研究相较于高频极少,且高频及以下频域内低噪声高阻宽带放大器的设计难度极高[7-11]。2017年欧洲核子研究中心设计了输入电压噪声密度为0.44 nV/$ \sqrt{\mathrm{H}\mathrm{z}} $ ,带宽200 Hz~75 MHz的低噪声放大器,但其1/f 噪声拐点约为1 MHz相对较大[12];德国Stahl公司一款商用超低噪声放大器采用第一级低噪声结型场效应管共源极放大和第二级运算放大器的结构,输入阻抗300 MΩ,0.5 kHz~49.0 MHz带宽内输入电压噪声密度为0.85 nV/$ \sqrt{\mathrm{H}\mathrm{z}} $ ,增益42 dB,但 ±5%的带内平坦度误差较大。本文拟设计一款基于低噪声N-JFET的电荷灵敏前置放大器,用以解决微弱信号难以数字化处理的难题,为重离子加速器的建设提供硬件支持,有望在HIAF建设中发挥重要作用。

-

晶体管是设计放大电路时必不可少且极其重要的元器件,其通过控制较小的电压或电流实现放大。由于单极放大电路无法同时满足输入高阻、宽带以及高输出功率的需求,多级放大电路由输入级、中间级和输出级组成,通常输入级具有输入阻抗高和噪声低的特性;中间级有较大的电压放大倍数;输出级有输出阻抗低和输出功率大的特点,故多级放大电路结构因其每级可实现不同功能的优势被采用。

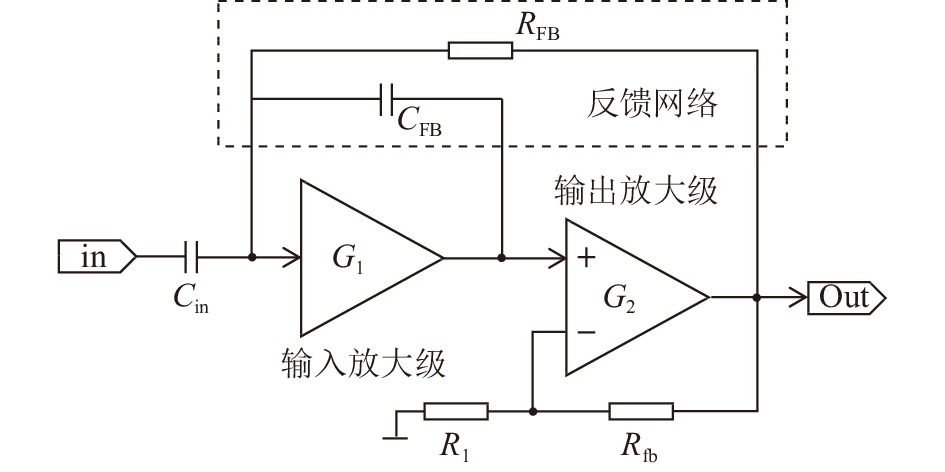

本设计的多级放大电路结构如图1所示,其中,输入放大级包括共源共栅、源极跟随、集电极负反馈恒流源;输出放大级是同相运算放大器;反馈网络以无源器件电容、电阻组成。

-

场效应晶体管是电压控制型器件,输入电阻大(百M~G量级),且参与导电的只有多子,管中受温度、辐射影响较大的少子不参与导电,故在低噪声高阻放大器输入级设计中,场效应管在稳定性、噪声和输入阻抗等方面都具有显著的优势。场效应晶体管主要分为金属-氧化物半导体场效应晶体管(MOSFET)、结型场效应晶体管(JFET)两大类,其中JFET的噪声性能和对于静电放电的抵抗力均优于MOSFET,故选择JFET作为输入级放大器件。

常见的JFET低噪声放大结构有共源、共源共栅。但密勒效应的存在使共源极结构的输入电容变大,进而带宽受限[13],共源共栅结构可以减小输入电容从而减小这种限制,且为了突破低噪声放大器的低频带宽,共源共栅结构的高增益、屏蔽特性等优点更适合被应用在本设计中[14]。源极跟随用作缓冲器时可以屏蔽后级放大对前级放大的影响,此外参考文献[15]中比较了共源极、共源共栅+源极跟随两种结构作为输入级放大时的性能,如表1所列,再次证明了共源共栅+源极跟随的结构作为输入级时带宽更大、噪声更小,与设计初衷相符。

电路结构 增益/dB 带宽/Hz 1/f 拐点/Hz 输入电压噪声

密度/(nV/$ \sqrt{\mathrm{H}\mathrm{z}} $)共源极 20.00 10 ~1 M 3 k 0.25 共源共栅+源极跟随 27.96 500 ~20 M 30 k 0.17 -

晶体管组成的放大电路内部噪声来源主要为与频率有关的1/f 噪声、与温度等因素相关的热噪声和散粒噪声。1/f 主要影响低频的噪声性能,而热噪声和散粒噪声一直存在,当1/f 噪声随频率增加逐渐减小时热噪声和散粒噪声在噪声性能中占主导地位[16]。

多级放大电路中,电路的输入噪声水平几乎由第一级决定,每级的占比具体由式(1)给出:

其中:NFn为第n级放大电路的噪声系数,An为第n级放大电路的增益。由该式可以看出,从第2级开始,每级放大电路对整体噪声的影响都被前级增益乘积减小,若想减小电路整体噪声,第一级放大电路的增益尽量大的同时噪声水平尽量小,即输入级JFET放大要选择恰当的静态电压、电流值以使增益最大、输入噪声最小。

JFET输入电压噪声密度的平方反比于JFET的跨导gm,而gm在一定范围内与漏源极电流IDS呈正相关,可通过调大输入级JFET的IDS来降低电路的噪声。但当IDS增大到一定程度后,温度、PN结等限制因素又会导致噪声增大。

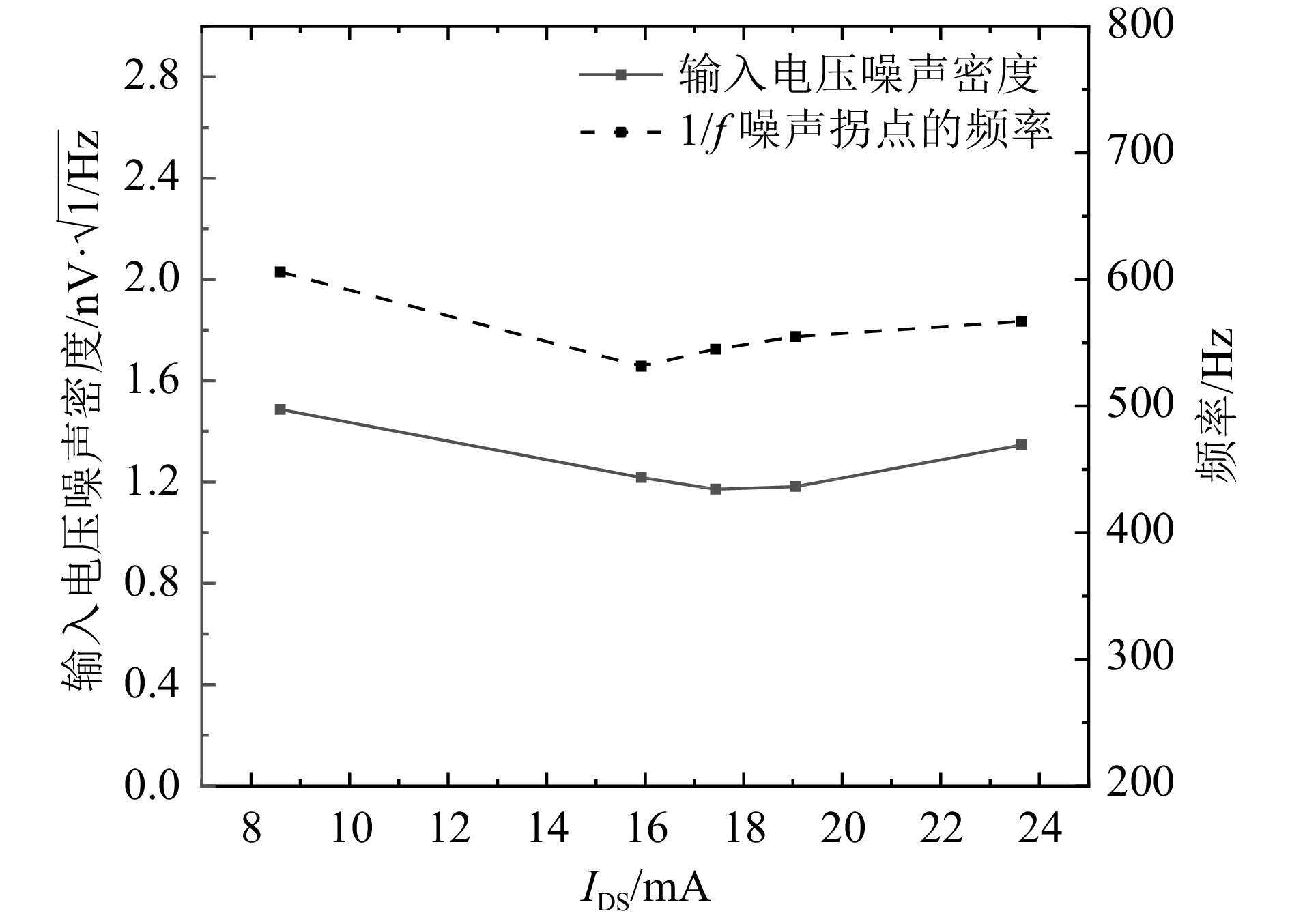

本设计综合考虑晶体管噪声性能等因素后,选定N沟道结型场效应管BF862为输入级,将2级BF862并联于本设计电路的输入级,改变IDS,利用RS-FSW43频谱仪测量电路的噪声性能,在频率为1 MHz时如图2所示。本设计通频带包括低频100 kHz,1/f 噪声的拐点频率应尽量小,故在图2内定性比较折中选择IDS约为16 mA。

一定范围内,N 个子电路并联可使总输入电压噪声密度为单路子电路电压噪声密度的1/

$ \sqrt{N} $ 倍,所以输入级JFET可采取多级并联的方式降低输入噪声。根据信噪比的定义,提高信噪比需减小输出电压噪声,输出电压噪声密度VNout计算公式如式(2)所示,当N ≈ 2时,VNout取最小值,此时信噪比最大。故放大器输入级设计为两级JFET并联:其中:G2为输出级同相运算放大器的增益;k为玻尔兹曼常数1.38×10-23 J/K;T为温度;N、CJ分别为JFET并联个数、输入电容;CFB、Cin分别是放大电路反馈电容、输入电容,CS为极板电容与电缆电容之和。

-

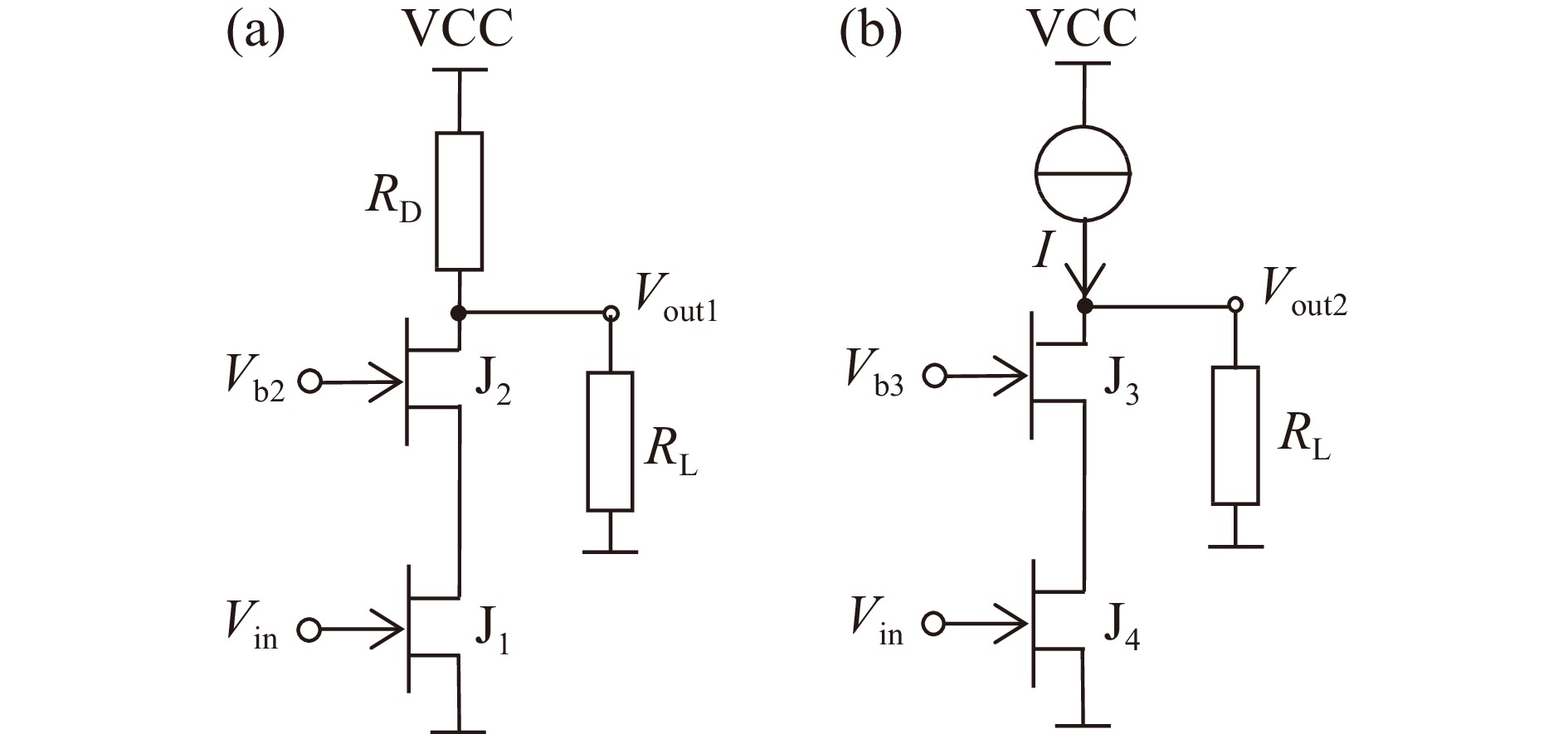

放大电路引入负反馈会提高稳定性,但负反馈的引入会牺牲增益(详细论述见本文1.2节),故只有开环增益足够大,才能满足闭环增益。理想电流源的等效内阻为无穷大,晶体管基础共源共栅结构电路如图3(a)所示,其中RL是共源共栅结构输出端负载等效电阻,J1管的漏源极电流IDS经过J2管流向RD和RL。图4为该电路小信号模型,共源共栅结构的放大倍数AV1可由式(3)表示:

在共源共栅结构中,使负载不变时获得最大增益,用电流源替代RD[图3(b)],因为在基础共源共栅结构中可近似看做RD=∞,则RD与RL并联约等于RL的值,此时在不改变RL阻值的情况下,AV最大。

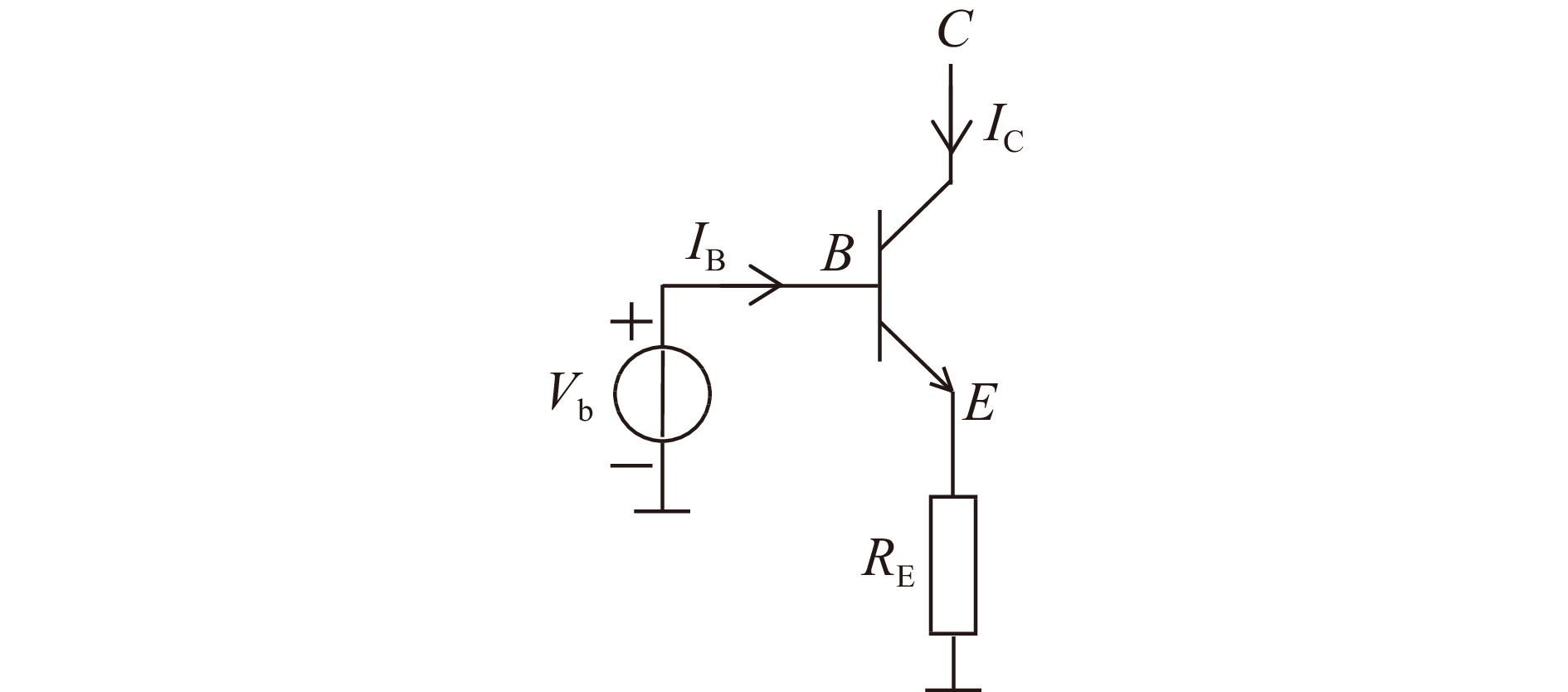

NPN三极管组成的恒流源电路如图5所示,由三极管的输出特性曲线可知,VCE对IC的影响可忽略不计,且VBE为固定值。当VB固定时,调整RE的值就可得到相应的IC,这种恒流源电流可控、操作简单、成本低。

-

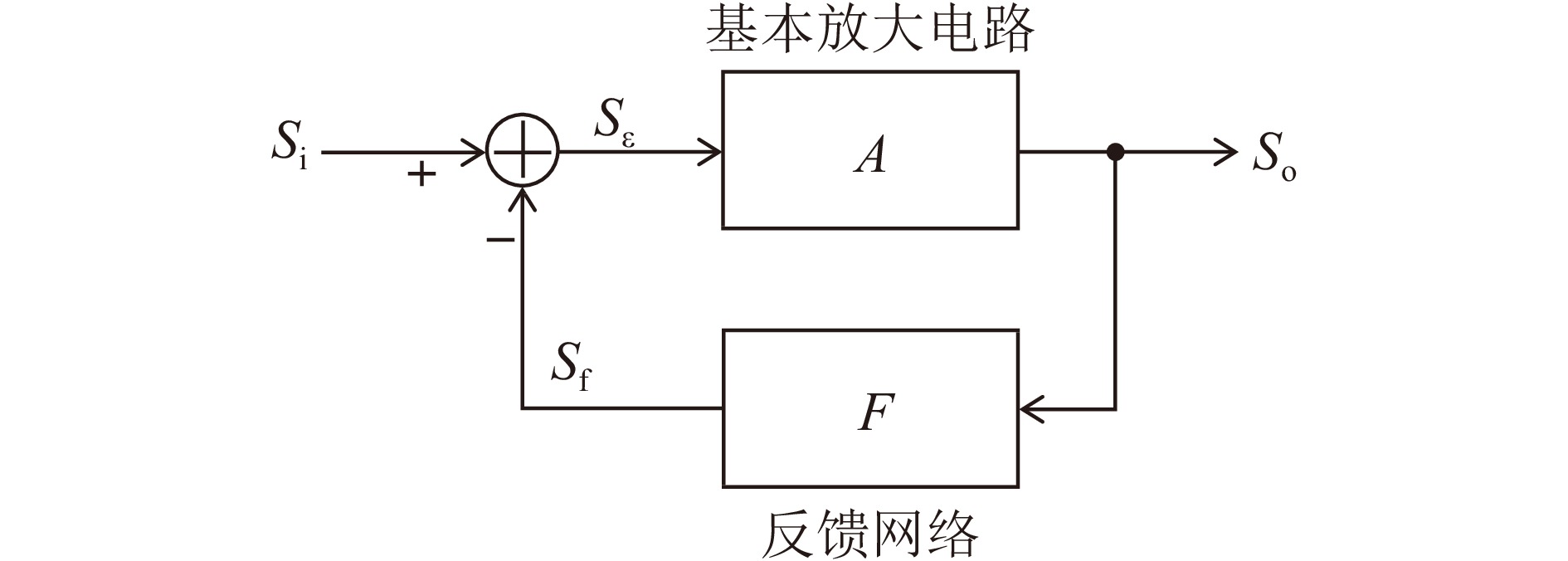

在放大电路中,通常将输出电流或电压连接到输入端构成反馈网络,正负反馈电流或电压信号会对输入信号产生增大或减小的影响。

如图6所示,系统的增益为A,反馈系数为F,引入负反馈后,系统的增益以及稳定性由下式表示:

其中:由式(4)可以看出,引入负反馈后增益减小为原来的1/(1+AF),但由式(5)可以看出稳定性增大为原来的1+AF倍。故引入反馈会在牺牲增益的同时提高系统的稳定性。

传统的负反馈是将电容与电阻并联在输入级放大的输入端与输出端之间,但通常会在两级放大之间插入极零相消电路以减小放大前的时间常数,否则高计数率下的脉冲堆积非常容易使输出电压饱和[17]。图1所示的阻容反馈网络在不插入极零相消电路的情况下提高了电压对电荷的灵敏度,没有额外显著增加噪声的同时提高了放电时间,避免了极零相消电路引进奇异点的风险。

-

输出级运算放大器选择电流反馈型运算放大器,其带宽较大(百MHz级),且相较于电压反馈型放大器受增益带宽乘积限制而言,电流反馈型放大器带宽主要受反馈电阻的控制,增益对带宽的影响小。同时THS3091的7 000 V/μs高转换率、180 mA高输出电流确保了高输出功率。输出级同时还需要阻抗匹配,当输出特征电阻与传输电缆的特征电阻相等时,噪声达到最小,传输功率达到最大[18]。

同相放大器的增益G2为

反馈电阻Rfb决定该放大器带宽,设计过程中根据数据手册选择Rfb,再根据增益需求确定电阻R1的阻值。

-

确定电路结构后对其进行分析,得出电路参数的理论表达式,调整电路中电阻电容的值,使放大电路的静态工作点稳定且输出端口的直流偏置趋近于0 V,输入阻抗、增益、带宽达到设计指标。设计完成后利用示波器、网络分析仪、频谱仪等测量仪器对该电路时域、频域和噪声性能进行测量与调试。

-

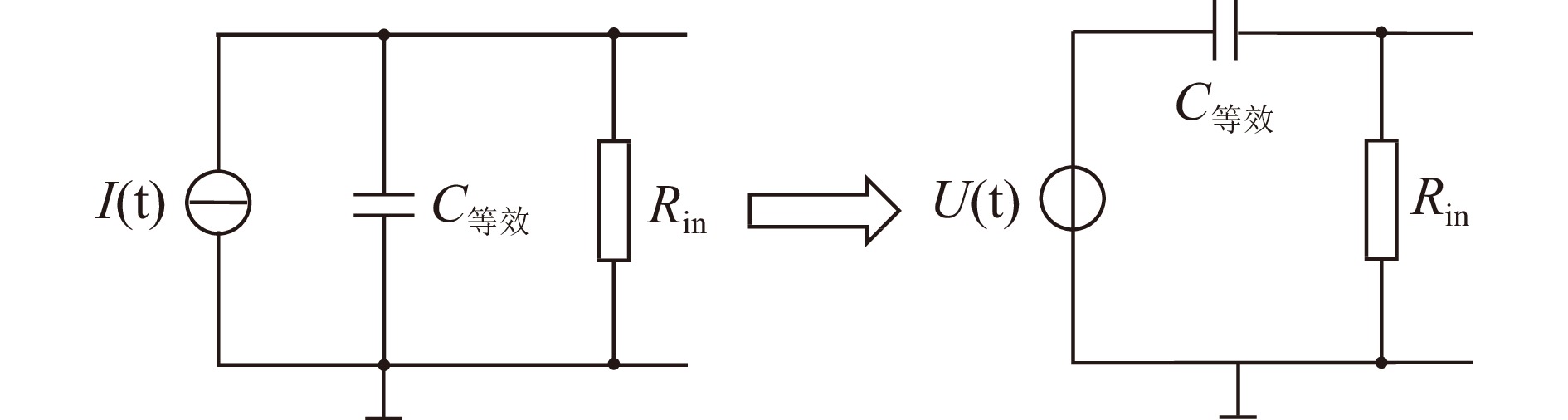

在实际应用时,放大器输入阻抗R,极板电容、电缆电容之和CS与放大器输入电容Cin叠加的等效电容C等效,感应电荷等效的电流源I(t)三者并联接地,根据戴维南定理该电路也可等效为接地电压源U(t)与Rin、C等效组成的高通滤波器的串联,如图7所示。

为了方便测试及分析电路的性能,下文中的增益等均以图7中右图等效电路为参考,即将探测极板的输出信号等效看做电压源,该电压源与感应电荷成正比,与C等效成反比。电路中RC滤波器的截止频率与Rin、C等效成反比,在C等效为pF量级的情况下,放大器输入阻抗为百kΩ及以上量级才能使低频截止频率达到设计指标。

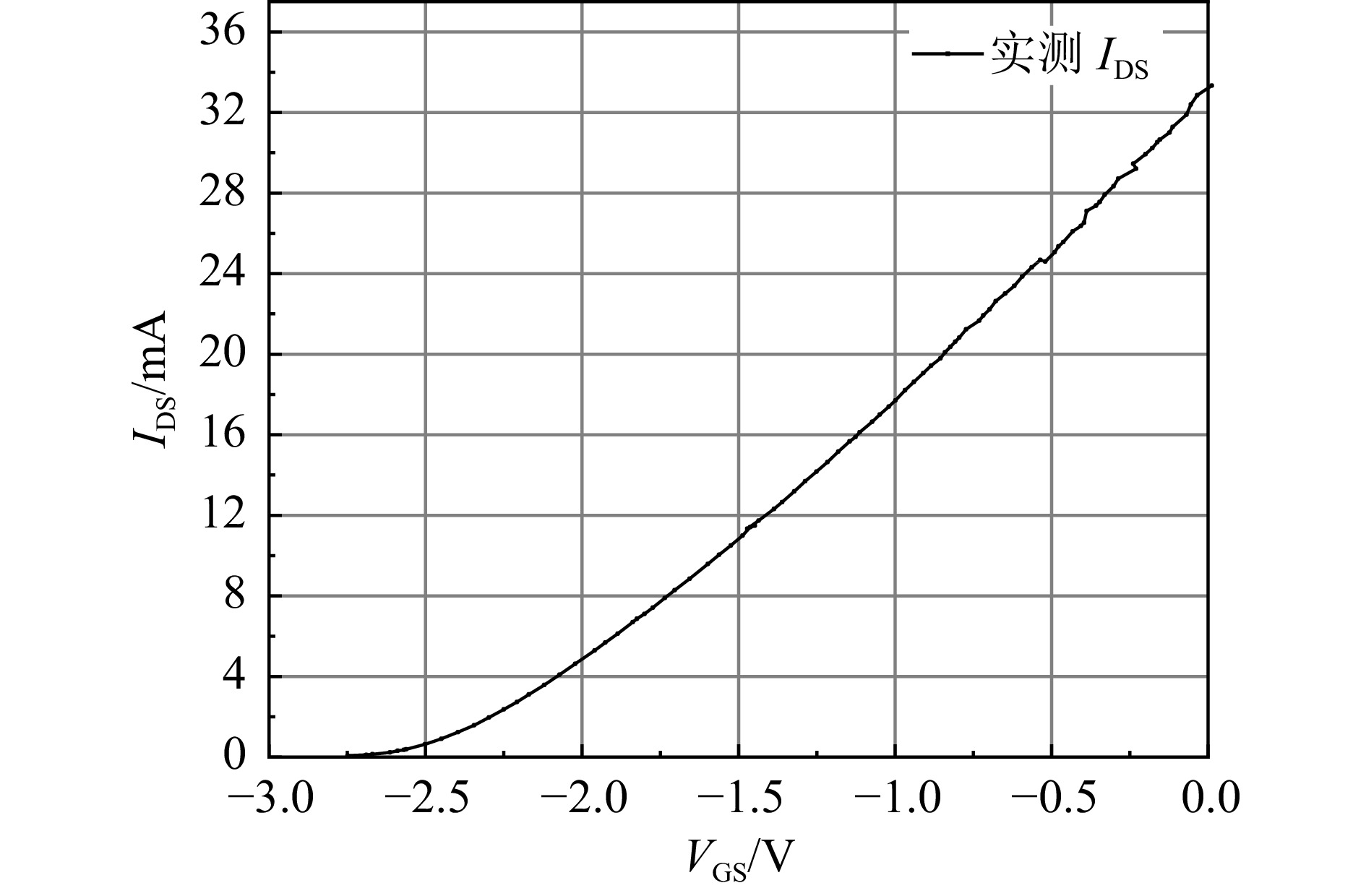

根据N沟道JFET转移特性,静态工作点VGS为负,故本设计中栅极偏置电路由两个电阻对VCC与VEE进行分压。分析电路可知,放大器输入阻抗主要由JFET的栅极偏置电路以及反馈电阻RFB决定,根据共源共栅结构中共栅极晶体管栅极电压的选择确定共源极JFET漏极电压,进而根据图8 VGS-IDS 实测曲线,调整漏极电阻、栅极偏置电路使BF862的IDS约为16 mA,并在相同或更高量级内选择反馈电阻的值[19-20],最终得到放大器的输入电阻。值得注意的是,反馈电阻不能过大,避免引入50 Hz工频噪声影响信号的传输。本设计输入阻抗值为2.37 MΩ。

-

分析输入放大级的电路可知增益计算如式(7)所示:

故在设计电路时调整对应的电容比值可控制放大器的增益,若要考虑放大器输出电压幅度相对于感应电荷的增益GQ,综合等效电压源与C等效的关系可得GQ只与CFB有关,对应了电荷灵敏型放大器的工作特点。

综合多级放大电路的增益计算方法,本文设计的放大电路增益由式(8)所示:

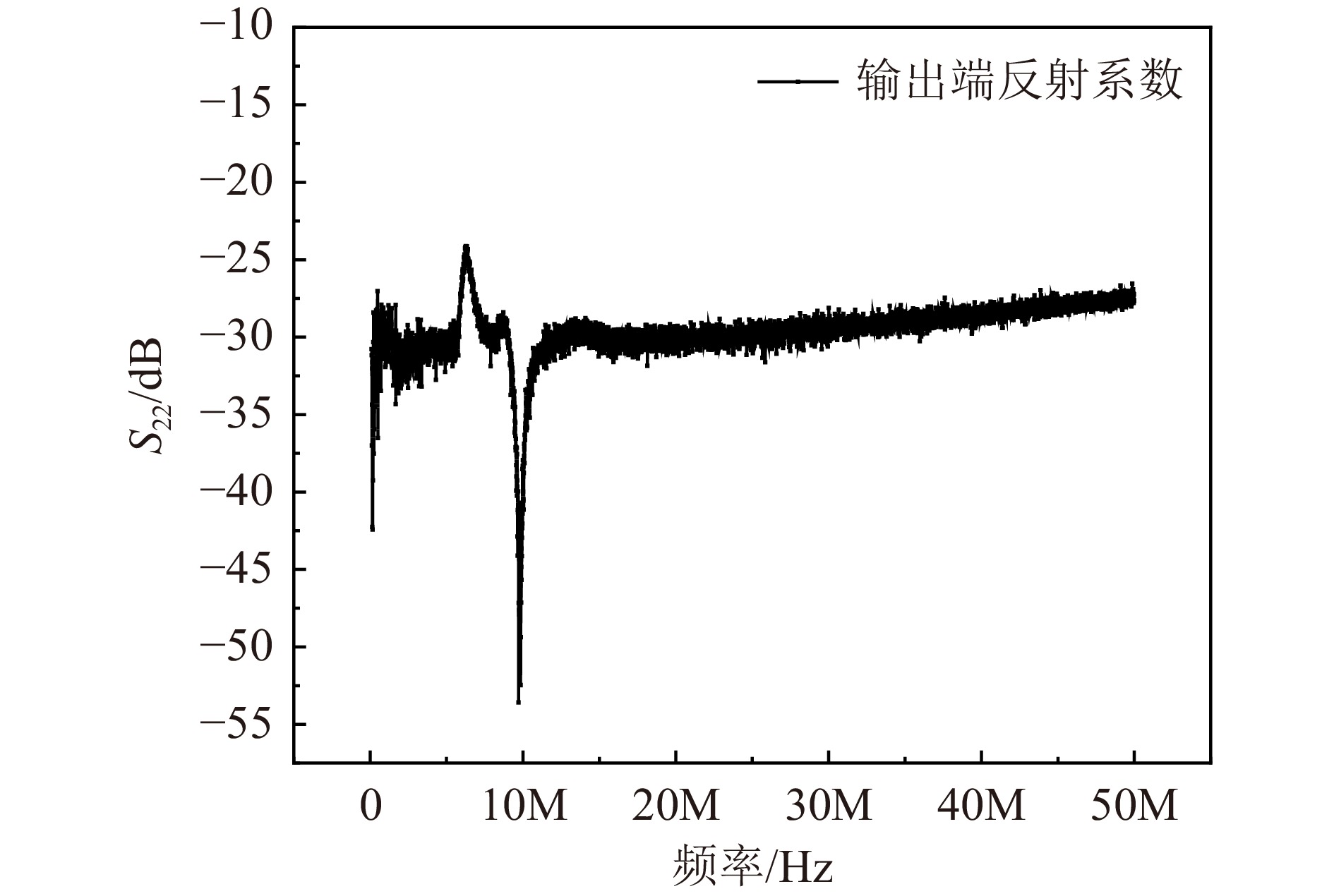

利用Keysight网络分析仪测量放大电路在10 kHz ~ 50 MHz频率范围内的S21、S22,电路的频率响应特性曲线如图9所示,输出端反射系数如图10所示。测试结果显示,放大电路增益为36.2 dB,增益平坦度± 0.3 dB,高频截止频率(−3 dB)约为38.47 MHz,低频截止频率(−3 dB)约为34 kHz,满足设计需求;输出端反射系数 < −24 dB,输出端阻抗匹配效果优异。

-

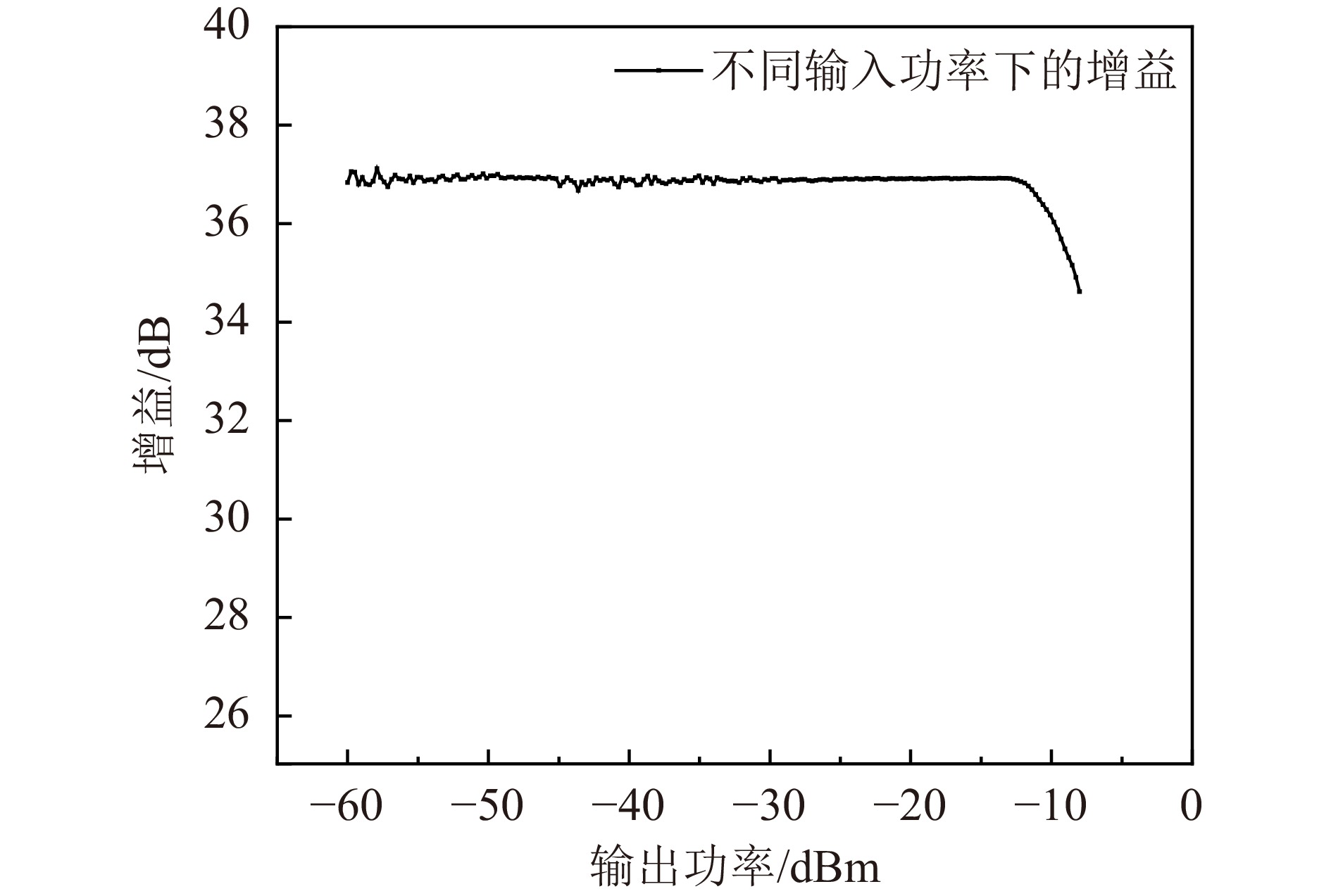

随着输入功率的增加,放大器逐渐进入非线性区,此时输出功率低于预期的线性值,当实际增益下降至比线性增益低1 dB时的输出功率值定义为输出功率的1 dB压缩点(P1dB)。当功率超过P1dB后,放大器增益将迅速下降并达到饱和输出功率[21。

使用网络分析仪测量放大器不同输入功率下的增益如图11所示,增益下降1 dB点处的输入功率约为−10 dBm,则P1dB约为26.2 dBm。

-

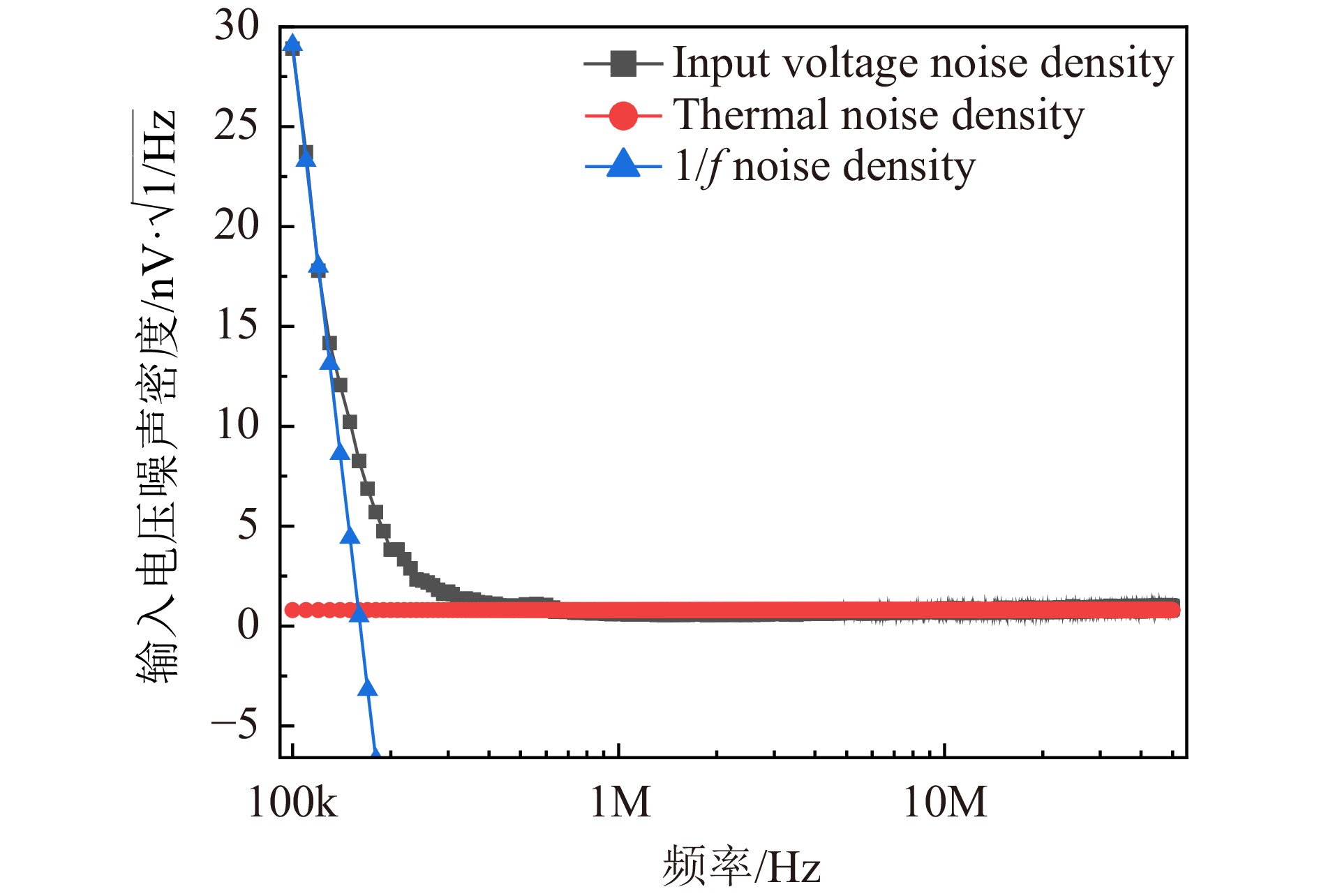

将放大器输入端短路,输出端连接是德科技N9010A频谱仪,扫描频率范围100 kHz~50 MHz,将测得的电压值除以频谱仪的分辨率带宽(10 Hz)的算术平方根和增益的乘积,得到等效输入电压噪声密度曲线,对该曲线的低频区用最小二乘法拟合,可得1/f噪声曲线以及热噪声曲线如图12所示,放大器电路输入噪声密度为0.63 nV/

$ \sqrt{\mathrm{H}\mathrm{z}} $ @1 MHz,0.76 nV/$ \sqrt{\mathrm{H}\mathrm{z}} $ @10 MHz,1/f 噪声拐点约为160.85 kHz。 -

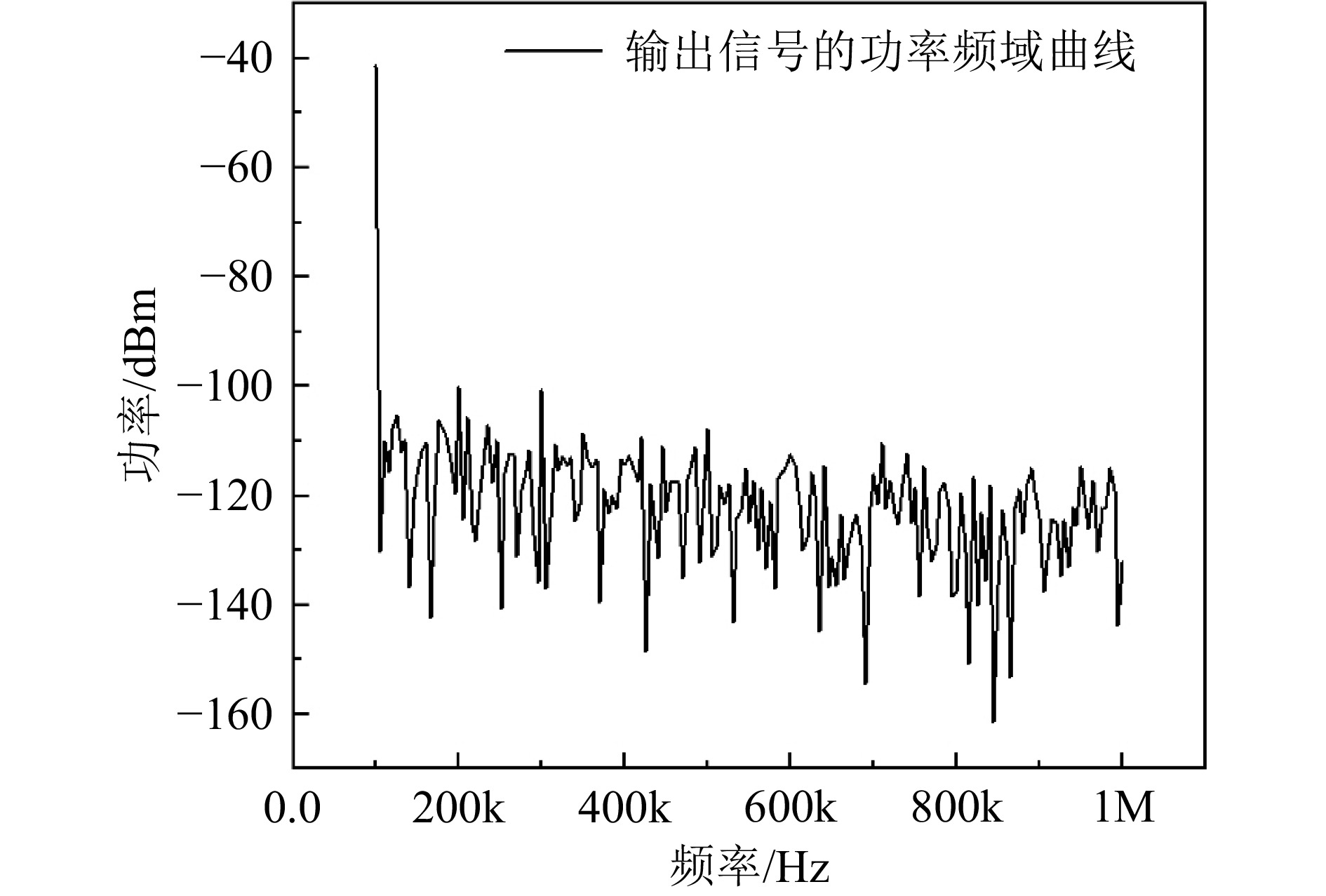

总谐波失真(Total harmonic Distortion, THD)是指信号经过放大器后的输出信号较输入信号产生的额外谐波成分,对放大器输入频率为100 kHz的正弦波,得到输出信号的功率谱如图13所示,根据总谐波失真的计算方法,即各谐波功率有效值的和与基波功率有效值比值的平方根,得到100 kHz时的THD为−55.34 dB。

-

模拟BPM的实际工作环境,将相对的两个极板命名为A、B,A极板连接信号源,B极板连接频谱仪、示波器等测量仪器或高阻放大器输入端,观察B极板感应信号与放大器输出信号,对各放大前后的信号参数进行比较分析。

由于实际极板的感应信号为高斯信号,则向极板A输入2 MHz的高斯信号,观察感应信号经过高阻放大器后输出信号的波形表现,如图14所示;将输出信号反相、时移与缩小后得到如图15所示的波形图,观察发现信号经过放大后可与原始感应信号重合,放大效果良好。

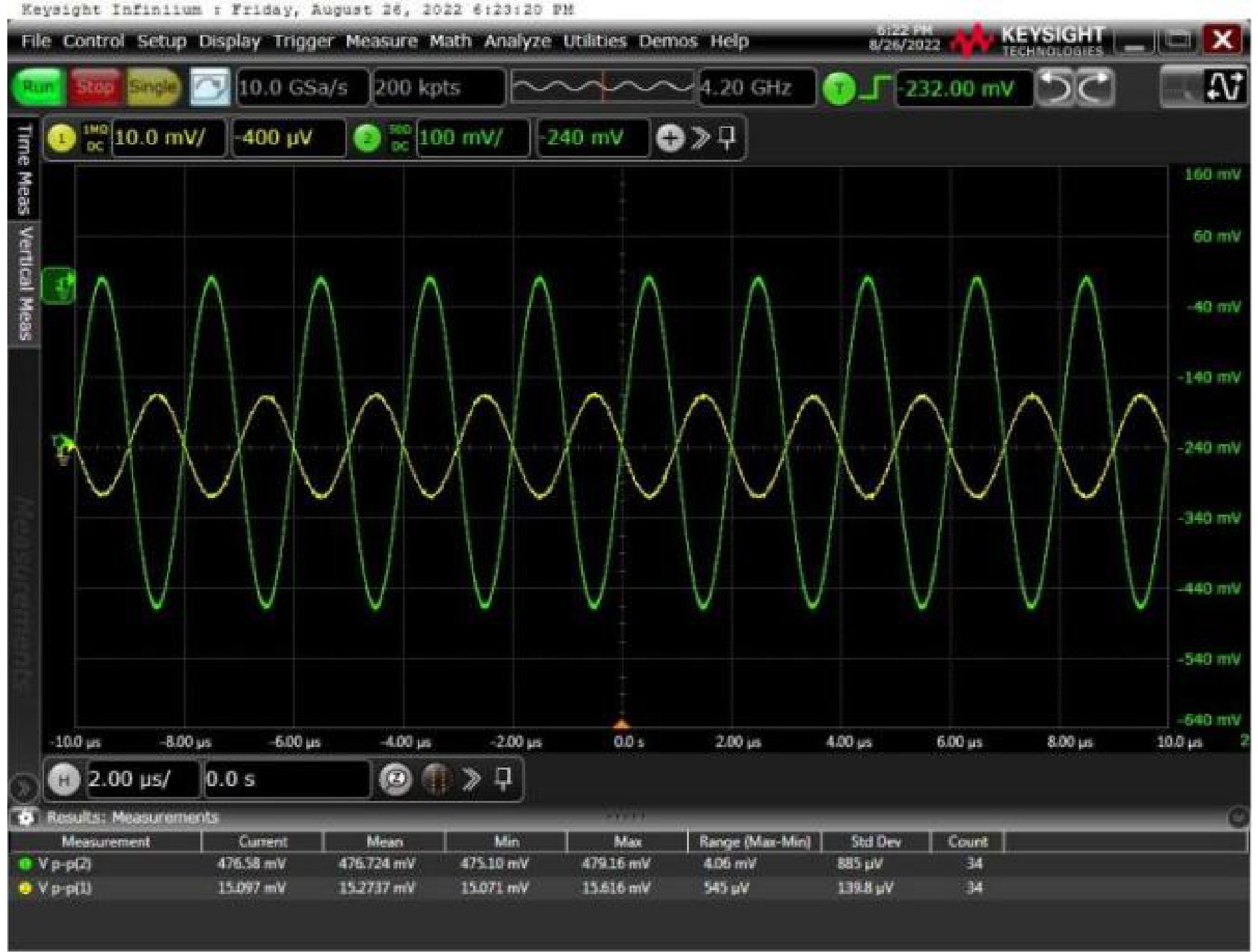

该放大器输出阻抗与负载的输入阻抗均为50 Ω,故实际应用时负载输入端相较于放大器输入端的增益应减小6 dB,即(30.2±0.3) dB,向A极板输入正弦信号,利用示波器观察B极板感应信号与放大器输出信号的幅值(如图16),得到放大器的增益为29.98 dB@500 kHz,符合实验室测试结果。

对A极板输入相同频率(2 MHz)不同幅度的信号,利用频谱仪观察B极板感应信号放大前后是否产生新的谐波。调整信号源的输出功率保持基波的功率相等,比较各谐波的功率,测试结果如表2所列,可知高阻放大器并未产生新的谐波或特别增加某些频率谐波的功率。

信号频率/MHz 2 4 6 8 10 12 感应信号 0 −51.89 −66.57 −74.32 −95.75 −82.54 放大后 0 −53.45 −68.74 −80.14 −101.04 −90.15 通过模拟加速器实际运行情况,对放大器性能进行测试可知放大器实际应用时,各参数性能的表现与实验室的测试结果相符。

-

重离子加速器束流位置探测系统中感应的微弱信号难以数字化处理,本文设计了一款基于N沟道JFET的低噪声高阻宽带前置放大器,文中综合增益、带宽与噪声等性能,考虑了晶体管、运算放大器等器件的参数,对比了不同电路结构的特性及优缺点,表明了电路结构加入设计的目的及意义;利用网络分析仪、频谱仪等对放大器进行实验室测试以及模拟BPM实际工作环境测试,结果显示,设计的放大器相较于国内外高频及以下频域内低噪声放大器的设计,在噪声、平坦度及带宽等方面均有优化,即将于HIRFL上线测试,并有望广泛应用于HIAF的建设。

A JFET Low Noise and High Impedance Wideband Preamplifier for Beam Position Measurement of Heavy Ion Accelerator

doi: 10.11804/NuclPhysRev.40.2022073

- Received Date: 2022-06-28

- Rev Recd Date: 2022-10-20

- Publish Date: 2023-09-20

-

Key words:

- beam position monitor /

- low noise /

- high input impedance /

- N-JFET /

- cascode /

- preamplifier

Abstract: To solve the measurement of the weak coupled signals from beam position monitors in a heavy ion accelerator with low intensity beam, a broad band low noise preamplifier with a high input impedance is designed and developed, which has a broad band response over almost 2 decades of frequency. This design is based on a cascade multistage amplification.The input stage, consisting of 2 folded N-channel junction field effect transistors (N-JFET), adopts a cascade and source following structure to minimize the input voltage noise. A high voltage open-loop gain is obtained by using the characteristic impedance of a constant current source. The output stage is a current mode feedback op-amp which provides a broad band frequency response and enough output power. The whole circuit has a high sensitivity, low noise and distortion. From the measurement, the achieved gain is 36.2 dB with a flatness of less than ±0.3 dB from 34 kHz to 38.47 MHz. The input voltage noise density is 0.76 nV/

| Citation: | Yajie LI, Zhixue LI, Xiaoxuan QIU, Fafu NI, Junxia WU. A JFET Low Noise and High Impedance Wideband Preamplifier for Beam Position Measurement of Heavy Ion Accelerator[J]. Nuclear Physics Review, 2023, 40(3): 426-432. doi: 10.11804/NuclPhysRev.40.2022073 |

甘公网安备 62010202000723号

甘公网安备 62010202000723号 DownLoad:

DownLoad: