-

对撞机是用于高能核物理与粒子物理研究的一种重要装置,中俄联合研究建造的基于超导粒子加速器的离子对撞机(NICA)主要研究高温高密和最大净重子密度的物质及其性质,其中多功能探测谱仪MPD(Multipurpose Detector)主要用于研究重离子碰撞中的热和致密物质的特性。MPD谱仪中内径迹系统(Inner Tracker System, ITS)将采用有源硅像素传感器(Monolithic Active Pixel Sensor, MAPS)构建,其输出通道数多、数据量大,NICA ROC(NICA Readout and Control) ASIC(Application Specific Integrated Circuit)是正在研制的一款用于接收MAPS输出数据并进行汇总和传输的前端专用芯片。它需要接收来自MAPS芯片的400 Mbps LVDS (Low Voltage Differential Signaling)串行输入数据,在原型验证阶段,汇总处理后的数据需通过LVDS标准发送至FPGA(Field Programmable Gate Array)进行性能测试和评估,LVDS发送数据率要求大于800 Mbps。此外,由于NICA ROC ASIC对功耗有严格的要求,LVDS收发器的功耗需要控制在10 mW以内。针对此需求,本文设计了一种基于130 nm CMOS工艺的LVDS高速串行收发器。

-

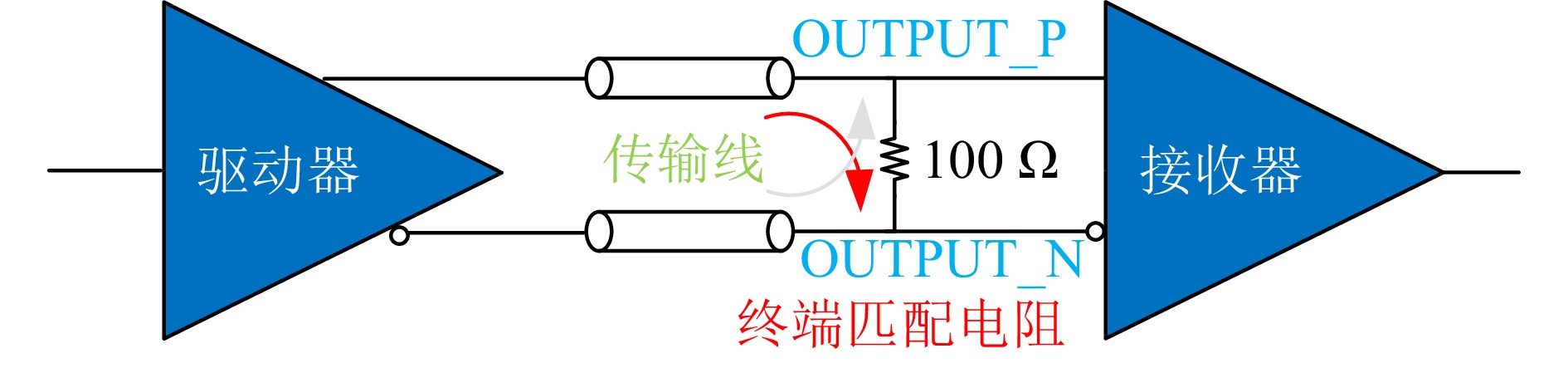

LVDS高速串行接口电路由驱动器(Driver)、接收器(Receiver)以及终端100 Ω匹配电阻组成。LVDS具有高传输速率、低功耗、噪声性能好、成本低等优点,在高速传输系统中用途十分广泛[1]。LVDS的整体结构如图1所示。LVDS具有良好的低噪声性能,当存在系统噪声时,噪声以共模方式耦合到一对差分线上,这些噪声在接收端进行相减,从而使噪声得以消除。LVDS通常以点对点(由一个驱动器、互连介质和一个接收器组成)方式配置使用[2]。

-

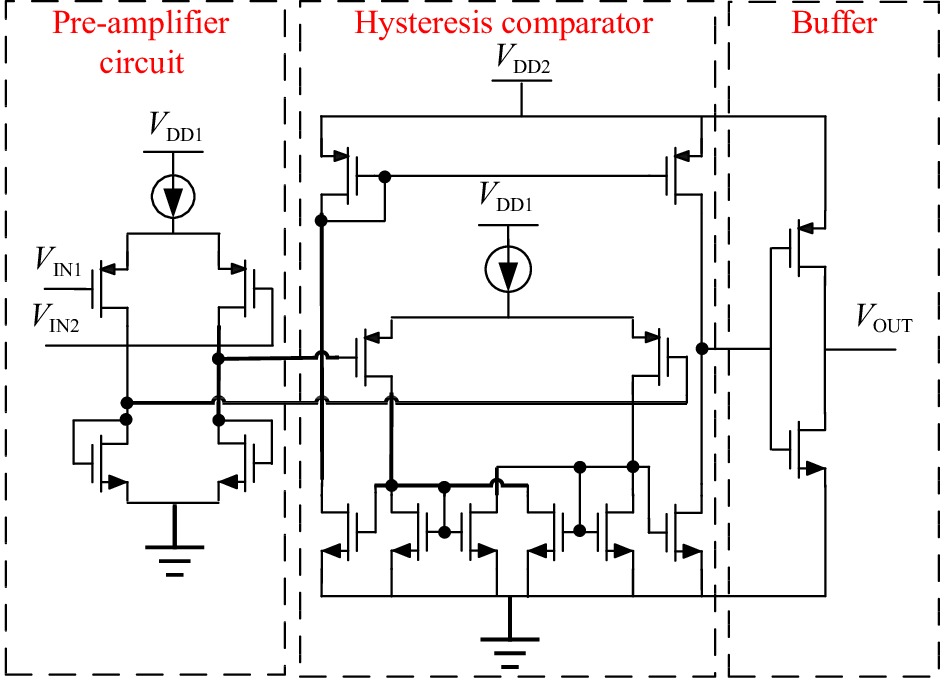

LVDS接收器用于接收传输线中的LVDS信号,并经过一系列的信号处理最后转换为高电平为1.2 V,低电平为0 V的CMOS信号。在整个信号传输系统中,虽然驱动器(Driver)起着非常重要的作用,但高性能的接收器能够弥补发送器的不足[3]。NICA ROC芯片前端的MAPS输出400 Mbps的LVDS信号送到NICA ROC芯片的接收器,结合未来设计提升的需要,本文设计的LVDS接收器速率的设计指标为800 Mbps,其中输入共模范围为0.6~1.5 V,最小差模为100 mV。本设计中,LVDS接收器包括预放大电路、迟滞比较器电路、缓冲器电路三大部分。图2为LVDS接收器整体原理图。

预放大电路以PMOS作为差分输入对管,可以提高输入共模范围,并且PMOS管的闪烁噪声也会比相同的NMOS管的更小。以二极管连接的NMOS管作为负载,由公式:

可以得出,预放大电路的差模增益是一个与输入共模无关,只与长宽比有关的量。这里忽略了二级效应。

第二部分采用迟滞比较器结构,首先可以放大由第一部分预放大电路输出的差分信号。另外采用迟滞原理,目的在于可以滤除阈值附近的噪声而带来的影响,减少信号误翻转[4-5]。迟滞比较器的设置需要严格考虑,如果迟滞比较深,则可能会将较低的差模的输入信号滤除,而如果迟滞比较浅,则无法滤除阈值附近的噪声,进而失去滤除阈值附近噪声的目的,综合考虑下来,本设计的迟滞电压为20 mV。另外比较器的第一部分采用2.5 V供电用以提高输入电压范围,为降低功耗,第二部分采用1.2 V供电的差分转单端电路,将输入的LVDS差分信号转为CMOS单端信号。

-

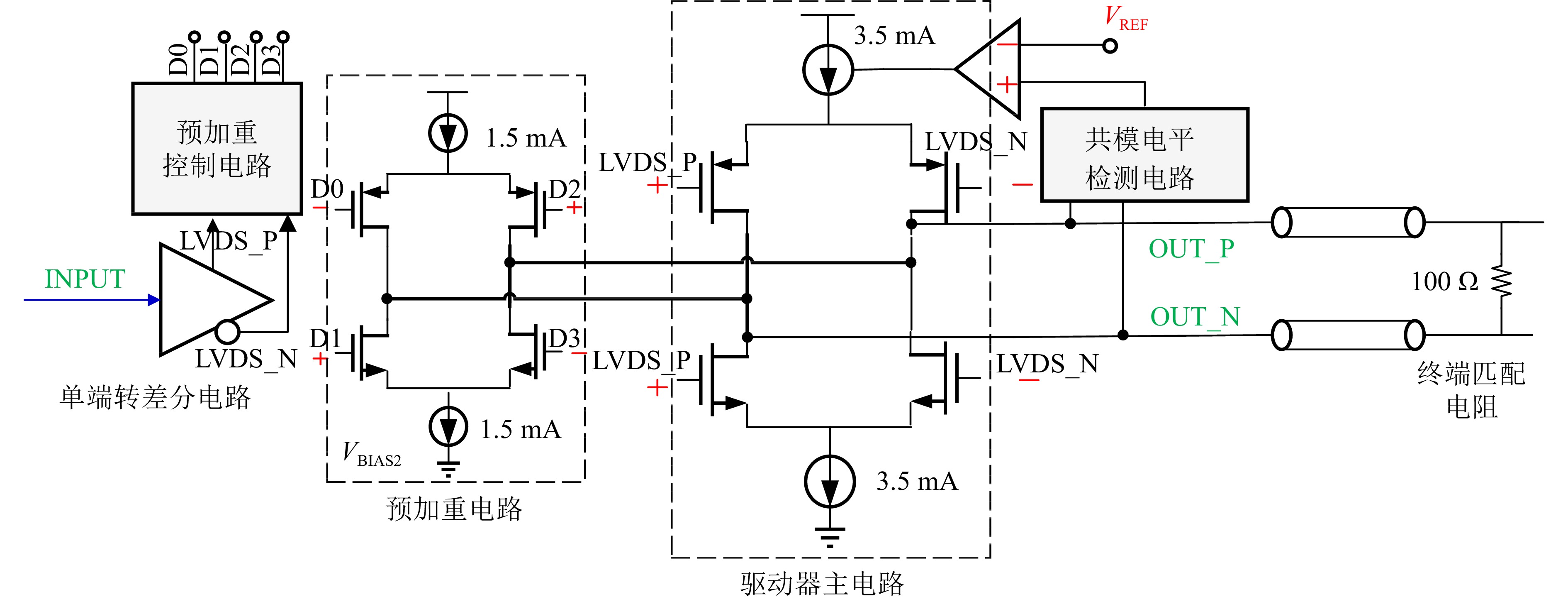

在NICA ROC原型ASIC设计中,经过汇总处理后的数据将通过LVDS驱动器发送到FPGA进行验证,通过FPGA对NICA ROC原型芯片的功能和性能进行评估。LVDS驱动器作为LVDS接口的核心部分,设计一种稳定高速且驱动能力较强的驱动器至关重要。因为LVDS驱动器是需要与FPGA进行交互,因此需要考虑FPGA接收器的相关参数要求进行设计。例如,XILINX生产的型号为Artix-7的FPGA中 LVDS接收器接收的输入差模范围(Differential Input Voltage)为100~600 mV,直流耦合模式下输入共模范围(Input Common-Mode Voltage)为0.300~1.425 V。因此在设计时,LVDS驱动器在驱动负载的情况下,需要保证在FPGA的接收端信号差模最小值大于或等于100 mV。本设计中,LVDS驱动器包括6部分,包括单端转差分电路、双电流源模式的主驱动器电路、预加重控制电路、预加重电路、共模负反馈电路以及终端匹配电阻。LVDS驱动器电路结构如图3所示。

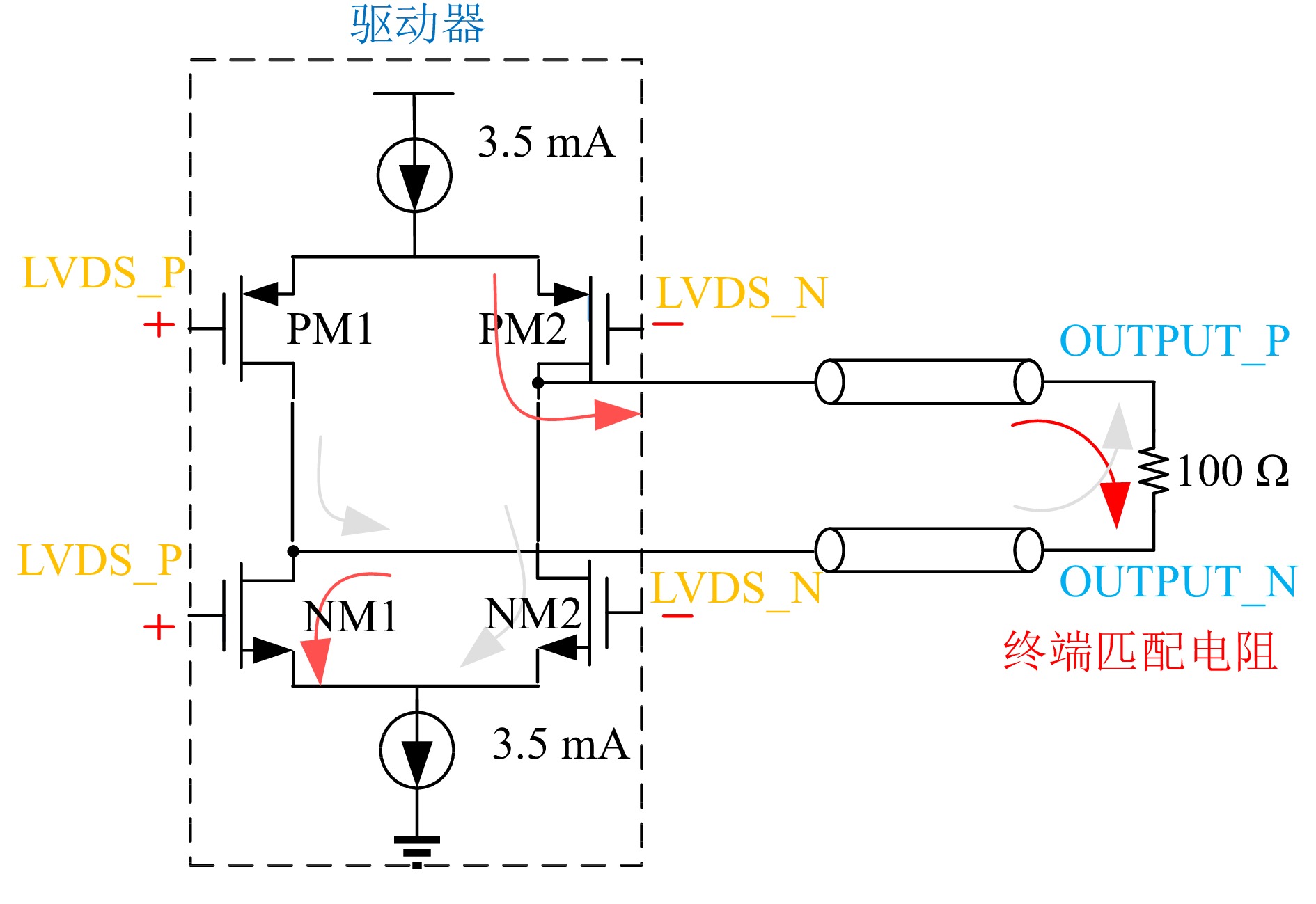

LVDS驱动器主电路输入差分信号,上下2个PMOS管和NMOS管可以视为四个开关管。如图4所示,当LVDS_P为高电平,LVDS_N为低电平时,PM2和NM1导通,此时上下两个电流源的电流顺时针通过终端匹配电阻。当LVDS_P为低电平,LVDS_N为高电平时,PM1和NM2导通,此时上下两个电流源的电流逆时针通过终端匹配电阻,并产生350 mV的压降。

信号在传输线传输过程中,传输线可以视为低通模型,因此高频分量在传输的过程中会有非常严重的衰减[6]。如图5所示,当传输较多的‘0’或‘1’时,信号在信道中会不断进行充电,当后续的传输的数据发生变化时,由于放电无法正常完成,在时域中会发现有严重的码间干扰(Inter Symbol Interference, ISI)[7-8]。因此在发送端需要对信号进行高频补偿,进而弥补信道中高频的损失,本设计中采用预加重技术对信号进行补偿[9]。预加重控制信号由组合逻辑组成,其具体结构由图6(a)所示。其中LVDS_P和LVDS_N是单端转差分的输出,D0~D3是LVDS预加重电路的输入,D0~D3通过控制预加重电路的开启和关断,进而实现对信号的补偿。D0~D3的预加重控制信号输出波形如图6(b)所示,其中P_Width的脉冲宽度决定预加重信号的强弱,脉宽越大,预加重能力越强,同时所需要的功耗也会越大。为最大程度地降低功耗,通过对参数进行优化以及结合仿真确定最终的P_Width为300 ps。

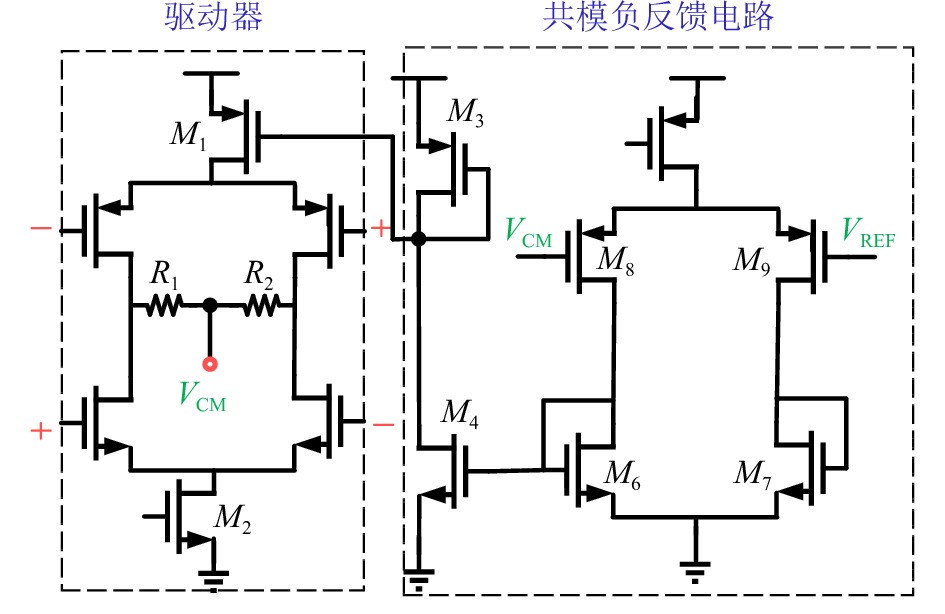

由于PVT(Process-Voltage-Temperature)的影响,LVDS驱动器的输出共模电压会发生变化,共模电压发生变化会严重影响输出波形的质量,因此为了保证LVDS驱动器具有一个稳定的共模电压,本设计采用共模检测电路和共模负反馈电路对输出共模电压进行检测和调节[10-11]。

如图7所示,驱动器电路中M1,M2是驱动的电流源,其中M2是由Bandgap输出的基准电流提供偏置电流。另外R1和R2作为共模检测电路的部分,其中点电压是LVDS输出信号的共模电压VCM。共模负反馈电路将LVDS输出的共模电压与基准电压VREF进行比较,如果VCM大于VREF,也就意味着LVDS输出共模电压偏大,这时M8的栅源电压减小,由公式:

可以得出流过M8与M6的电流减小,这时

$ {V}_{\mathrm{G}\mathrm{S}6} $ 减小,$ {V}_{\mathrm{G}\mathrm{S}4} $ 同样减小,对应的流过M4的电流下降,同时$ {|V}_{\mathrm{G}\mathrm{S}3}| $ 减小,则$ {|V}_{\mathrm{G}\mathrm{S}1}| $ 减小,因为流过M2的电流不变,而总电流是流过M1与 M2的,因此由沟道调制效应得出,M1的漏极电压下降,M2的漏极电压不变,因此M1与 M2漏极之间的电压,即VCM会下降。同理,当VCM大于VREF时,M1漏极电压上升,此时VCM也会上升。 -

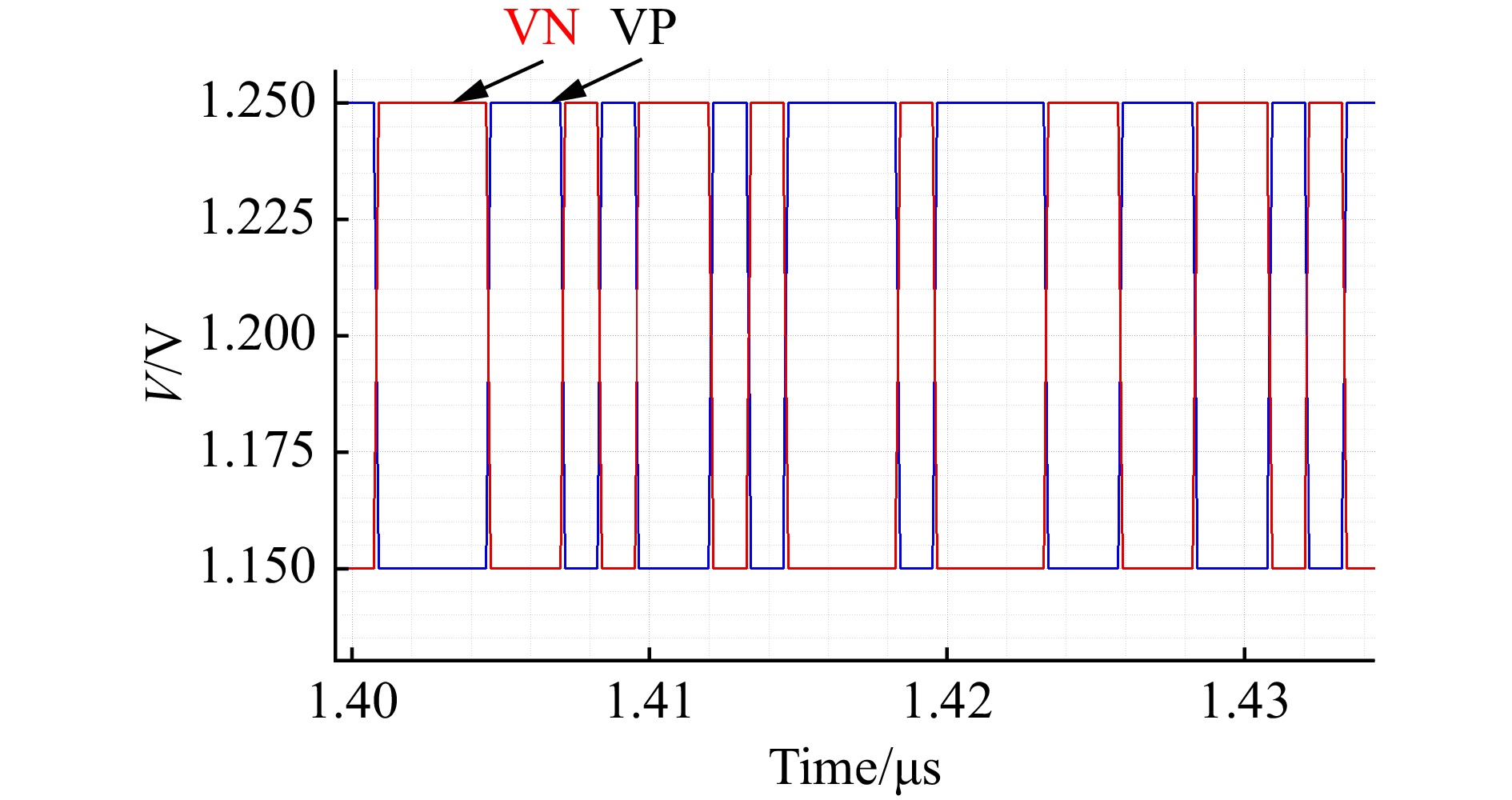

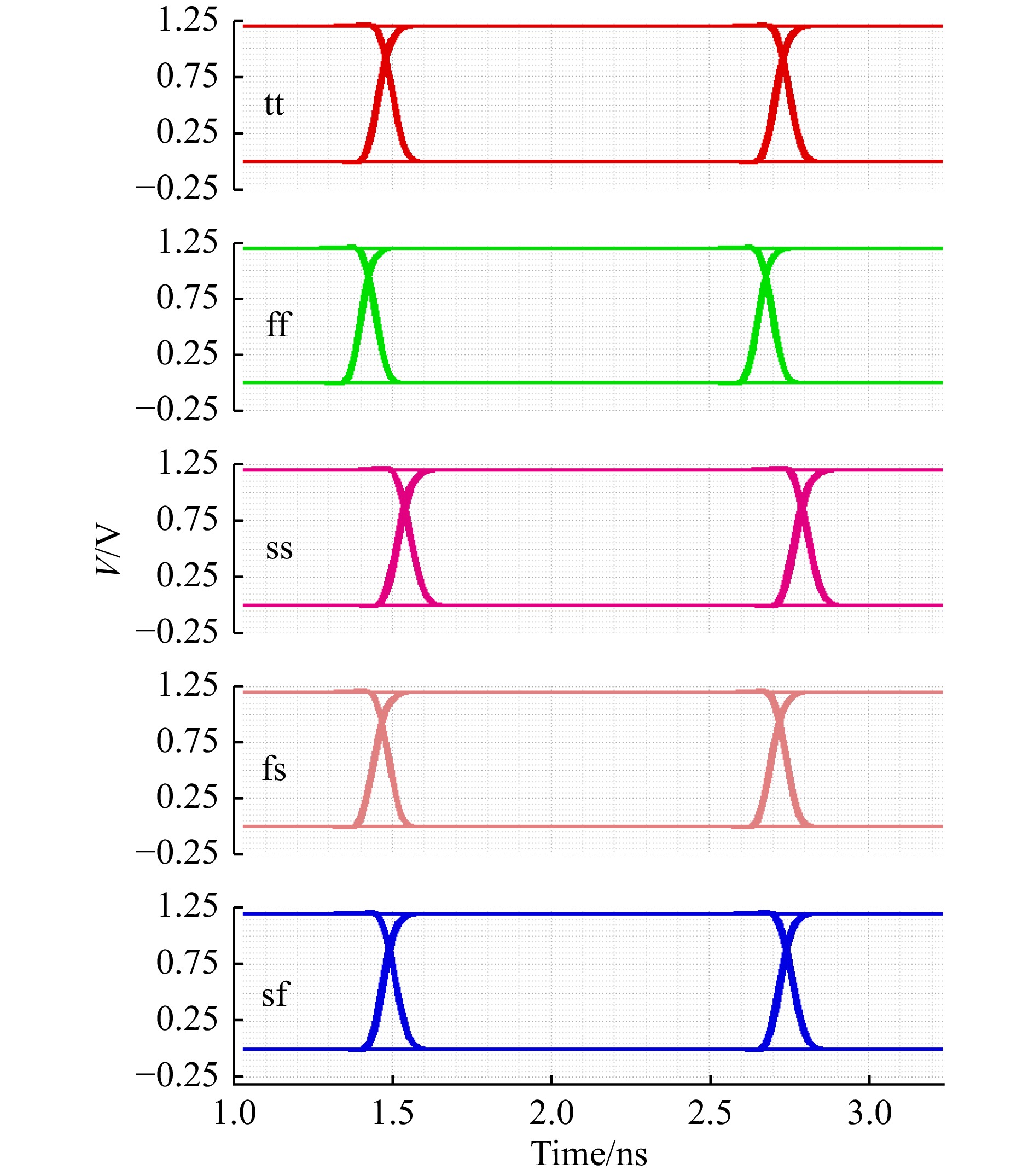

如图8所示为LVDS输入为随机码(PRBS7)、数据率为800 Mbps、共模为1.2 V、差模为100 mV时的输入LVDS差分信号VP和VN。接收器的输出,即图2中的VOUT,在tt、ff、ss、fs、sf五个工艺角下的眼图如图9所示。在驱动负载电容为200 fF下,输出CMOS信号高电平为1.2 V,低电平为0 V。由眼图得出,在tt、ff、ss、fs、sf五个工艺角下接收器的输出抖动分别为12.06, 11.64, 13.85, 10.93 , 12.61 ps。通过蒙特卡罗仿真,设置样本数为2 000,覆盖目标面积(Target Yield)为99.73%,得到LVDS接收器的输出波形占空比(Duty Cycle)最大值与最小值分别为50.5%和50.34%。LVDS接收器功耗最大值(ff)与最小值(ss)分别为2.29和2.18 mW。

-

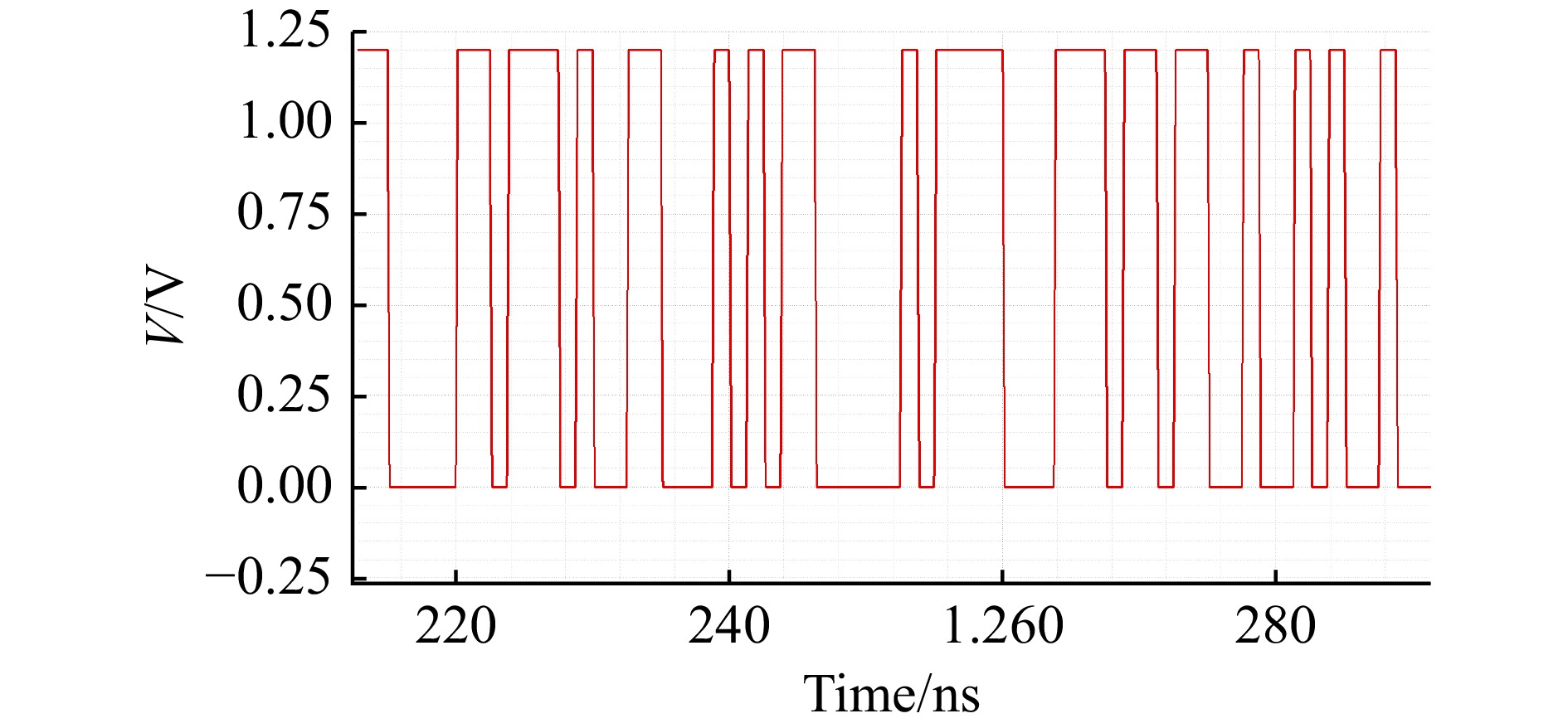

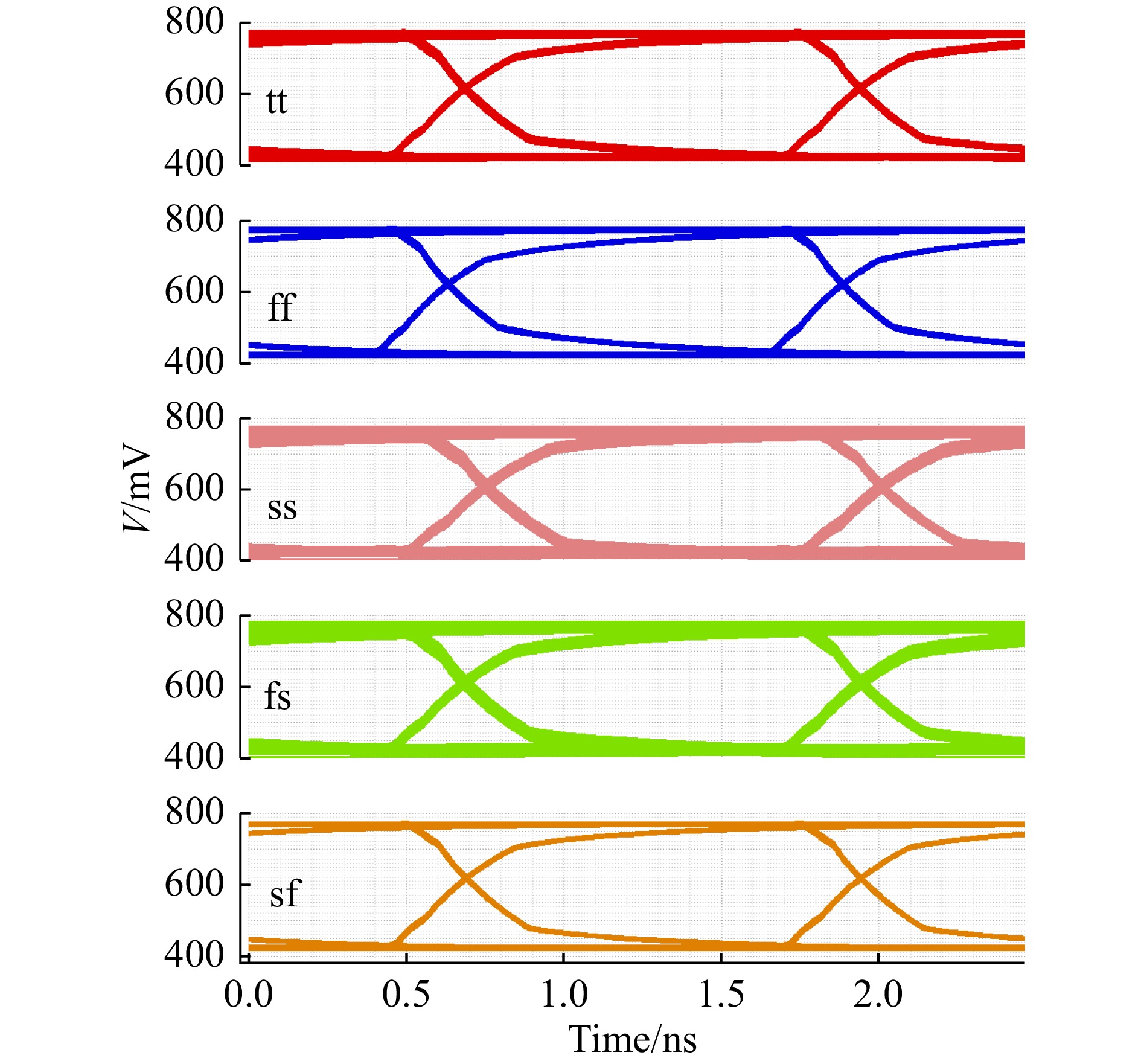

图10所示波形为LVDS驱动器的输入,输入数据率为800 Mbps的随机码(PRBS7),高电平为1.2 V,低电平为0 V。如图11所示,自上而下的波形为输入在5种工艺角(tt、ff、ss、fs、sf),驱动负载电容为10 pF的输出信号眼图。由眼图得,在5个工艺角下接收器的输出抖动分别为23.38, 17.60, 38.09, 38.59, 14.57 ps。通过蒙特卡罗仿真,设置样本数为2 000,覆盖目标面积(Target Yield)为99.73%,得到LVDS驱动器的输出波形占空比(Duty Cycle)最大值(ff)与最小值(ss)分别为51.82%和49.25%,接收器输出波形的差模电压最大值(ff)与最小值(ss)分别为329和310 mV,输出波形共模电压最大值(ff)与最小值(ss)分别为600.8和588.7 mV。LVDS驱动器功耗最大值(sf)与最小值(ss)分别为7.03和6.95 mW。

-

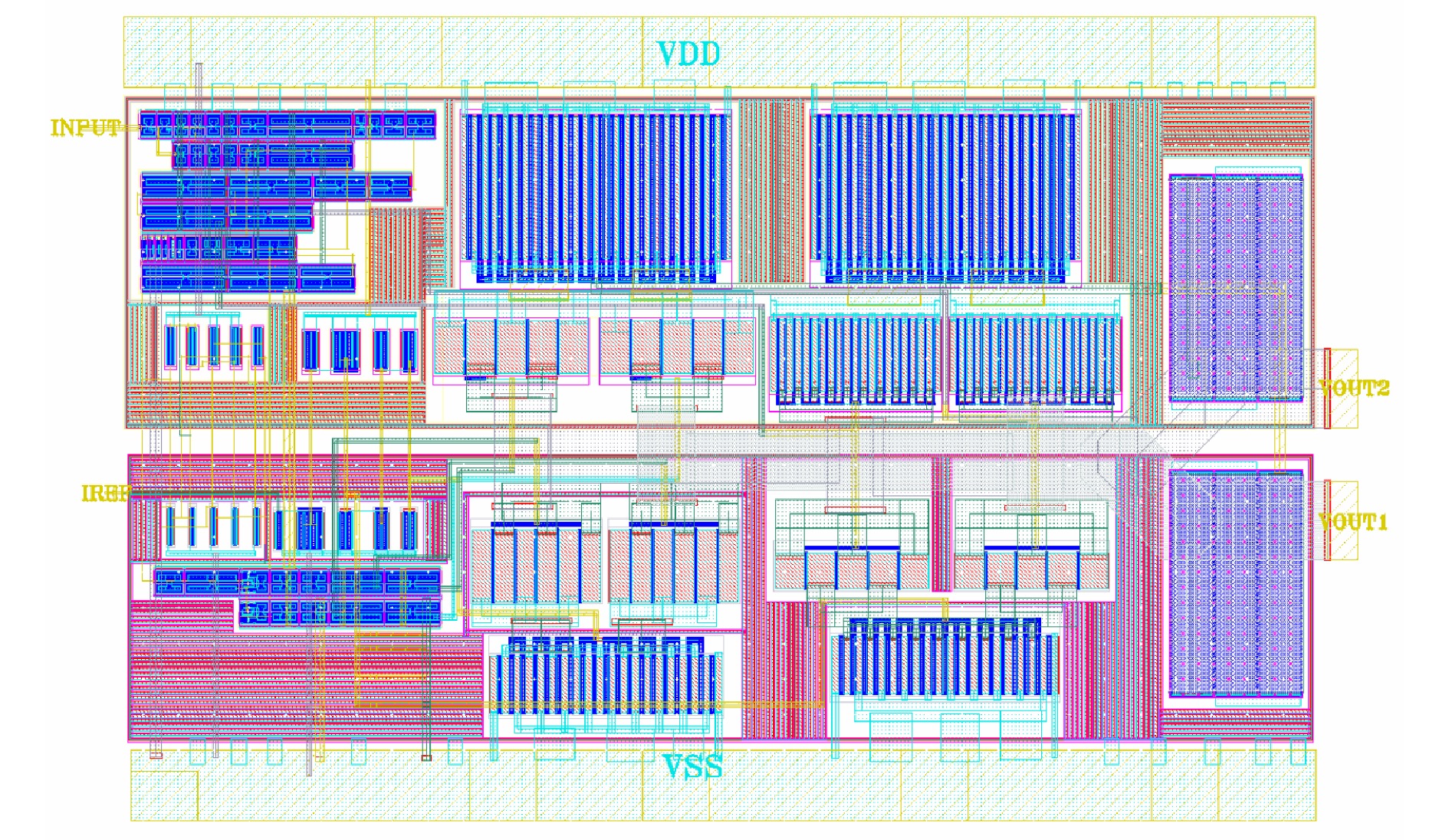

图12所示为LVDS接收器版图,面积为49.195 µm×70.7 µm。图13所示为LVDS驱动器版图,面积为166.41 µm×112.905 µm。

-

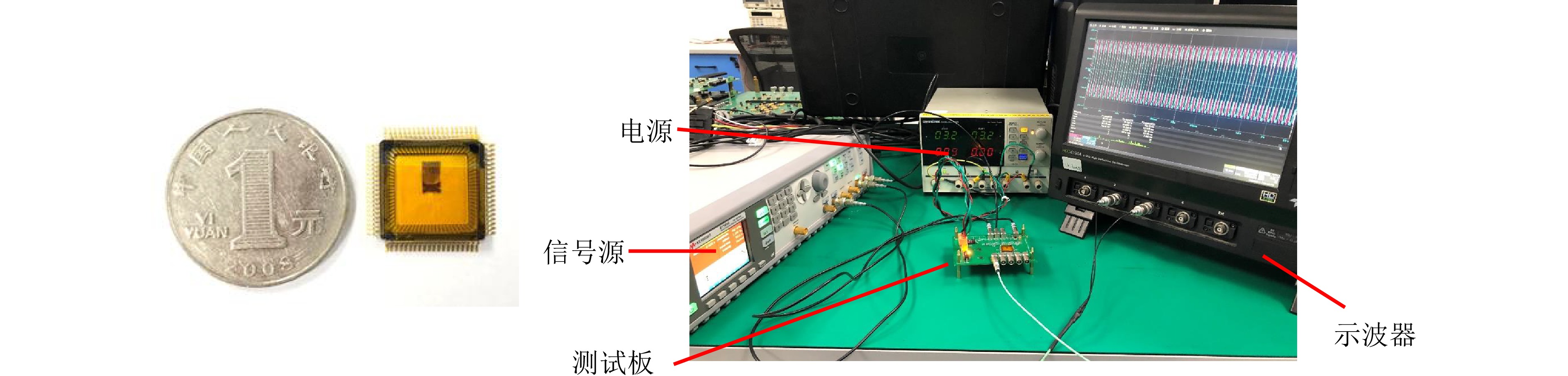

本设计的测试方案是首先信号源输出单端信号,经过单端LEMO后送入测试板上的变压器,经过变压器后将输入单端信号转为差分信号再送入LVDS接口芯片。由于变压器输出的差分信号是隔直之后的信号,因此在变压器后会有设置共模电压的电路来设置输入芯片的共模电压。通过设置不同的输入共模电压,来确定接口可以接收的输入共模电压的范围。芯片内部经过对信号进行处理后,驱动器产生的电流经过100 Ω终端匹配电阻后产生LVDS差分信号,通过差分LEMO后,经1 m的信号线传输出到示波器,通过示波器分析信号的眼图、占空比、抖动和误码率等性能。如图14所示,芯片采用QFP80的封装,封装面积为17.5 mm×17.5 mm,芯片的测试台包括电源(GPD-3303)、信号源(KEYSIGHT 81160A)、示波器(HDO4104A)以及芯片测试板。

-

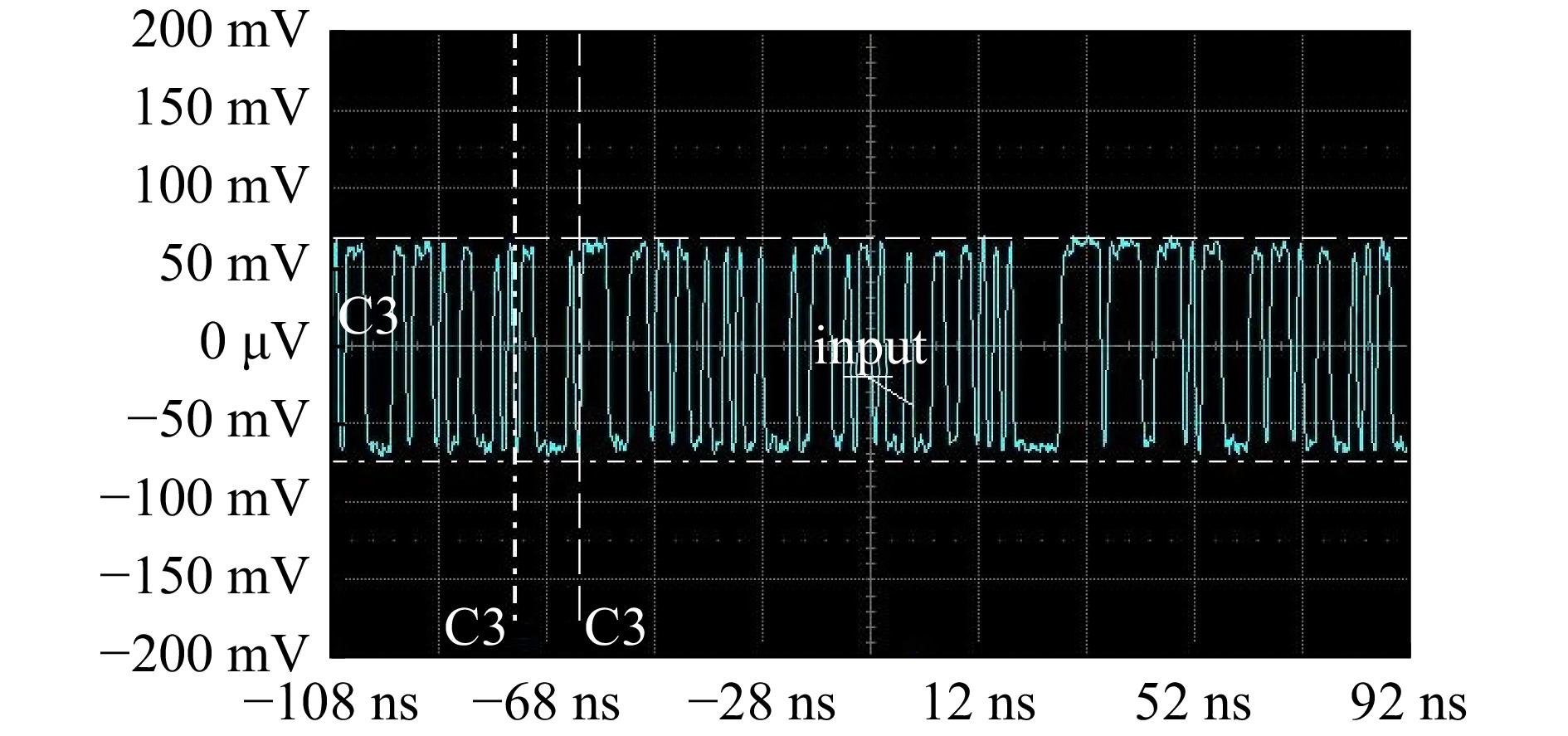

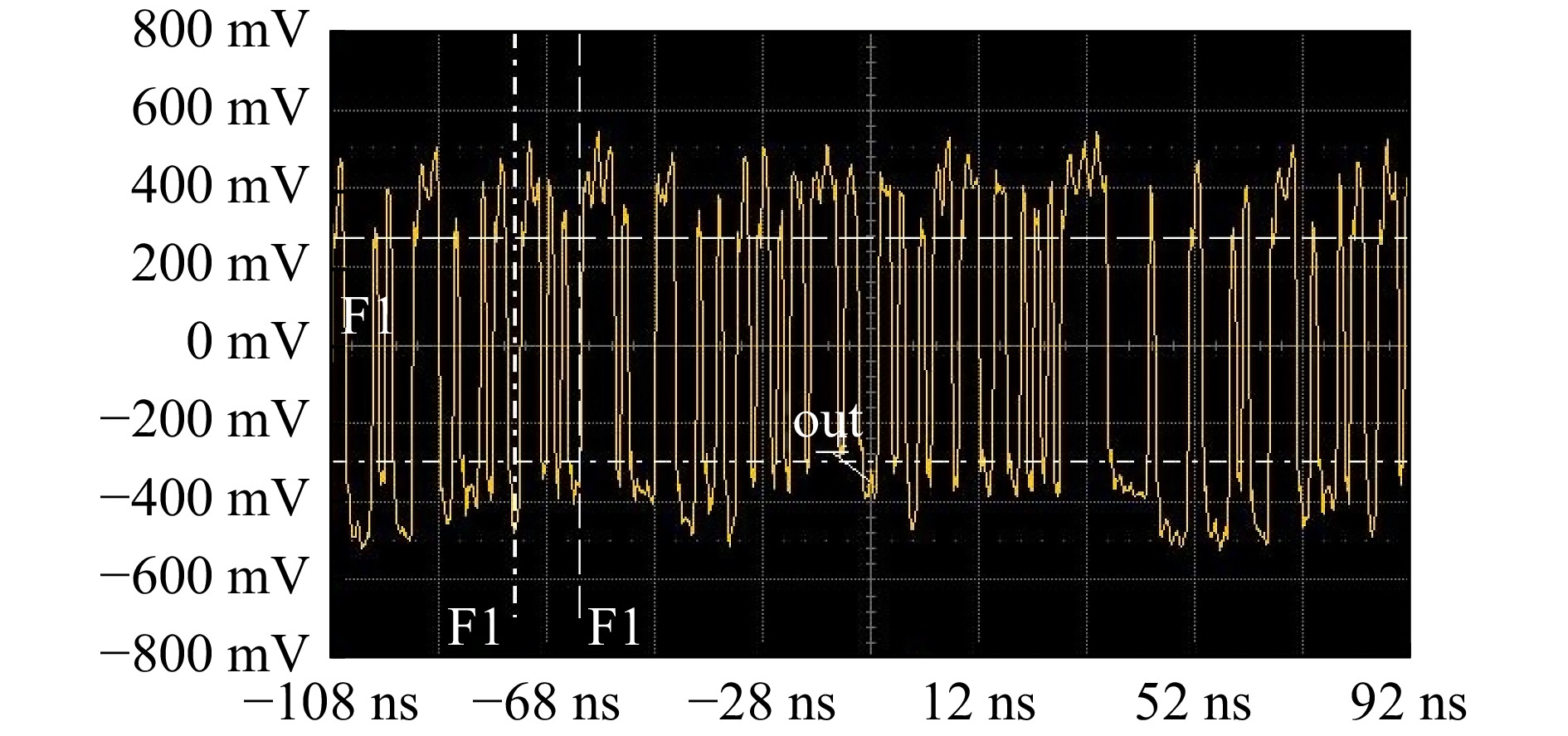

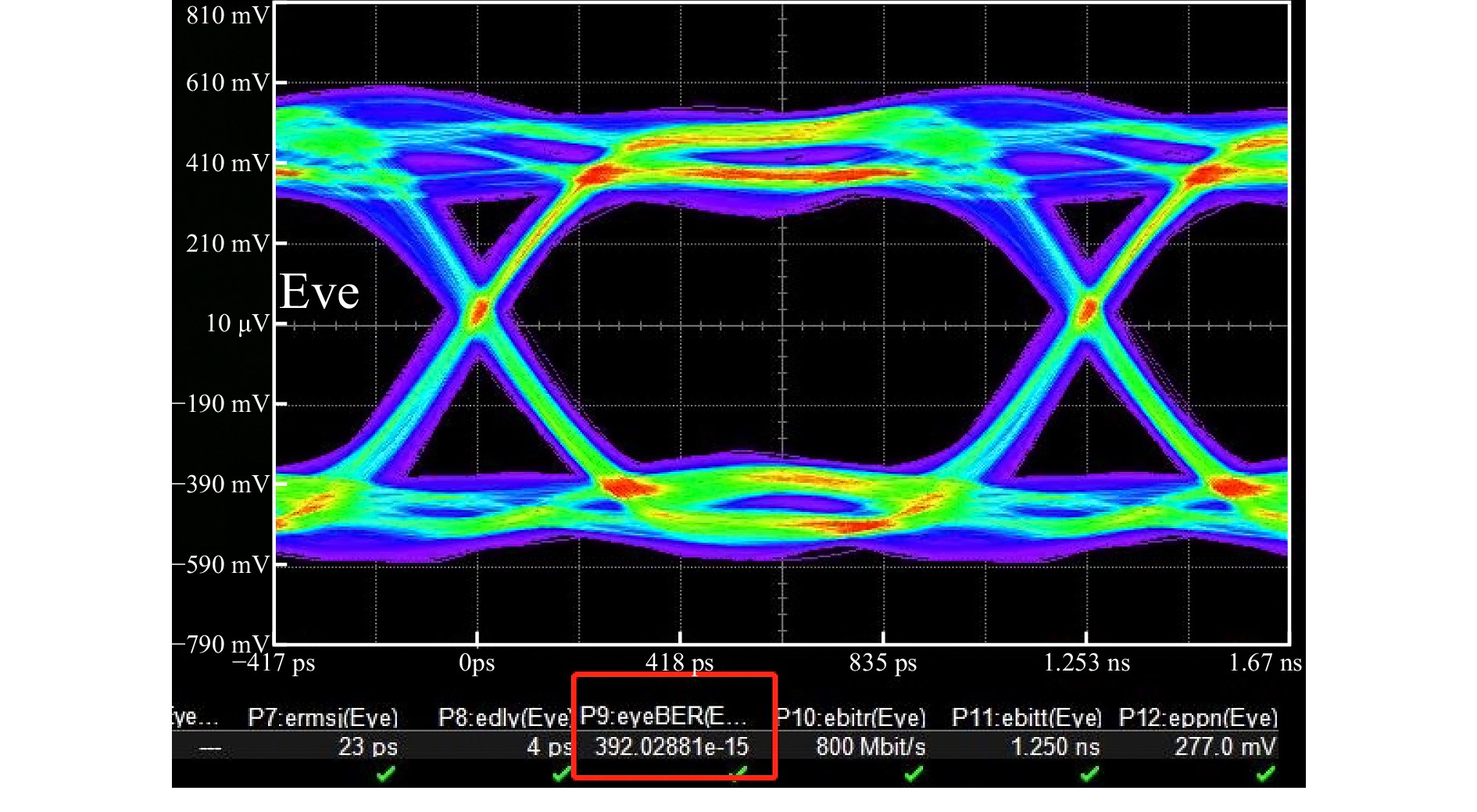

输出线为差分LEMO转两个单端SMA,由于线的长度在1 m左右,以及SMA和LEME转接头都有一定程度的阻抗不连续,这使得输出信号具有一定程度反射以及衰减,也就意味着眼图情况会有一些恶化。为了模拟实际使用时传输的8B/10B编码信息,信号源的输入为随机码(PRBS7)。其中眼图的抖动包括芯片本身的抖动和信号源的抖动。如图15所示,波形为信号源单端输出、差模100 mV、数据率800 Mbps的信号。图16给出了差分输出的LVDS信号。图17为对应图16的眼图。从眼图可以得出,高为260 mV,眼宽为1.15 ns,总体抖动(Total Jitter, TJ)约为100 ps。

-

信号在信道传输过程中可能会受到很多因素的影响,例如噪声、串扰和码间干扰等,这些影响因素会导致码元在接收端出现错误。码率(Bit Error Ratio, BER)的高低可以表明一个系统的传输性能,误码率越低表明信号在此系统中的传输质量越好。误码率公式如式(3)所示:

IEEE802.3规定误码率的最坏情况是

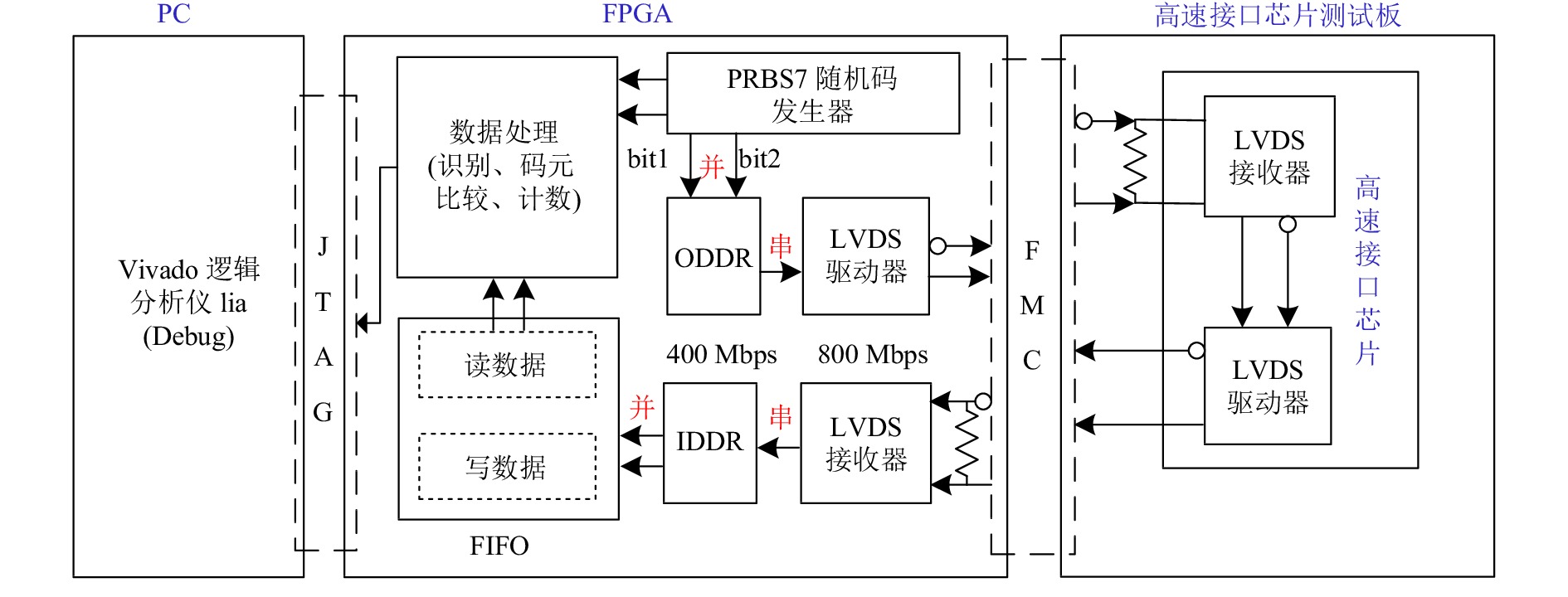

${1 \times 10}^{-10}$ 。在中国科学技术大学核探测与核电子学国家重点实验室参与的NICA项目中,所要求的的误码率最坏情况是$ {1\times 10}^{-12} $ 。本设计测试误码率的整体结构如图18所示。FPGA发送数据率为400 Mbps的两路并行PRBS7随机码至ODDR(Output Double Data rate)中,ODDR将两路并行数据转为800 Mbps的串行数据,之后送至LVDS驱动器发出至高速接口芯片中。高速接口芯片测试板通过FMC(FPGA Mezzanine Card)与现场可编程逻辑门阵列(Field Programmable Gate Array, FPGA)相连接。数据通过高速接口芯片后,发送到FPGA的LVDS接收器,再通过IDDR(Input Double Data rate)将800 Mbps的串行数据转为两路400 Mbps的并行数据,并送入FIFO(First Input First Output)存储器中。通过数据处理模块将FIFO中接收到的数据进行处理,并与发送的数据进行比较,进而获得相应的误码率。在数据处理模块,如果输入与输出相等,则正确码元计数器加1,如果不相等则错误码元计数器加1。经测试,输出

${1 \times 10}^{13}$ 个码元,正确码元计数器为${1 \times 10}^{13}$ ,错误码元计数器为0。得到芯片的误码率小于等于${1 \times 10}^{-13}$ 。 -

针对中国科学技术大学核探测与核电子学国家重点实验室自主设计的硅像素探测器前端数据汇总与传输原型芯片NICA ROC的数据收发需要,设计了一种LVDS高速串行接口电路。经过流片和测试后的结果显示,LVDS接口芯片在较低的功耗下,能够接收较大输入共模范围0.3~2.0 V的信号和最小100 mV的差模信号。数据率为800 Mbps的数据信号输出的眼图显示最小差模在260 mV左右、抖动在100 ps左右、误码率好于

$ {1\times 10}^{-13} $ 。在LVDS收发器传输800 Mbps的数据时,一对LVDS驱动器总功耗仅为9.5 mW,这些参数的获得对于后续设计具有重要的意义。通过对LVDS高速串行接口芯片的测试,验证了芯片各项参数性能已达标,满足设计要求和测试目标。

Design of LVDS Transceiver in NICA MPD ITS Front-end Data Collection and Transfer Chip

doi: 10.11804/NuclPhysRev.40.2022041

- Received Date: 2022-05-08

- Rev Recd Date: 2022-06-06

- Publish Date: 2023-09-20

-

Key words:

- low voltage differential signal /

- receiver /

- driver /

- Pre-emphasis

Abstract: NICA(Nuclotron-based Ion Collider fAcility) is a heavy ion collider based on superconducting particle accelerator developed by China and Russia. According to the requirements of data receiving and sending in NICA ROC(NICA Readout and Control) ASIC, designed for ITS front-end data collection and transmission in NICA MPD, a Low Voltage Differential Signaling(LVDS) high-speed serial interface circuit is designed as the data interface between NICA ROC and front-end readout ASICs, and the pre-emphasis technique is employed to reduce the inter-symbol interference. Based on 130 nm CMOS technology, the circuit design, simulation, layout design, and tape-out of LVDS receiver and driver have been completed. A test system is designed for this high-speed serial interface chip. The test results show that the LVDS transceiver can achieve 800 Mbps receiving and transmitting data rate, and the differential output voltage is about 260 mV, with the Bit Error Ratio(BER) less than

| Citation: | Li LI, Jiajun QIN, Lei ZHAO, Zeguang CHANG, Jiacheng GUO, Chunxiao SONG, Qi AN. Design of LVDS Transceiver in NICA MPD ITS Front-end Data Collection and Transfer Chip[J]. Nuclear Physics Review, 2023, 40(3): 418-425. doi: 10.11804/NuclPhysRev.40.2022041 |

甘公网安备 62010202000723号

甘公网安备 62010202000723号 DownLoad:

DownLoad: