-

暗物质探测是当前国际上粒子物理和天体物理领域很热门的研究内容,我国在高能伽马射线方面的空间探测方向上起步较晚,在中国科学院空间科学战略性先导科技专项支持下[1],我国于2015年发射成功了首颗天文科学卫星暗物质粒子探测卫星“悟空”。“悟空”进入预定轨道以来,获得了目前国际上精度最高的电子宇宙射线能谱探测结果。“悟空”号的研发、运行和分析研究经验为成功研制新一代大型伽马射线探测卫星奠定了坚实的基础。考虑到高能伽马射线天文领域的蓬勃发展前景[2],国内多家单位进行联合提出要研制新一代高性能的甚大面积伽马空间望远镜VLAST(Very Large Area gamma-ray Space Telescope)[3]。VLAST的探测器从顶部到底部包括:反符合探测器(Anti Coincidence Detector, ACD)、径迹及低能伽马探测器(Silicon Tracker and low Energy gamma-ray Detector, STED)、高能成像量能器(High Energy Imaging Calorimeter, HEIC) [2]。其中,反符合探测器拟采用有机塑料闪烁体作为探测器的灵敏材料,即使用塑料闪烁体阵列探测器(Plastic Scintillator Detector, PSD,后续简称塑闪阵列探测器)完成反符合功能,PSD对前端读出电子学提出了大动态范围的需求。同时,在空间探测领域中,高集成度的专用集成电路 ASIC(Application Specific Integrated Circuit)芯片技术逐渐成为发展趋势[4]。因此,为了实现塑闪阵列探测器能量信号的读出和分析,并配合已有的前放及成形芯片的读出要求,亟需设计一款大动态范围的峰值保持电路ASIC芯片,设计需求为非线性误差优于1%,下垂速率好于10 μV/μs,动态范围为30~900 mV。

-

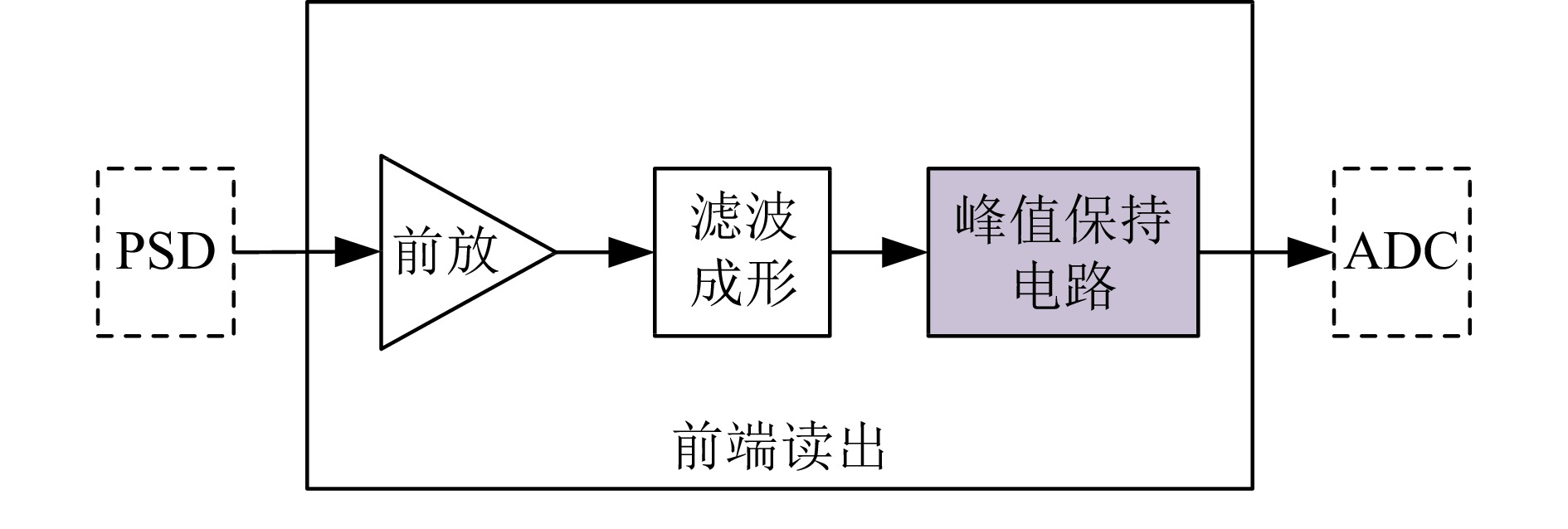

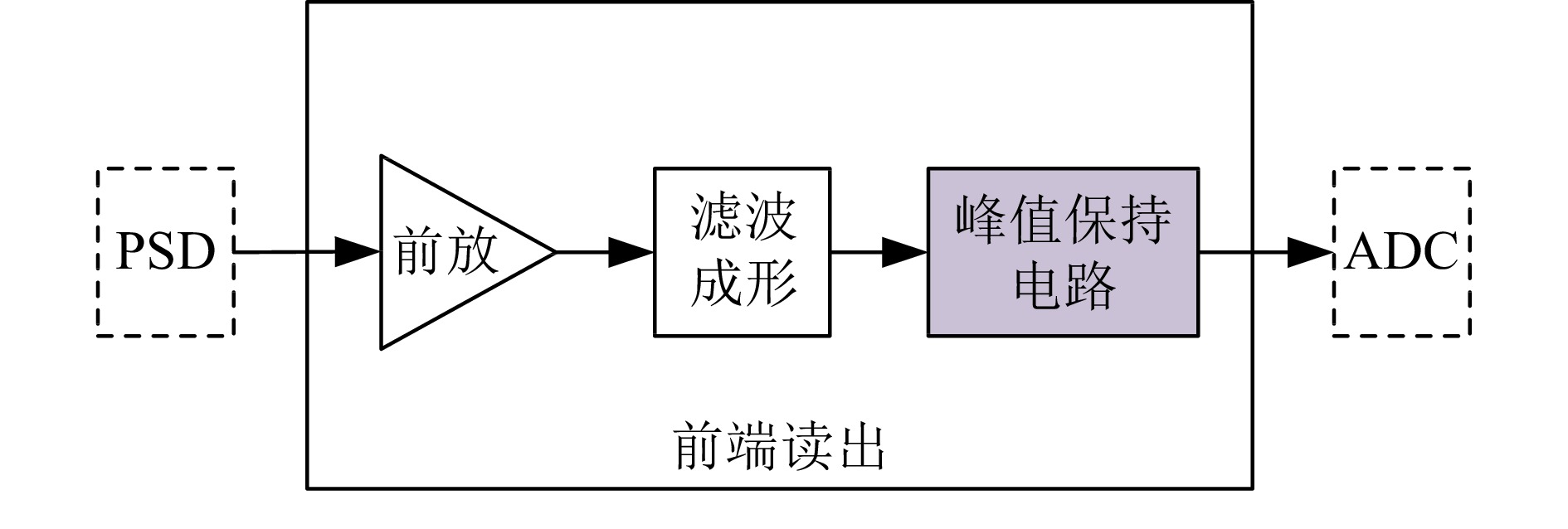

塑闪阵列探测器输出信号的前端读出电路设计框图如图1所示[5]。探测器输出的电荷信号,经过前置放大器在电容上积分成电压信号并放大后,送入滤波成形电路中对信号进一步放大和成形,产生一个准高斯波形,波形的峰值能反映出探测器输出信号的能量信息。为了更稳定地获得能量信息,需要峰值保持电路对滤波成形之后的准高斯波形的峰值进行检测,并保持一段时间,然后将峰值信息输出至低采样率ADC中,做数字化处理和分析。

本文的工作就是设计图1中的峰值保持电路。传统的峰值保持电路主要由跨导型运算放大器U1、二极管D1、保持电容C1和缓冲器U2组成,结构图如图2所示。

当输入信号上升沿到来时,跨导型运算放大器U1的反向端输入信号Vout小于正向端输入信号Vin,二极管D1导通,U1的输出电流经过二极管D1对保持电容C1充电,C1上的信号经过U2缓冲后反馈到U1的反向端,使U1的反向端输入信号Vout增加;当输入信号的下降沿到来时,Vout大于Vin,U1输出为负,则二极管截止,保持电容上的电压保持不变,从而实现输入信号的峰值保持[6]。这一工作原理成功地应用于几个离散电路的实现[7-10]。

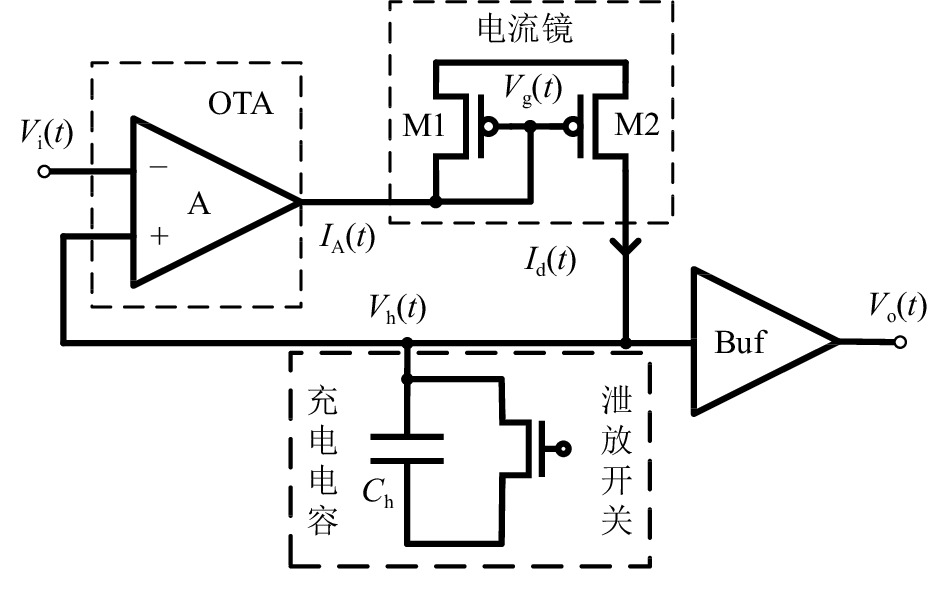

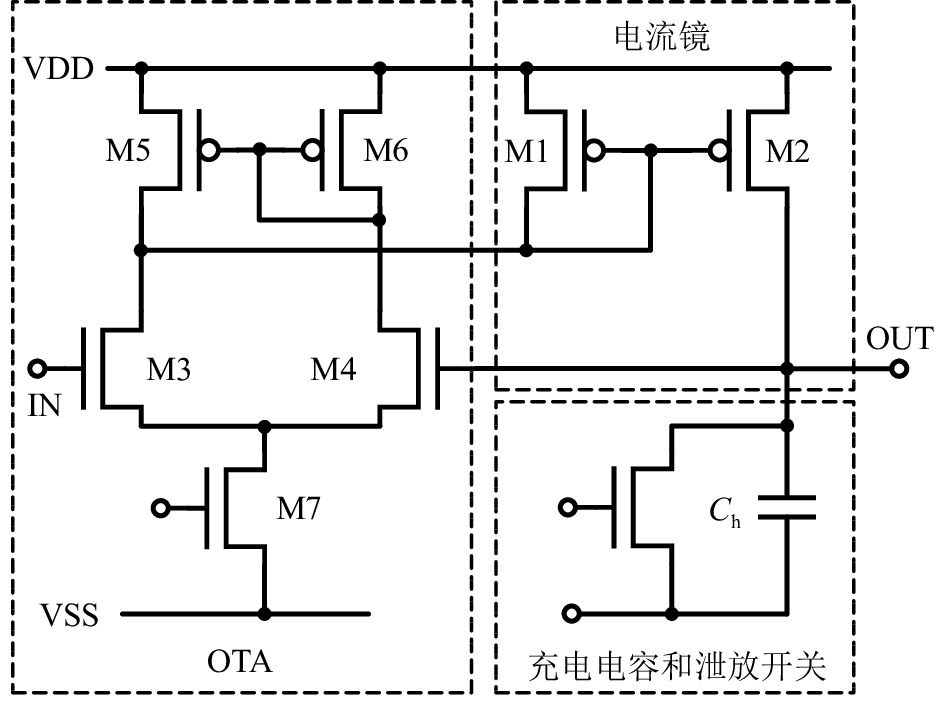

由于二极管具有一定的正向导通压降,所以传统的峰值保持电路需要在前端设计一个补偿电路来抵消二极管正向压降的影响,增加了电路的复杂性和不稳定性[5]。考虑到传统峰值保持电路中因二极管正向导通电压引起的影响,我们设计的峰值保持电路ASIC芯片,使用有源器件MOSFET管来代替二极管[11],单通道的电路结构如图3所示,该电路包括4个部分,跨导放大器OTA(Operational Transconductance Amplifier)、电流镜、充电电容Ch和泄放开关、缓冲器[12]。

工作过程为:跨导放大器A的“−”端接输入信号Vi(t),“+”端接电容上的保持电压Vh(t),跨导放大器A输入端的差模电压为Ve(t),

$$ {V}_{\mathrm{e}}\left(t\right)={V}_{\mathrm{h}}\left(t\right)-{V}_{\mathrm{i}}\left(t\right) ; $$ (1) 当输入信号Vi(t)到达并高于保持电压Vh(t)时,跨导放大器的输出电流IA(t)经过电流镜中二极管接法的M1管,进行I-V转换,使M1和M2的栅极电压Vg(t)产生一个急剧负跃迁,从而使M2导通,电流Id(t)开始对保持电容Ch进行单向充电,直到Ve(t)接近零。然后通过环路不断调整栅压Vg(t),使

$$ {I}_{\mathrm{d}}\left(t\right)={C}_{\mathrm{h}}{\boldsymbol\cdot} {V}_{\mathrm{i}}'\left(t\right) , $$ (2) 其中Vi´(t)是Vi(t)的斜率。跟踪条件Vh(t)= Vi(t)一直持续到Vi(t)接近其峰值Vi(tp)= Vip,此时Vi´(t)趋于零,Ve(t)改变符号,并使Vg(t)产生一个急剧的正跃迁,使M2关断。由于Ch没有可用的放电路径,Vh(t)保留了Vi(t)的峰值,从而实现了保持条件:

$$ {V}_{\mathrm{h}}(t\geqslant {t}_{\mathrm{p}})={V}_{\mathrm{hp}}={V}_{\mathrm{ip}} 。 $$ (3) 由此工作原理,电路实现了对输入信号峰值信息的保持过程。

-

芯片单通道包括峰值保持电路和输出缓冲器。其中峰值保持电路的设计图如图4所示,电路包括3个部分,OTA、电流镜、充电电容Ch和泄放开关。五管OTA中,NMOS输入管M3和M4为差分对管,构成差分输入结构,M5和M6两个PMOS对管构成电流镜,其中M5的漏极接输出,而M6的漏极与栅级相连,构成二极管连接,M7决定了支路总电流,由电流镜结构平均分配到两条支路。电流镜电路中,PMOS 管M1为I-V转换管,M2管既是充电元件,也是开关元件,在导通时起充电功能,当关断时,高阻抗以防止电容Ch上的存储电压失真。当峰值信息保持一段时间后,泄放开关导通,电容放电至基线电压,然后等待下一个信号的到来。

其中,在设计OTA时,W为晶体管的宽度,L为晶体管的长度,较小的输入管对地电容(Cgs+Cgb)能够提高电路的工作速度,约束WL的面积可以获得较小的电容。因此,差分对输入管M3和M4的栅长L取该工艺下能达到的最小栅长0.35 μm。为降低OTA的失调电压,W的取值也应该相应地减小。但减小W会引起差分对管的增益不足,因此需要根据需求精度以及功耗等因素综合考虑。在电流镜中,M2管的漏电流Id对电容Ch充电时的摆率要与输入信号的上升速度一致,为了配合M2管充电时的摆率,电流镜需要对差分对管的总电流进行相应的衰减,考虑以上因素并结合式(4)来决定M2管的尺寸:

$$ {C}_{\mathrm{h}}{{V}_{\mathrm{i}}}^{{'}}\left(t\right)={I}_{\mathrm{d}}\left(t\right)=\frac{1}{2}\mu {C}_{\text{ox}}\frac{W}{L}{\left({V}_{\mathrm{D}\mathrm{D}}-{V}_{\mathrm{g}}-{V}_{\mathrm{T}}\right)}^{2} \text{,} $$ (4) 式中:

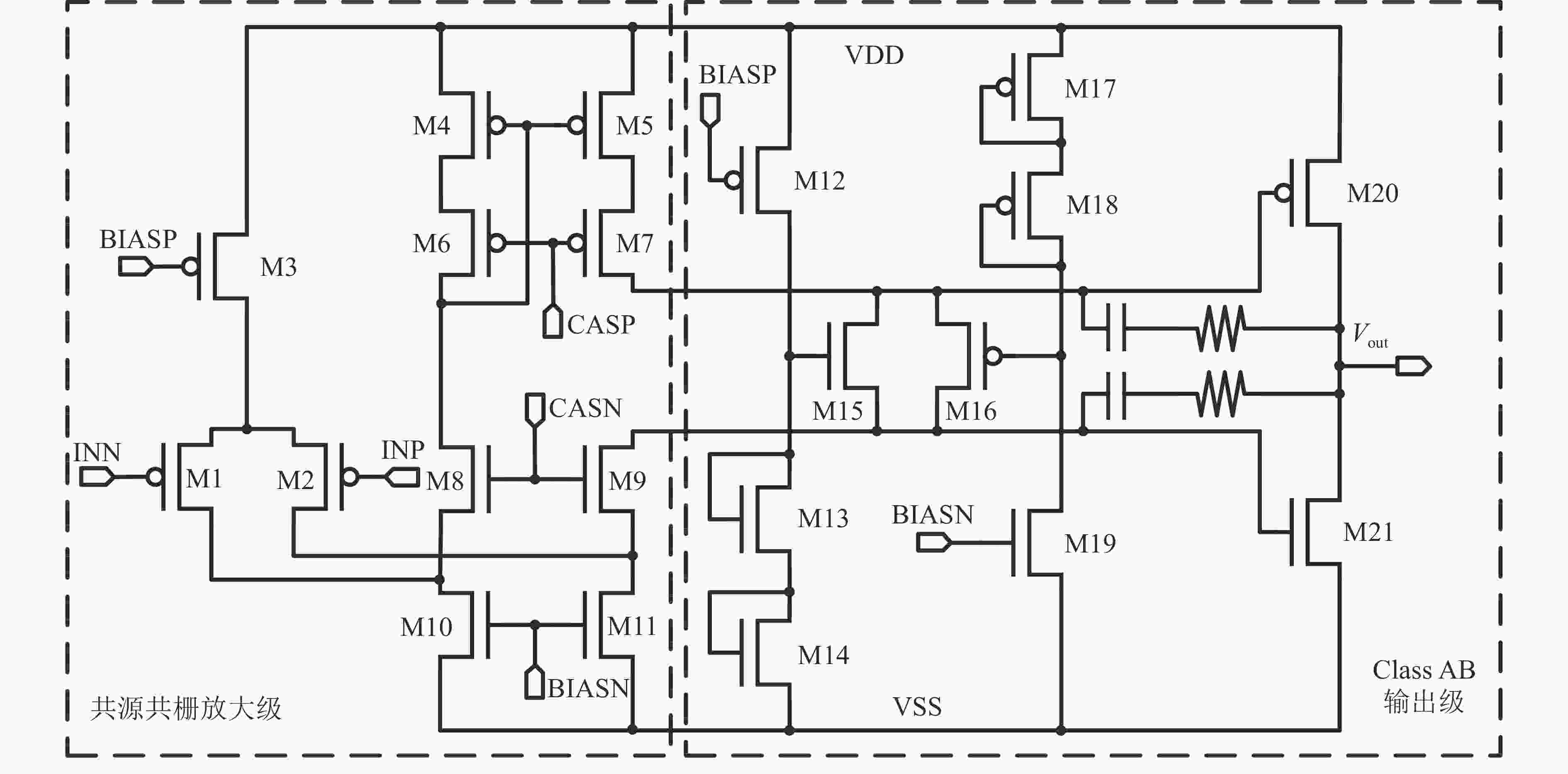

$ \mu $ 为载流子迁移率;W/L是晶体管的宽长比;Vg是栅极电位;VT为晶体管的阈值电压;Cox为栅氧化层电容;VDD为电路的电源电压。为保证能够驱动大电容及小电阻负载,缓冲器采用带有Class AB输出结构的放大器,缓冲器的结构图如图5所示。其中第一级采用PMOS管输入的共源共栅结构放大器,M1与M2差分对使用PMOS作为输入级,可以提高电路抗辐照性能,M4-M7、M8-M11采用了共源共栅结构,有助于抑制电源噪声;第二级使用Class AB结构的输出电路[13-14],提高了电路的带负载能力[15]。仿真得到的缓冲器性能指标为:带宽37.27 MHz,开环增益114 dB,摆率43.8 V/μs。

-

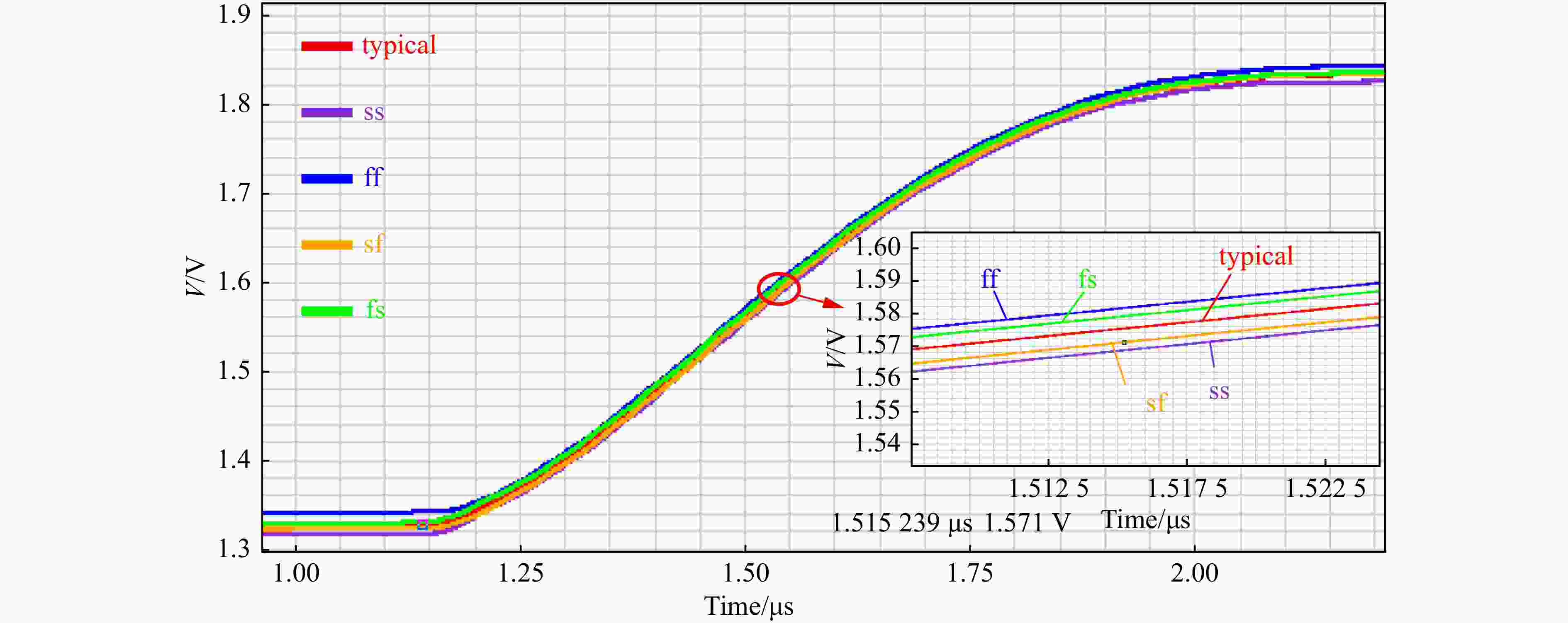

仿真的输入信号采用的是基线电压1.3 V、上升沿 1 μs左右的高斯波形信号。仿真结果如图6~8所示。通过仿真结果可得,峰值保持电路工作正常,在33~940 mV的输入动态范围内,非线性误差优于0.75%,下垂速率为1.05 μV/μs,峰值探测延迟时间约为30 ns。

-

该芯片采用180 nm CMOS工艺,3.3 V单电源供电。芯片版图如图9所示,单通道版图尺寸为110 μm×50 μm。版图的绘制考虑到设计的用途对版图进行了优化[15],通过添加保护环来减小干扰,增强抗辐照能力;根据电流的大小设计不同宽度的走线,并且走线要尽量短,来减小走线上带来的寄生电阻和电容;在整体版图设计时,要保证衬底接地良好,防止引起闩锁效应。

版图设计后,进行了DRC和LVS的验证,以及版图的参数提取,并对电路进行了后仿真。后仿真的输入信号采用的是基线电压1.3 V、上升沿1 μs左右的高斯波形信号。仿真结果如图10所示,下垂速率好于1.43 μV/μs,峰值探测延迟时间约为35 ns。

-

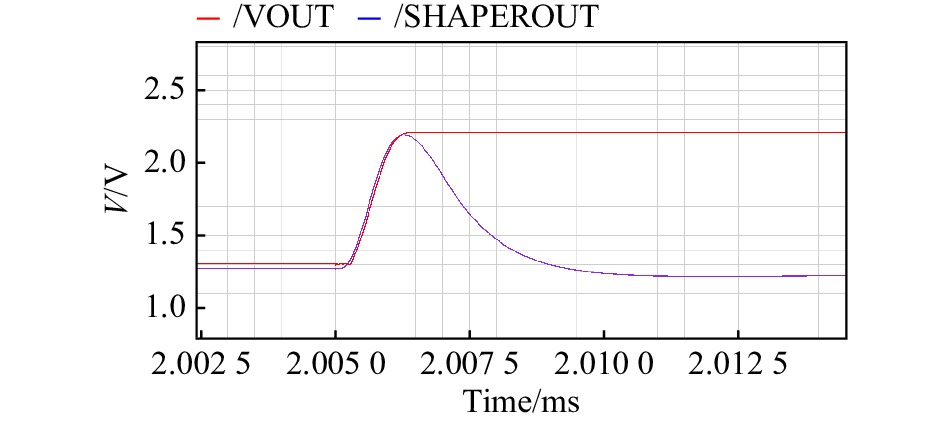

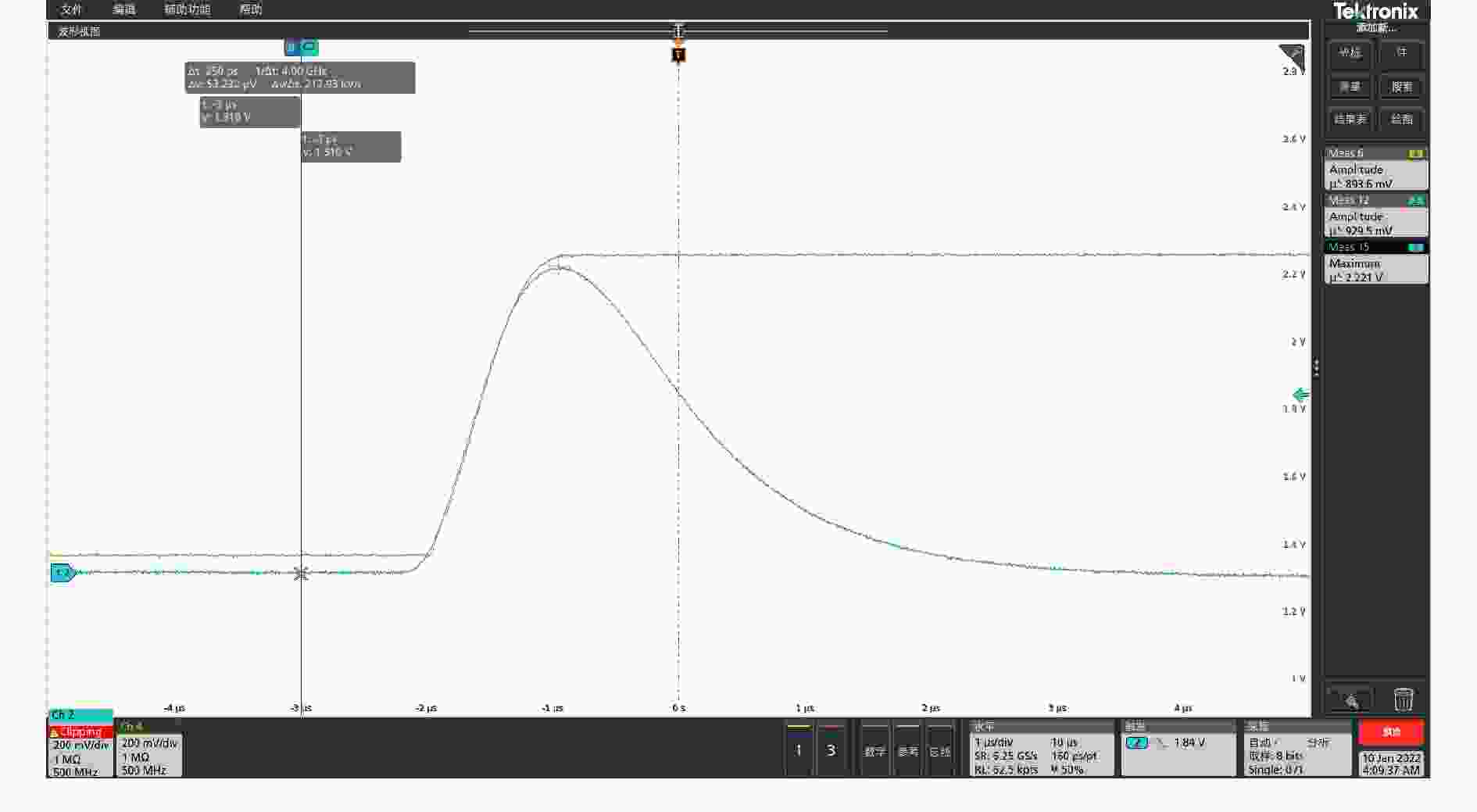

电路原理图及版图完成后进行了流片,并对流片完成的芯片进行实验室测试,测试现场及测试板,如图11所示。峰值保持电路的功能实现测试结果如图12所示,由于输入端存在失调,基线噪声不会引起峰检测电路的误触发,超过触发的信号可以正常触发。测试输入信号是基线电压1.3 V、上升沿1 μs左右的高斯波形信号,测试结果表明,峰值保持电路能够正常工作,峰值探测延迟时间小于30 ns,表明设计有良好的跟踪功能。

-

在输入动态范围内对电路的输出幅值及输入输出的线性进行测试和拟合,并根据测试结果计算非线性误差。图13为电路的线性拟合曲线,由计算可得,在电路的输入幅值范围为33~940 mV时,对应的非线性误差优于0.8%。表明该设计有良好的线性,可以满足设计需求。在峰值电压的保持过程中,输出端存在微弱的漏电流,电荷会缓慢泄放。下垂速率为8.6 μV/μs,根据探测器输出信号的计数率(20 kc/s)的要求,峰值信号保持时间小于50 μs,则峰值信号在保持时间内的变化小于0.43 mV。

测试结果与仿真结果相比存在一些误差,经过对比分析,误差来源包括:峰值保持电路的结构非对称性带来的失调电压误差,引起小信号测量的损失以及工艺误差和测试环境带来的误差。下一版的设计中将对每个误差来源进行优化和改进,提高设计的性能。

-

本文设计了一款用于塑闪阵列探测器能量信息读出的峰值保持ASIC芯片。通过对峰值保持电路的仿真及测试分析可得,峰值保持电路的输入动态范围为33~940 mV, 非线性误差优于0.8%,下垂速率好于8.6 μV/μs,峰值探测延迟时间好于35 ns,芯片单通道功耗为825 μW,各方面指标均满足设计需求。在之后的设计中,将对峰值保持电路的结构进行优化,提高电路的对称性,减小由于电路的不对称性带来的误差,进一步提高设计指标。

-

摘要: 塑料闪烁体阵列探测器(PSD,简称塑闪阵列探测器)的输出信号经过前置放大器和滤波成形电路后输出准高斯波形,利用峰值保持电路可对准高斯波形信号的峰值进行采样和保持,以便后续的电子学系统对其进行进一步的分析。本工作采用180 nm CMOS工艺设计并实现了一款峰值保持电路ASIC芯片,每通道主要由跨导放大器(OTA)、电流镜和充电电容三部分电路组成。实验室电子学功能和性能测试结果表明:峰值保持电路功能良好;输入动态范围为33~940 mV,非线性误差优于0.8%,下垂速率好于8.6 μV/μs,峰值探测延迟时间小于35 ns,芯片单通道静态功耗为825 μW,达到设计要求。

-

关键词:

- 塑料闪烁体阵列探测器 /

- 峰值保持电路 /

- 专用集成电路

Abstract: The output signal of PSD(plastic scintillation detector) is fed to the preamplifier and the shaping circuit to output a quasi-Gaussian waveform. The peak holding circuit can be used to sample and hold the peak value of the quasi-Gaussian waveform signal, so that the subsequent electronic system can further analyze it. This paper presents a peak holding circuit ASIC(application specific integrated circuit) chip which is designed based on 180 nm CMOS technology. Each channel of the ASIC includes an OTA(Operational Transconductance Amplifier) circuit, a current mirror circuit, and a charging capacitor. Laboratory electronics function and performance test results indicate that the function of the peak hold circuit is achieved. The input dynamic range is 33~940 mV, and the nonlinear error is better than 0.8%. The droop rate is better than 8.6 μV/μs, the peak detection delay time is lower than 35 ns, and the single-channel power consumption of the chip is 825 μW, which meets the design requirements. -

[1] 赵红赟. 新型塑闪阵列探测器读出系统的研究与实现[D]. 兰州: 中国科学院近代物理研究所, 2015. ZHAO Hongyun. The Research and Implementation of the Readout System for a New Plastic Scintillator Array Detector[D]. Lanzhou: Institute of Modern Physics, Chinese Academy of Sciences, 2015. (in Chinese) [2] 范一中, 常进, 郭建华, 等. 天文学报, 2022, 63(3): 13. doi: 10.15940/j.cnki.0001-5245.2022.03.002 FAN Yizhong, CHANG Jin, GUO Jianhua, et al. Acta Astronomica Sinica, 2022, 63(3): 13. (in Chinese) doi: 10.15940/j.cnki.0001-5245.2022.03.002 [3] 汪慎. VLAST硅微条径迹探测器模块原型设计及参数化模拟研究[D]. 合肥: 中国科学技术大学, 2020. WANG Shen. Prototype Module Design and Simulation of VLAST Silicon Tracker Detector[D]. Hefei: University of Science and Technology of China, 2020. (in Chinese) [4] 汪波, 王佳, 刘伟鑫, 等. 半导体检测与设备, 2019, 44(09): 728. doi: 10.13290/j.cnki.bdtjs.2019.09.013 WANG Bo, WANG Jia, LIU Weixin, et al. Semiconductor Testing and Equipment, 2019, 44(09): 728. (in Chinese) doi: 10.13290/j.cnki.bdtjs.2019.09.013 [5] 杨飞, 陈福彬. 北京信息科技大学学报, 2013, 28(01): 47. doi: 10.16508/j.cnki.11-5866/n.2013.01.006 YANG Fei, CHEN Fubin. Journal of Beijing Information Science and Technology University, 2013, 28(01): 47. (in Chinese) doi: 10.16508/j.cnki.11-5866/n.2013.01.006 [6] 肖云凤, 黄光明. 核电子学与探测技术, 2020, 40(02): 359. doi: 10.3969/j.issn.0258-0934.2020.02.030 XIAO Yunfeng, HUANG Guangming. Nuclear Electronics & Detection Technology, 2020, 40(02): 359. (in Chinese) doi: 10.3969/j.issn.0258-0934.2020.02.030 [7] BUCKENS P F, VEATCH M S. IEEE Nuclear Science Symposium and Medical Imaging Conference, 1991: 723. doi: 10.1109/NSSMIC.1991.259034 [8] HAAS W, DULLENKOPF P. IEEE Transactions on Instrumentation and Measurement, 1986, 35(04): 547. doi: 10.1109/TIM.1986.6831767 [9] ERICSON M N, SIMPSON M L, BRITTON C L, et al. IEEE Transactions on Nuclear Science, 1995, 42(05): 724-728. doi: 10.1109/23.467886 [10] WESSENDORF K O. LUND J C, BRUNETT B A, et al. Very Low-power Consumption Analog Pulse Processing ASIC for Semiconductor Radiation Detectors [C]//1998 IEEE Nuclear Science Symposium and Medical Imaging Conference(Cat. No. 98CH36255), 1998, 01: 488. DOI: 10.1109/NSSMIC.1998.775189. [11] DE GERONIMO G, O’CONNOR P, KANDASAMY A. Nucl Instr and Meth A, 2002, 484(1-3): 533. doi: 10.1016/S0168-9002(01)02059-9 [12] KRUISKAMP M W, LEENAERTS D M W. IEEE Transactions on Nuclear Science, 1994, 41(01): 295. doi: 10.1109/23.281513 [13] BAKER R J. CMOS:Circuit Design, Layout, and Simulation[M]. Beijing: Posts & Telecom Press, 2014: 165. [14] ALLEN P E, HOLBERG D R. CMOS Analog Circuit Design[M]. Beijing: Publishing House of Electronics Industry, 2011: 198. [15] 蒲天磊, 千奕, 苏弘, 等. 核电子学与探测技术, 2015, 35(11): 1146. doi: 10.3969/j.issn.0258-0934.2015.11.022 PU Tianlei, QIAN Yi, SU Hong, et al. Nuclear Electronics & Detection Technology, 2015, 35(11): 1146. (in Chinese) doi: 10.3969/j.issn.0258-0934.2015.11.022 -

下载:

下载:

甘公网安备 62010202000723号

甘公网安备 62010202000723号