-

对探测器信号进行高速采样,获取其全波形信息,进一步进行数字信号处理可以获得精确的时间信息[1]。基于开关电容阵列(Switched Capacitor Arrays,SCAs)技术可以对输入信号进行高速采样,并配以较低速的量化电路实现数字化过程[2],相对高速模拟数字变换器(Analog-to-Digital Converter,ADC)可以降低电路复杂度,降低功耗,提高电子学集成度。国外多个研究所都在积极进行此方向技术研究,并已在一些实验中采用了SCA芯片进行电子学设计,例如南极中微子观测站试验AMANDA中采用了ATWD芯片[3];南极宇宙线探测试验ANITA中使用了LABRADOR[4]芯片;MAGIC-II实验中采用了DRS芯片[5]。本人所在实验室目前正在SCA ASIC方向上展开研究,并已研制了原型芯片,其采样率达到5 GSps,通道采样深度为256 cells,单个SCA芯片集成8个采样通道[6]。

在之前的SCA ASIC测试中,我们利用FPGA (Field Programmable Gate Array)开发板临时搭建了简易的测试平台,为了便于对未来多个版本SCA ASIC进行系统化的测试,设计了具有一定通用性的数字读出模块和相应的上位机软件。该模块采用标准FMC (FPGA Mezzanine Card)连接器以便兼容当前及后续版本的SCA ASIC的测试,采用USB3.0接口用于数据传输。上位机软件具有简洁的用户界面,可以实现控制指令的发送及数据采集分析的功能。

-

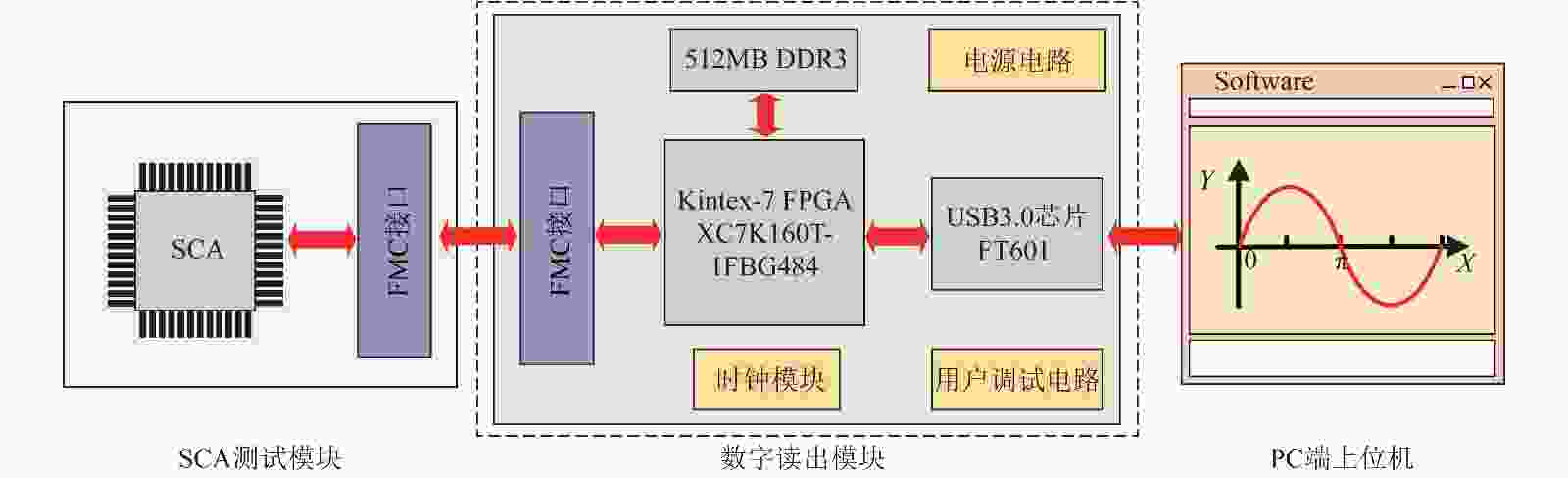

读出模块基于FPGA设计[7],使用片外DDR3芯片进行数据存储,使用USB3.0接口作为主要接口进行数据传输,读出模块主要包含五部分:电源电路、接口电路、时钟电路、存储电路、用户调试电路;数字读出模块的结构框图如图1所示。

其中数字读出模块采用了开放式的接口和SCA前端测试模块连接,前端测试模块获取的数据经过FPGA的简单处理,缓存至DDR3外部存储芯片中,再由USB3.0控制芯片读出至上位机软件进行分析。由于本设计中采用了USB3.0的接口,接口实际传输速率高达350 MB/s,而第2版SCA芯片的输出接口为100 MHz的串行接口,可使用USB3.0接口实时读取。考虑到将来芯片的改版升级工作,当输出速率大于350 MB/s时,可将数据先缓存至DDR3后再由USB接口读出。

-

在设计供电系统时需要考虑各器件的功耗,对纹波的要求以及对上电顺序的要求。总的来说对于模拟器件以及其他对电源质量要求较高的芯片使用LDO(low dropout regulator)进行供电,其余部分使用开关电源供电,由于LDO芯片是线性电源,输入输出的压差将以热的形式消耗,所以在设计的时候需要保证压差不能太大,一方面是为了减少整个系统的功耗,另一方面是为了减小LDO芯片的发热情况,以免损坏芯片。

此数字读出模块的供电系统有两部分任务,一是为数字读出模块提供所需的电压;二是为SCA前端测试模块提供稳定可靠的电压。对于数字读出模块,主要考虑FPGA芯片的供电。其中VCCINT为内核电压,VCCBRAM为片内BRAM的核心电压,其电压值较小,但电流值根据片内资源消耗情况最多可达到数10 A以上;VCCO为IO接口电压,可以根据实际需求进行选择,在本设计种为了满足一定的兼容性,提供了2.5和3.3 V两种电压,可通过电阻进行选择。在FPGA的上电过程中,有如下所示的上电顺序要求[8],电源芯片之间的启动顺序可利用芯片的使能端引脚进行控制。

$$\begin{array}{l} \;\;\;\;\;\;\;\;\;\;\;\;{\rm{VCCINT}} \to {\rm{VCCBRAM}} \to {\rm{VCCAUX}} \to {\rm{VCCAUX\_IO}} \to {\rm{VCCO ,}}\\ {\rm{VCCINT}} \to {\rm{VMGTAVCC}} \to {\rm{VMGTAVTT}}{\text{或}}{\rm{VMGTAVCC}} \to {\rm{VCCINT}} \to {\rm{VMGTAVTT}}{\text{。}} \end{array} $$ 对于前端SCA测试模块,其需要的电压有5种:±5, +3.3, +1.8和+1.0 V。数字读出模块提供的电压种类无法做到面面俱到,故最终决定使用三种较为常用的电压:+5, –5, +3.3 V。前两种电压用于运算放大器的供电,+3.3 V的电压适用于大多数芯片。SCA测试模块利用板载的LDO芯片将3.3 V电压转换成+1.8和+1.0 V电压。模拟电路对电源质量要求高,要求电源纹波小,所以给前端测试模块供电的电源不与数字读出模块电源混合使用,并且全部使用LDO芯片供电。数字读出模块的供电系统如图2所示。

其中供电系统的第一级输入,一般采用的都是实验室的直流稳压电源。本设计在采用此种供电方式的同时,增加了USB供电的方式,使用了当前较为流行的Type-c接口。Type-c接口支持正反插,使用起来方便快捷,在单独使用数字读出模块或前端测试模块不需要±5 V电压时(不使用运放时)可以直接通过Type-c接口为系统供电。

-

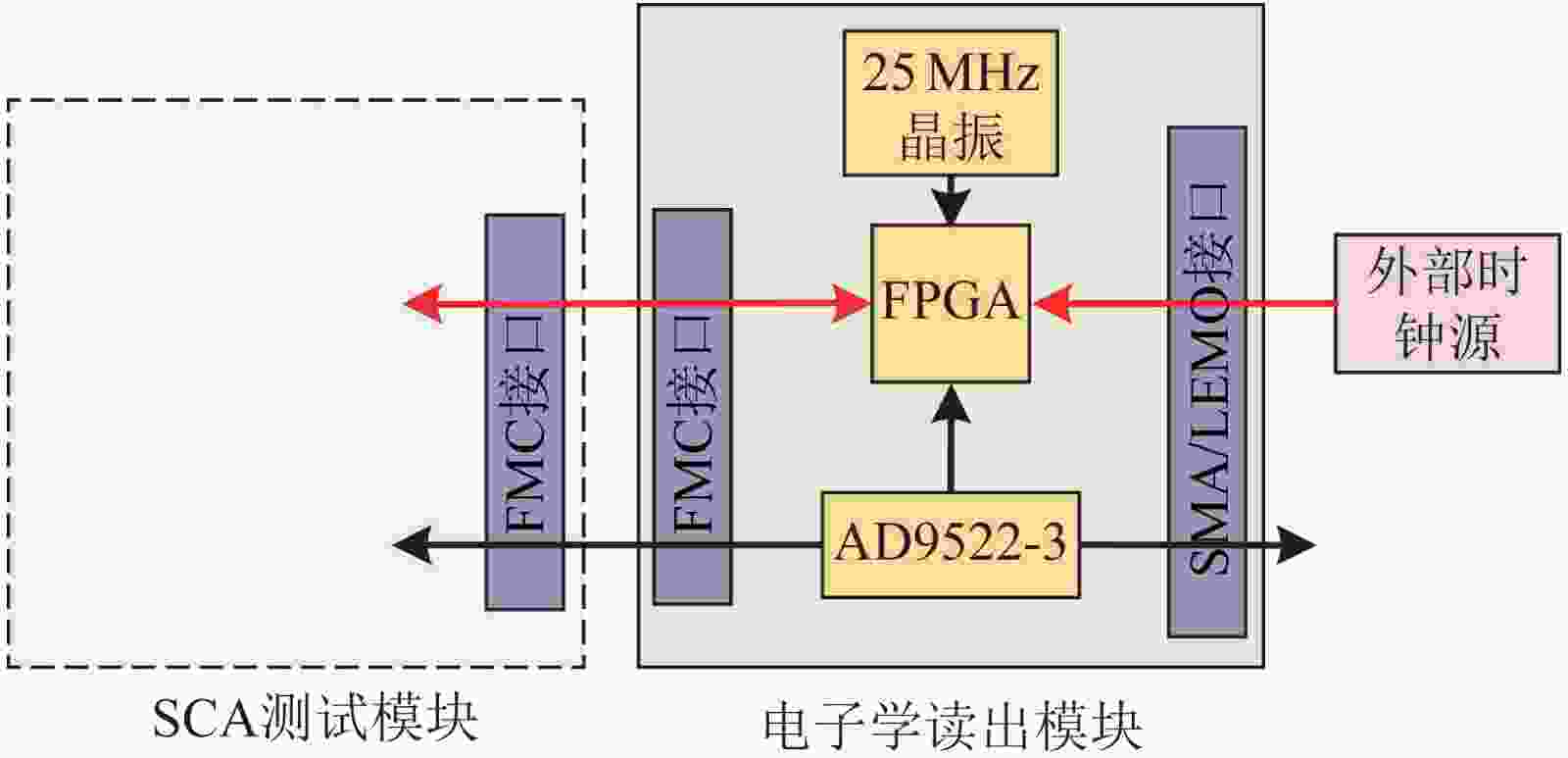

数字读出模块的时钟系统有两个作用,一是为FPGA提供系统时钟,二是为SCA提供采样时钟。此部分一共涉及3种芯片(SCA,FPGA,AD9522-3)与3种接口(FMC,SMA,LEMO)。其中AD9522-3是ANALOG DEVICE公司生产的一款时钟发生芯片,提供多路输出时钟分配功能,片内VCO的调谐频率为1.72~2.25 GHz。输出时钟可自由配置成单端或差分输出,并具有亚皮秒级别的抖动性能。每组时钟可自由配置其分频系数和相位。数字读出模块的时钟分布如图3所示。

其中:

(1) 以FPGA为对象:板载25 MHz无源晶振为其提供了基础时钟,用于配置模块中的其他芯片(包括AD9522-3);AD9522-3产生的高质量时钟信号可作为FPGA的系统时钟,保证其稳定运行;外部时钟信号可以通过板上的SMA,LEMO接口传入FPGA,其中SMA接口传递单端时钟信号,LEMO接口传递差分时钟信号。由于FPGA内部集成了PLL,所以也能够在片内产生时钟信号并通过SMA,LEMO接口送至外部。同理,前端测试模块也可以通过FMC连接器上的专用时钟引脚向FPGA传递时钟信号或接收FPGA产生的时钟信号。

(2) 以AD9522-3为对象:AD9522-3可为三部分提供精准稳定的时钟信号,可以直接为FPGA提供系统时钟;通过SMA,LEMO接口向外部提供时钟;通过FMC连接器向前端测试模块提供时钟。

对于正弦波输入的ADC测试系统,时钟晃动会导致采样时刻的不确定从而带来孔径误差,孔径误差和信噪比之间的关系如下:

$${\rm{SNR}} = {\rm{ - }}20\lg 2{\rm{\pi }}{f_{{\rm{in}}}}{t_{\rm{a}}},$$ (1) 其中:SNR为信噪比;fin为输入信号频率;ta为时钟jitter,而理想情况下信噪比和有效位之间有如下关系

$${\rm{ENOB}} = \frac{{{\rm{SNR}} - 1.761}}{{6.02}}{\text{。}}$$ (2) 当输入信号频率为350 MHz时,若希望有效位达到8位,则时钟的jitter应小于1.45 ps。对于SCA ASIC,采样单元的控制信号由内部DLL产生,外部输入的时钟信号仅作为DLL的参考时钟,参考时钟的jitter主要对最后一个采样间隔产生影响。

-

读出模块接口分为两类:用于连接前端测试模块的接口,用于和上位机连接的接口。与前端测试模块相连的接口采用LPC规格的FMC连接器,其遵循ANSI/VITA 57标准,专用于FPGA与其他子卡之间的连接。为了更好地适用于SCA ASIC的测试,根据前端测试模块的需求,本设计对官方定义的引脚稍作修改。首先去除了VREF_A_M2C,PRSNT_M2C_L与PG_C2M信号,其次修改了电源供电电压的大小,将3P3V电压定义成+5 V,将12P0V定义成–5 V,VADJ设置成固定3.3 V。由于前端测试模块没有搭载需要JTAG接口的器件,故将JTAG引脚的信号线定义成用户IO。经过此番修改,原官方定义的电源与地的引脚位置并没发生改变,仍然具有一定的兼容性。图4为FMC连接器的原定义与修改后定义的对比示意图。

数字读出模块通过USB3.0接口与上位机进行连接,本设计使用FTDI公司生产的FT601芯片。该芯片将USB的串行数据转换成32位并行数据接入FPGA,FPGA只需将其当做一个位宽为32 bit的FIFO处理即可,所有USB通信协议将在芯片内自行完成转换。并行数据同步时钟可设置为100 MHz,理论最大传输速率高达400 MB/s[9]。本设计除了使用了USB接口以外,还设计了串口和SFP接口以适用于不同的使用场景。值得一提的是,数字读出模块不仅可以用于SCA ASIC的测试,还可以兼容实验室设计的ADC ASIC测试模块和其他使用FMC连接器的前端测试模块。

-

FPGA为数字读出模块的核心处理器件,用来完成SCA、DAC、时钟芯片的配置和数据的处理与传输任务。本设计使用的FPGA芯片为Xilinx公司的XC7K160T-2FBG484。

前端测试模块搭载了实验室自主设计的第2版SCA芯片,该芯片共有8个通道,每个通道串行输出。FPGA对输入数据进行选通再通过内部的异步FIFO转换成32位并行数据,USB控制逻辑在FT601输出的数据同步时钟下将FIFO内的数据传出。另外FPGA还需要对前端测试模块上DAC芯片,时钟芯片及SCA芯片发送配置信号。配置信号的内容由上位机发送的控制信号中解析而来,上位机发送的32位指令进入指令分析逻辑,指令的24~31位表示时钟芯片的配置信息;16~23位表示DAC的配置信息;8~15位表示SCA的配置信息;0~7位暂未使用。整个FPGA内部逻辑结构如图5所示。

-

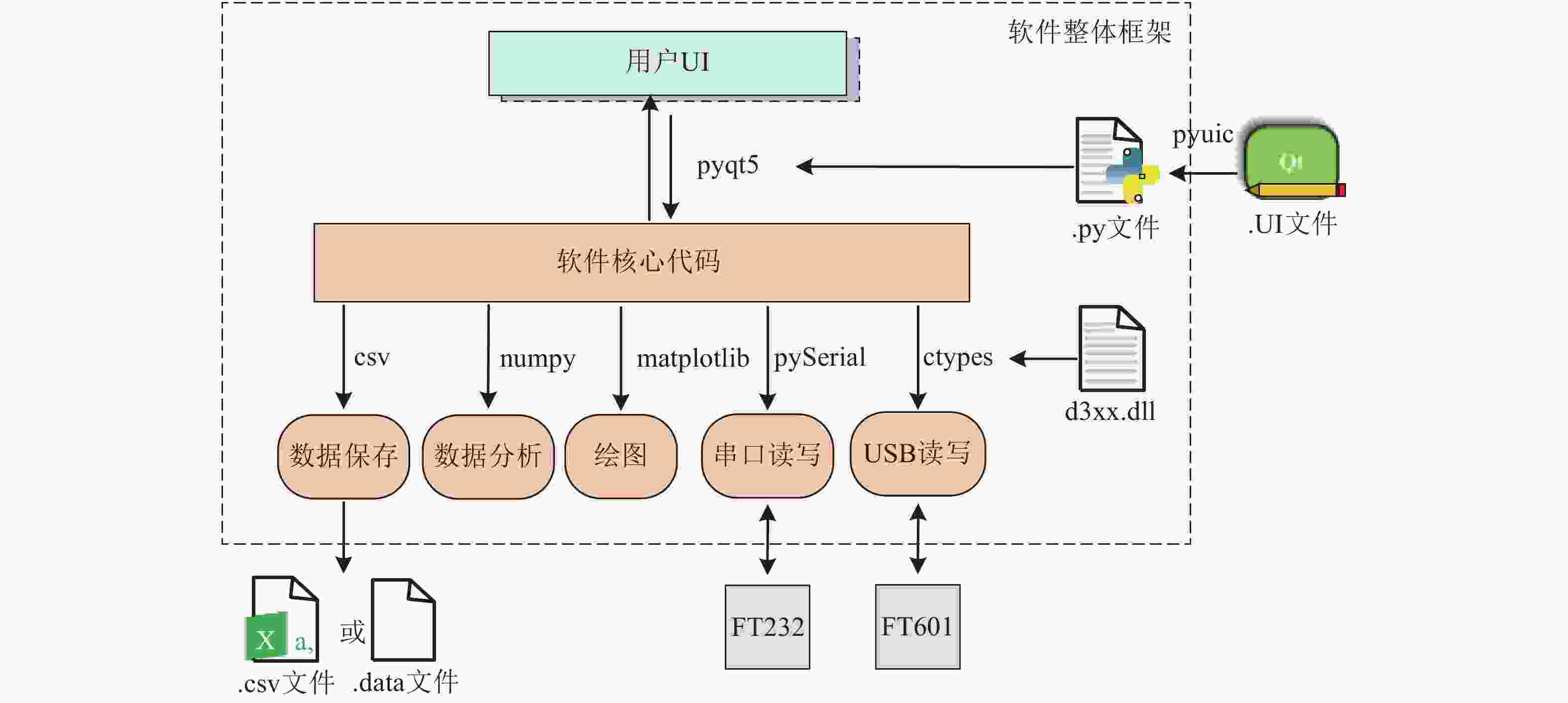

上位机软件基于Python3.7设计,软件具有如下功能:对FT601芯片进行读写操作(包括数据读取和控制指令的发送),对读取的数据进行保存,对数据进行计算分析、绘图功能以及简洁的用户界面。Python拥有功能强大的标准库以及众多第三方库,需要根据设计需求选择相应的拓展库实现不同的功能。

对于FT601芯片的读写,FTDI公司提供了FTD3XX驱动和一个动态链接库文件(d3xx.dll)。PC端安装好驱动程序后,通过调用d3xx.dll文件里封装的API函数即可实现芯片的访问与控制[10]。Python中的Ctypes模块可实现调用动态链接库文件的功能。对于数据的保存,提供了两种保存类型:逗号分隔值(csv)文件和二进制文本文件。前者通过csv模块实现。后者使用标准库中的write方法实现。对于数据的分析使用Numpy库,Numpy底层基于C语言编写,运行效率更高,另外Numpy内部解除了全局解释器锁,使其运行速度不受Python解释器的限制。对于绘图功能,使用Matplotlib绘图库实现。对于用户界面,使用QT框架进行设计。这是一个专业的跨平台C++图形用户界面应用程序开发框架,其中的QT Designer工具可以让开发者通过拖拽控件的方式实现UI的设计,设计生成的UI文件利用pyqt5库中的pyuic工具转换成.py文件,即可在Python中调用。

在整个软件框架中,虽然所有代码均通过Python编写,但底层芯片的读写、数据运算、用户UI部分的实现,最终基于C或C++,保证了软件的运行效率。另外,软件并不仅仅适用于SCA ASIC的数据读出,对于所有兼容数字读出模块接口的测试模块都可以使用此软件进行数据读出。软件整体框架如图6所示。

-

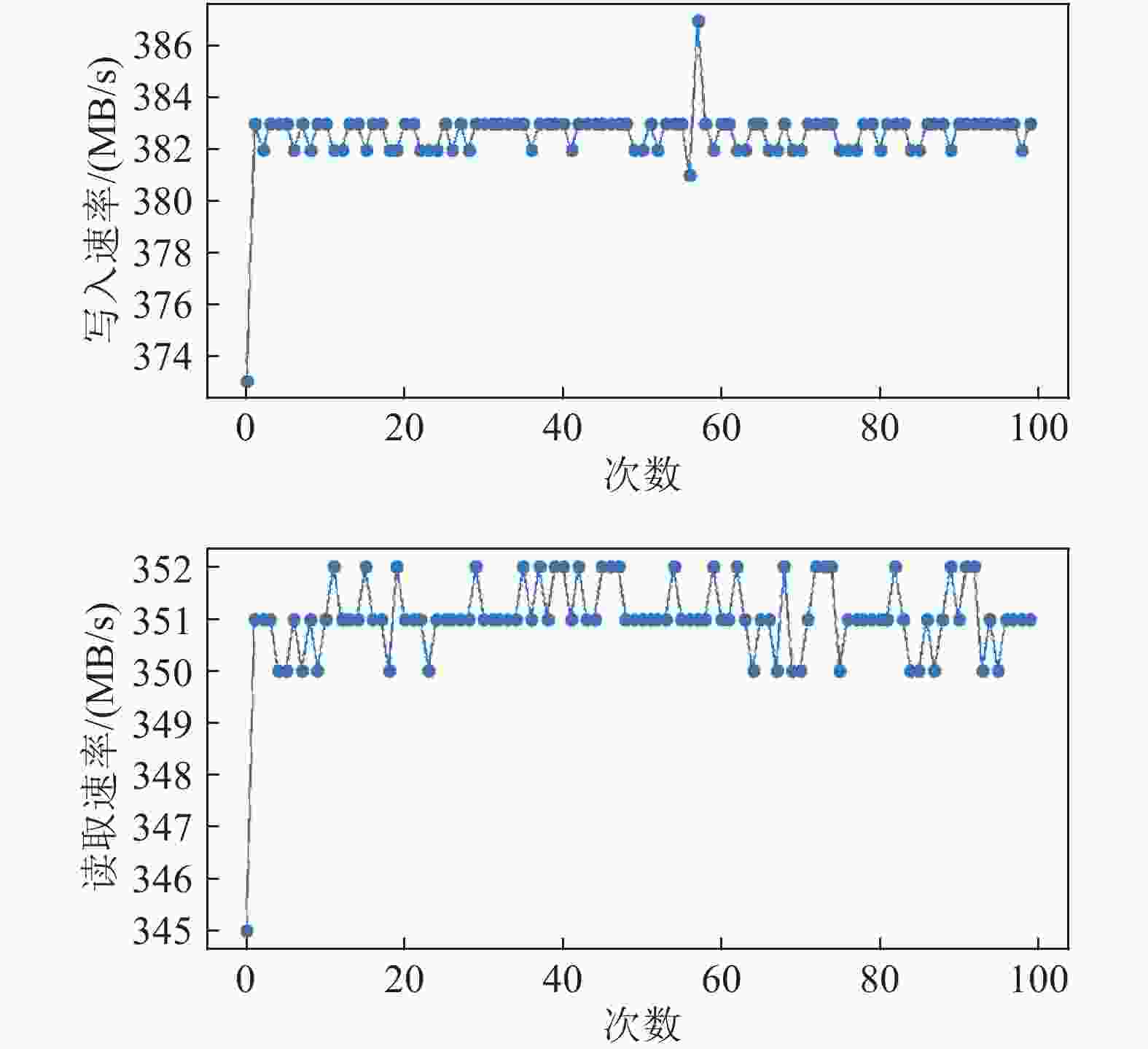

将FT601芯片配置成“245同步FIFO”模式,将输出时钟配置成100 MHz。通过USB3.0数据线将数字读出模块连接至测试机,测试机的配置为:Windows10 Education,Version 1809(x64),Intel® Core i5-3470, 3.2 GHz, 8 GB Memory。D3XX驱动版本为1.3.0.2。使用FTDI公司提供的FTDI data streamer软件进行测试。

首先进行连续写入测试,对USB设备循环写入100次,每次写入16 MB数据,记录每次写入的速率并对结果求平均值。再进行连续读取测试,对USB设备循环读取100次,每次读取16 MB数据(FPGA内部产生测试用的100 MHz,32 bit位宽的数据),记录每次读取的速率并对结果求平均值。测试结果表明,USB接口的连续写入速率约为383 MB/s,连续读取速率约为351 MB/s。图7为USB接口读写速率测试结果。

-

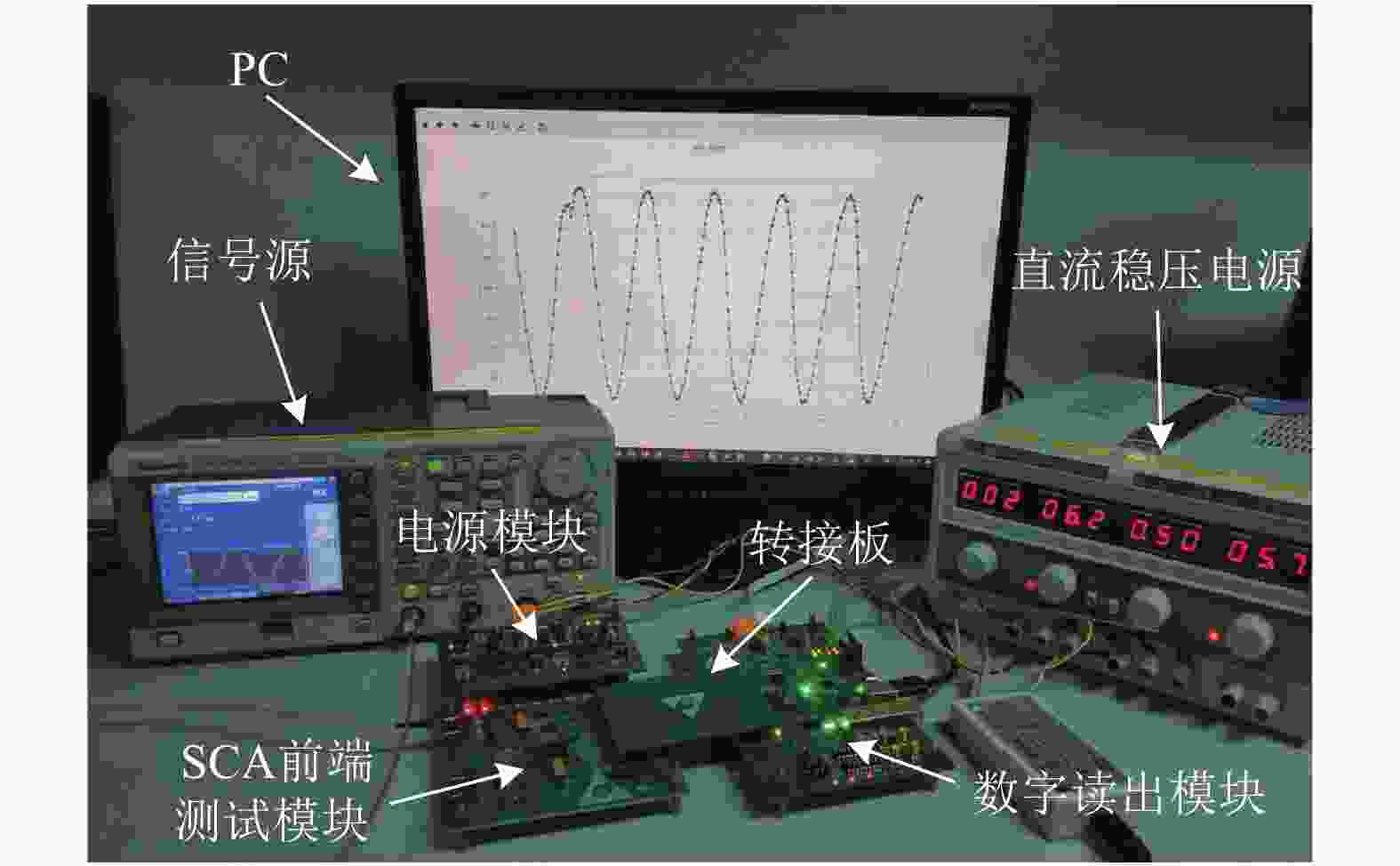

本测试使用的是实验室设计的第2版SCA前端测试模块,由于SCA测试模块先于数字读出模块设计,其FMC连接器与数字读出模块的FMC连接器同为母座,且未将板上电源连接至FMC连接器,所以在使用时需要通过连接板将前端测试模块与数字读出模块相连,还需要单独使用电源模块进行供电。使用实验室的直流稳压电源输出±6 V的电压接入电源模块,电源模块上的LDO芯片将电压转换成SCA测试模块所需要的±5, +3.3, +1.8和+1.0 V电压。数字读出模块直接通过Type-c接口的USB线连接通用的5V2A电源适配器进行供电。完整的测试平台如图8所示。

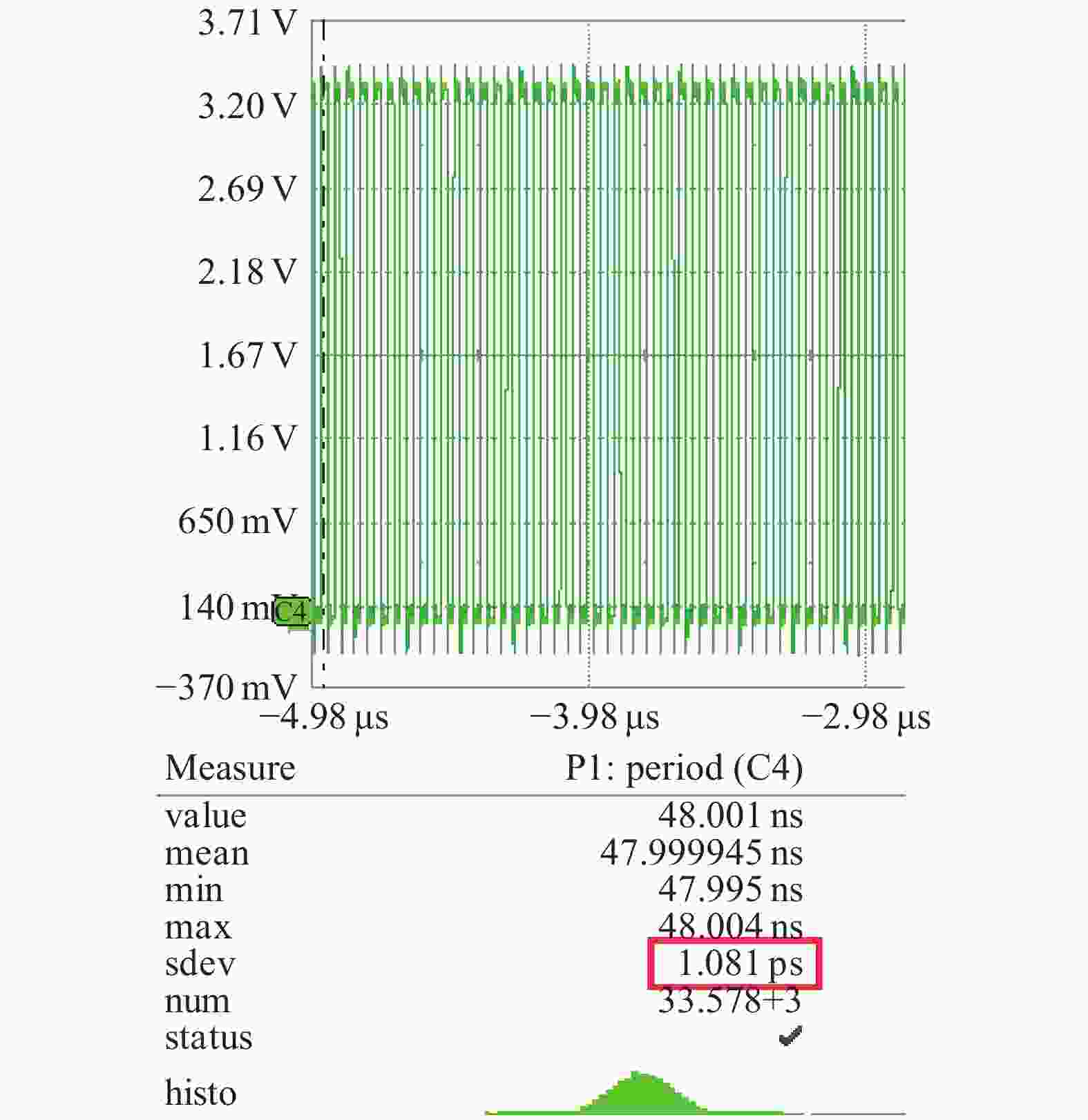

首先对SCA芯片的采样时钟进行了测试,使用示波器对其进行观察,可以看出时钟jitter为1.081 ps,满足1.5 ps的设计指标。测试结果如图9所示。

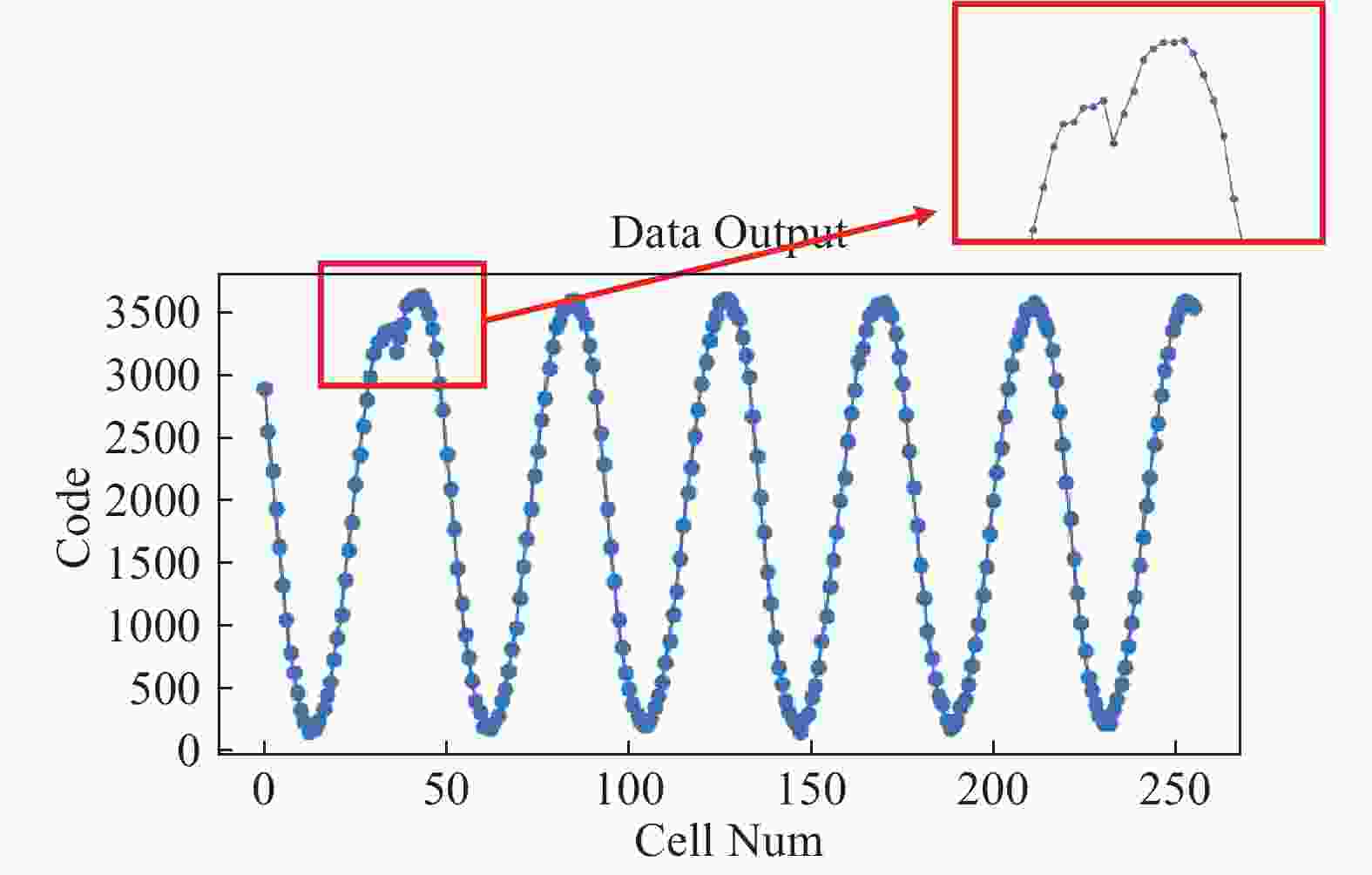

其中使用AFG3252任意波形发生器产生一个频率为120 MHz,幅度接近满量程的正弦波输入至SCA前端测试模块,SCA芯片的采样频率为5 GSps,使用本设计中的读出模块进行数据读出,再由上位机软件进行采集与绘图,采集到的的波形如图10所示。

SCA芯片内部每个通道各有256个采样单元(Cell),所以一共输出256个码值。由于SCA的256个Cell处于循环采样的状态,所以在采样停止的位置数据不连续,在输出波形上的体现则是存在断点。另外由于在芯片的制造中存在工艺误差,256个Cell之间的采样间隔存在一定偏差,导致输出波形有所失真,这也与测试结果相吻合。虽然采样间隔存在偏差,但是这种偏差是固定的,可以通过基于超定线性方程组的算法[11]计算出实际的采样间隔,再利用计算出的间隔对采样点在时间上进行修正。

-

本人所在实验室正在展开SCA ASIC的研究与设计工作,为了满足SCA芯片的测试需求设计了后端读出模块以及相应的测试软件。后端读出模块采用FMC连接器与SCA测试模块相连,SCA输出的数据经过FPGA的简单处理通过USB3.0接口传输至上位机软件。上位机软件可以实现数据的分析,保存以及绘图等功能。此外还对SCA前端测试模块和后端读出模块进行了联合调试,测试结果表明读出模块工作正常,SCA输出波形符合预期分析。

-

摘要: 高速开关电容阵列(SCA)具有高速采样、低功耗的特点,基于SCA的高速波形数字化是目前高精度时间测量的一个重要研究方向。为此,我们开展SCA芯片的研究,目前已设计完成原型ASIC设计,并正在进行后续版本的改进设计。为便于未来多版本ASIC的测试和评估,需设计具有一定通用性的数字读出模块,本论文工作主要介绍此模块的设计工作以及相应的数据读出软件。数字读出模块基于FPGA实现对待测ASIC的控制、配置及数据读出,采用DDR3片外存储芯片,使用USB3.0等接口进行数据传输;上位机软件基于Python3.7设计,实现了数据采集与波形绘制等功能。目前已使用设计完成的数字读出模块对第2版SCA ASIC进行了初步的测试,测试结果表明,此读出模块工作正常,且SCA芯片输出结果符合预期。Abstract: Switched Capacitor Array (SCA) features high-speed sampling and low power consumption. High-speed waveform digitization based on SCA is an important research direction for high-precision time measurement. We are designing the SCA ASIC chips, of which several prototypes have been designed and the improvements are ongoing. In order to test and evaluate the future SCA ASIC chips, it is necessary to design a digital readout module with good compatibility. This paper presents the design of the readout module and the data readout software. The digital readout module integrates the functionality of the control, configuration and data readout of the ASIC under test within one FPGA device. A DDR3 chip is used for data caching, and a USB3.0 interface is designed for data transmission. The readout software is designed based on Python3.7 and contains the functions such as data acquisition and waveform drawing. This module was successfully used in the initial testing of the second version of the SCA prototype ASIC, and the test results indicate that the readout module works as expected.

-

Key words:

- ASIC test /

- switched capacitor array /

- FPGA /

- USB3.0 /

- Python

-

[1] GENAT J F, VARNER G, TANG F, et al. Nucl Instr and Meth A, 2009, 607(2): 387. doi: 10.1016/j.nima.2009.05.193 [2] ZHANG H Y, DENG Z, LIU Y N. Chinese Physics C, 2016, 40(7): 076102. doi: 10.1088/1674-1137/40/7/076102 [3] KLEINFELDER S. IEEE Transactions on Nuclear Science, 2003, 50(4): 955. doi: 10.1109/TNS.2003.815137 [4] VARNER G S, RUCKMAN L L, NAM J W, et al. Nucl Instr and Meth A, 2007, 583(2-3): 447. doi: 10.1016/j.nima.2007.09.013 [5] PEGNA R, BARCELO M, BITOSSI M, et al. Nucl Instr and Meth A, 2007, 572(1): 382. doi: 10.1016/j.nima.2006.10.375 [6] 秦家军. 基于开关电容阵列的高速波形数字化ASIC研究[D]. 合肥: 中国科学技术大学, 2018. QIN Jiajun. Research of Waveform Digitization ASIC Based on Switched-Capacitor Arrays[D]. Hefei: University of Science and Technology of China, 2018. (in Chinese) [7] ZHAO Lei, LIU Shubin, LI Yusheng, et al. A General Purpose Test Apparatus for High-Speed, High Resolution Analog to Digital Converters Based on IEEE Standard[C]// International Conference on Electronic Measurement and Instruments, 2007. ASSCC’07. IEEE Asian, IEEE, 2007: 179. [8] Xilinx, Inc. Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics, DS182- Kintex-7 FPGAs Data Sheet: DC and AC Switching Characteristics (v2.16.1). [EB/OL].[2019-04-13]. https://china.xilinx.com/support/documentation/data_sheets/ds182_Kintex_7_Data_Sheet.pdf. [9] FTDI chip, Inc. FT600Q-FT601Q IC Datasheet (USB 3.0 to FIFO Bridge), FT600Q-FT601Q SuperSpeed USB3.0 IC Datasheet.[EB/OL]. [2019-04-13]. https://www.ftdichip.com/Support/Documents/DataSheets/ICs/DS_FT600Q-FT601Q%20IC%20Datasheet.pdf. [10] FTDI Chip, Inc. Application Note AN_379 D3XX Programmers Guide, Version 1.7, D3XX Programmer's Guide. [EB/OL]. [2019-04-13]. Version 1.7. https://www.ftdichip.com// Support/Documents/ProgramGuides/AN_379%20D3xx%20Programmers%20Guide.pdf. [11] CHENG B, ZHAO L, QIN J, et al. Nucl Instr and Meth A, 2019, 916: 71. doi: 10.1016/j.nima.2018.11.029 -

下载:

下载:

甘公网安备 62010202000723号

甘公网安备 62010202000723号