-

波形数字化技术是未来物理实验装置中前端读出电子学非常重要的发展趋势之一,通过获取的探测器输出信号的原始波形,物理学家可以得到其携带的所有物理信息,如幅度信息(能量、位置)、时间信息[1-2]。传统基于Flash ADC的波形数字化技术不仅分辨率低,集成度低,成本高昂,而且随着采样率的提高功耗越来越大[3],以及带来的高速数据缓存、数据传输电路的系统复杂问题,已经不能满足未来物理实验装置发展的需求。

基于开关电容矩阵(Switched Capacitor Array, SCA)的波形数字化技术是一种新颖的技术路线[4-5]。它是基于高速模拟取样、存储,然后配以合适速度的ADC(Analog-to-Digital Converter)进行模数变换的技术路线。这种方法的最大优点是用高速模拟取样、存储技术解决了Flash ADC高釆样率和高精度模数转换之间的矛盾。SCA芯片自身功耗低且避免采用高速ADC,从而降低了系统的总功耗。SCA+ADC的技术路线已渐渐被广泛关注,一些大的物理实验装置探测器读出中也开始对此方法进行应用[6-7],其中比较典型的如:瑞士MEG(Mu-E-Gamma)实验中使用了DRS(Domino Ring Sampler)芯片[8],位于南极中微子探测AMANDA (Array of 80 Optical Modules Arranged)实验中使用了ATWD(Analog Transient Waveform Digitizer)芯片[9],位于地中海天体物理ANTARES(Arizona-NOIRLab Temporal Analysis and Response to Events System)实验中使用了ARS1(Analogue Ring Sampler 1)芯片[10]。该技术的突破和成熟,将会是粒子物理实验装置中探测器前端读出电子学的一个重大进展。

DRS4(Domino Ring Sampler 4)是一款由瑞士PSI (Paul Scherrer Institut)研究所研发的商用的先进SCA超高速波形数字化芯片,该芯片具有9路模拟差分输入通道,最高采样率为5 GHz,模拟输入带宽可以达到950 MHz,并且具有极低的功耗[11]。本文设计了一种基于DRS4芯片的超高速波形数字化数据采集电路。本次设计采用运算放大器构成的比例运算电路来提取探测器输出的脉冲信号,并且通过DRS4芯片将这些快速变化的信号用开关电容阵列存储,然后将存储的电压信号低速(如33 MHz)地输出到ADC进行模数转换,这样就可以使用较低采样率但精度高的ADC来进行模数转换,最后通过FPGA(Field-Programmable Gate Array)对这些数字信号进行处理。该电路适合于多种场合的物理实验装置的探测器前端读出电子学中,如塑料闪烁体探测器(Plastic Scintillator Detector, PSD),溴化镧晶体探测器(LaBr3 Detector),硅酸钇镥晶体探测器(LYSO Detector)等探测器的信号读出。该电路非常适合提取和处理探测器输出的窄脉冲信号,以满足物理实验中高采样率、多参数测量等要求。本文主要探讨基于DRS4 的波形数字化电路设计以及相关技术。

-

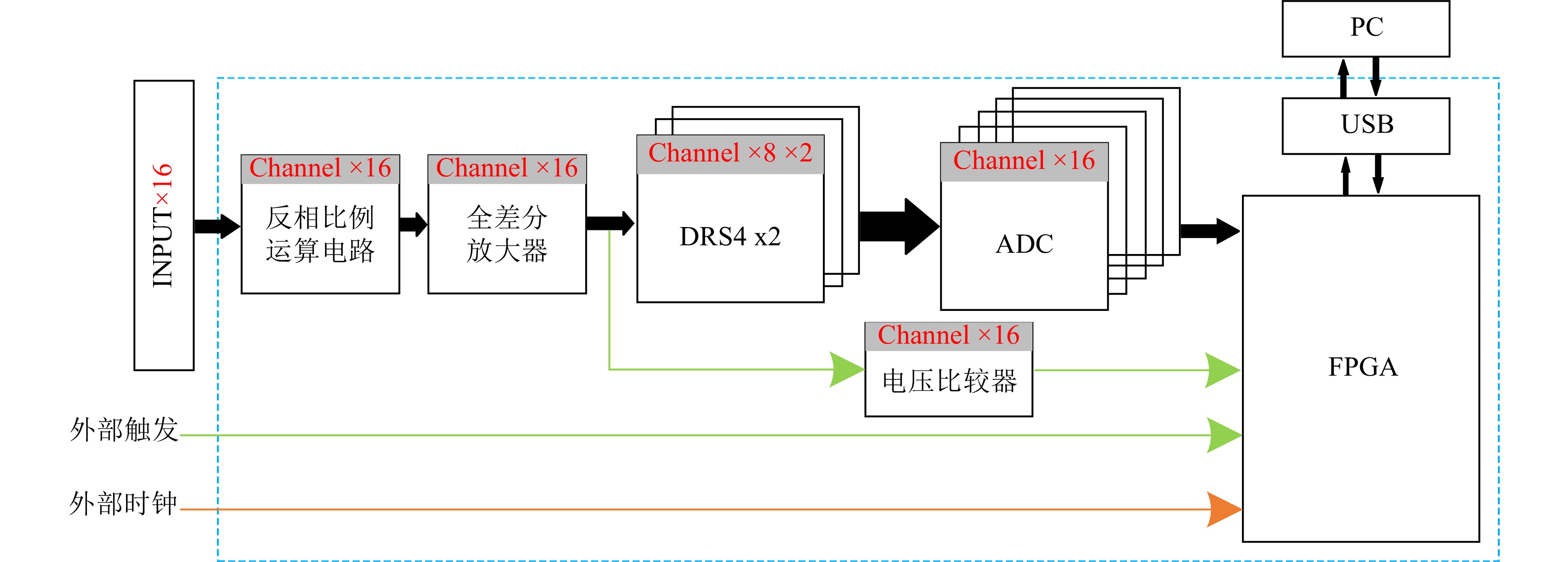

基于DRS4芯片设计了高速波形数字化数据采集电路,电路设计框图如图1所示,主要由模拟信号调理电路、DRS4、ADC、比较器、FPGA及接口电路组成。为了能够提取探测器输出的微弱电荷脉冲信号,并且能够有效驱动下一级,我们将模拟信号调理电路第一级设计为反相比例运算电路来提取16路PSD的输出信号,然后经过全差分放大器将单端信号转换成差分信号作为DRS4的输入。DRS4以700 MHz至5 GHz可调的采样频率对全差分放大器输出的信号进行全波形采样,直到有效事例到来时,全差分放大器的正向输出通过电压比较器产生触发信号。当FPGA收到信号自触发信号或者外部触发信号时,控制DRS4以较低的频率(如33 MHz)输出电容阵列存储的电压,然后ADC将此时的模拟信号转换成数字信号,ADC选用的型号是AD9249,具有16个输入通道,输出为16路串行输出。在FPGA中对ADC输出的数字信号进行数字滤波,然后保存到16个FIFO中。最后FPGA轮回读取出数据,并对其获取峰值、能量等信息。最后FPGA通过USB和上位机交互信息,上位机不仅可以获取PSD波形的重要信息,还可以用来灵活地配置DRS4的采样频率、采样深度等工作模式。需要处理多路(超过16路)PSD信号时,可以使用多块电路板并联,通过共用同一个外部时钟作为系统时钟,从而实现各个电路板之间的时钟同步。

-

本系统的主要参数总结:

1) 16通道,每个通道1 024个采样深度;

2) 采样率在700 MHz~5 GHz可调;

3) 模拟宽带实测在0~200 MHz失真度误差小于0.7 dB,在0~100 MHz失真度误差小于0.2 dB;

4) 在0 V直流输入时的系统电子学噪声小于0.5 mV。

-

由于PSD输出的信号是频率为兆赫兹的电荷脉冲信号,为了很好地提取该信号,并且满足DRS4的差分输入要求,设计了信号提取电路和单端转差分信号电路,如图2示。为了满足输入信号较宽的带宽,第一级采用AD8001AR[12]电流反馈型运算放大器构成

${A_{{\text{V1}}}} = - {R_{{\text{f}}1}}/{R_1} = - 1$ 的反相比例运算电路来提取PSD输出信号。通过PSpice仿真得到其频带宽度如图3红色“X”标记曲线所示。输入信号提取后,通过THS4508全差分放大器将单端信号转差分信号,其中${A_{{\text{V2}}}}$ 为差模放大倍数,${A_{{\text{V2}}}} = {R_{{\text{f}}2}}/{R_2} = 1$ ,${V_{{\text{com}}}}$ 为共模输入电平。输入信号经过反相比例运算电路和全差分放大器的频带宽度如图3蓝色“□”标记曲线所示,系统的−3 dB带宽为596 MHz。 -

DRS4读取储存在开关电容阵列波形的触发由板上信号自触发和外部触发两种。可以通过上位机来选择使用哪种触发模式。自触发信号由电压比较器实现,当探测器输入信号大于设置的阈值时,比较器输出高电平脉冲作为自触发信号。如图4所示,外部触发信号或者自触发信号有效时,等待一定的时间后,DRS4开始读出存储在SCA中的波形数据。

-

DRS4的样频率由外部输入的参考时钟(REFCLK)的频率决定,当REFCLK的频率为

$f$ 时,DRS4根据自身PLL产生频率为2 048 ×f的时钟对8个输入(Input)进行采样,如图5所示。Domino wave采样频率根据REFCLK的频率从700 MHz~5 GHz可调。DRS4芯片采样部分主要由Domino 环和开关采样电容阵列两部分组成,波形存储(Waveform stored)和读出(Readout)如图6所示,Domino环移位由内部PLL产生一个700 MHz~5 GHz的时钟来控制开关电容阵列对输入波形各个电压进行存储。其中开关电容阵列个数即采样深度可配置成1 024~8 192个。当DRS4收到读出信号时,立即停止采样,此时以读出移位时钟 (Readout Shift Clock)的频率输出已经存储在开关电容阵列中的电压。整个过程完成了由输入信号的700 MHz~5 GHz采样到输出信号的33 MHz读出。

-

DRS4将采集到的输入信号的电压值保存在开关电容阵列中,并且其采样频率可以通过上位机从700 MHz到5 GHz灵活配置,很方便对不同频率的输入信号进行采样,然后通过较低速时钟(如33 MHz)将这些开关电容阵列存储的电压值读出。如图7所示,实现了从时间为

$t$ 的输入信号展宽成时间为$kt$ 的输出信号,系数$k$ 由采样频率${f_{\text{s}}}$ 和输出时钟频率${f_{\text{o}}}$ 共同决定,可从几十到几百倍,如式(1)所示。如图8所示,DRS4在采样频率为4.096 GHz且读出频率为 33 MHz时,某一个通道的实际测量值,红色形曲线输入信号,其周期为100 ns,幅值为0.5 V的正弦波。黑色曲线是实测输出信号,其周期为12.4${\text{μ}}{\rm s}$ ,幅值为0.506 V的正弦波。$$ k = {f_{\text{s}}}/{f_{\text{o}}} $$ (1) -

FPGA主要用来实现各个模块的驱动,数字信号的处理和各个模块控制的工作。FPGA选择的型号是Xilinx 公司的XC7K325T-2FFG900I。图9给出了FPGA设计框图。复位顺序模块主要用于处理各个模块的同步复位,首先由硬件异步复位转变成系统时钟控制的同步复位,待DAC为其他模块输出稳定的参考电压后,再控制DRS4模块复位,然后ADC再复位。时钟管理模块用来将系统时钟通过IP(Intellectual Property)核生成不同频率的时钟为各个模块提供工作时钟,执行顺序模块控制数据的流向,FPGA接收到触发信号后,控制ADC将DRS4开关电容阵列中存储的电压值先进行模拟信号转数字信号,FPGA得到数字信号后对数据进行信息提取,如能量信息、时间信息等,最后通过USB(Universal Serial Bus)接口发送给上位机。上位机通过USB下发命令给FPGA,用来设置DRS4的采样频率、采样深度等不同工作模式。FPGA控制DAC模块输出不同的电压值,给全差分放大器、DRS4、ADC提供高精度偏置电压和触发电路中比较器的阈值电压。DRS4驱动模块主要是配置DRS4的采样频率、采样深度、读出数据等。ADC模块主要由两个部分组成,一是通过SPI(Serial Peripheral Interface)给ADC的寄存器配置赋值来设置输出参考电压、数字输出编码、数字输出精度等等,二是数据解码,每次数据时钟的采样都需要严格控制在产生数据的时间窗内,才能保证数据解码成功。

-

信号发生器产生幅值为500 mV,频率从0~200 MHz的正弦波信号作为输入信号。测得AD8001AR和THS4508输出频谱图,如图10所示。模拟输入电路在输入正弦信号0~200 MHz时失真度误差小于0.7 dB,在输入正弦信号0~100 MHz时失真度误差小于0.2 dB。

-

在DRS4校准完成后,使用0 V直流作为输入时得到的对应的输出值,结果如图11所示。将采集到的输出值求高斯分布,其所得到的μ作为平均值Mean,Mean为0.160 8 mV;其所得到的σ作为RMS,得到的RMS为0.480 7 mV。在校准完成后,用0 V直流作为激励得到的系统电子学噪声小于0.5 mV。

-

DRS4数据采集电路的输入信号由脉冲发生器产生频率为10 MHz,幅值从100 mV到1 V,步进为100 mV的正弦波,每个幅值采集5 000个波形。该测试中,根据统计记录的数据,推导出不同幅值的正弦输入信号对应的读出电子学输出的幅度的线性拟合函数。由式(2)计算电子学系统的非线性:

$$ {V_{{\text{nonlinearity}}}} = \mathop {{\text{Max}}}\limits_{100 < n < 1000} \big\{ {O_{{\text{tes}}{{\text{t}}_n}}} - {O_{{\text{fi}}{{\text{t}}_n}}}\big\} \text{,} $$ (2) 其中:

${V_{{\text{nonlinearity}}}}$ 为非线性电压值;${O_{{\text{tes}}{{\text{t}}_n}}}$ 是在n毫伏幅值的正弦输入对应的实际输出值;${O_{{\text{fi}}{{\text{t}}_n}}}$ 是对n毫伏幅值的正弦输入对应的输出信号的线性拟合的拟合值。如图12所示,不同幅值的输入得到的非线性,最大不超过1.9 mV。由式(3):$$ {I_{{\text{INL}}}} = \frac{{|{V_{{\text{out\_fit}}}} - {V_{{\text{out}}}}{|_{{\text{MAX}}}}}}{{{V_{{{{\rm{o}} - {\rm{MAX}}}}}}}} \text{,} $$ (3) 求得积分非线性 (Integral Non-Linearity, INL)为0.95%,其中

$ {I_{{\text{INL}}}} $ 为积分非线性,$ {V_{{\text{out\_fit}}}} $ 为拟合输出值,$ {V_{{\text{out}}}} $ 为与其对应的实际输出值,如图13所示。 -

使用DRS4数据采集电路与PSD进行了联合测试。测试方案框图如图14所示,PMT的供电电压为–950 V。宇宙射线击中塑料闪烁体后发出荧光,荧光被PMT探测器转化为电荷信号[13-14],DRS4数据采集电路将电荷脉冲信号波形数字化,最后将处理完的数据发送给上位机。DRS4的采样频率

$ {f_{\text{s}}} $ 、采样深度${S_{\text{N}}}$ 、对输入信号的采样时长${T_{\text{s}}}$ 这三个的关系如式(4)所示。在测量PMT输出波形时,将DRS4芯片的采样深度${S_{\text{N}}}$ 设置成1 024个,在采样频率$ {f_{\text{s}}} $ 分别设置为2.048,3.072 ,4.920 GHz时,得到的数据所绘制的三条PMT输出信号波形,如图15所示。在DRS4的读出频率和ADC的转换速率一致时,DRS4的采样频率越高,相等时间长度输入信号对应的采样点数越多,即${S_{\rm{ N}(4.920~{\rm{GHz}})}} > {S_{\rm{ N}(3.125~{\rm{GHz}})}} > {S_{\rm{ N}(1.024~{\rm{GHz}})}}$ 。$$ {T_{\rm{s}}} = {S _{\rm{N}}}/{f_{\rm{s}}} $$ (4) -

本文基于SCA波形数字化技术设计了一款基于DRS4芯片的高速采样数据采集电路,用于物理实验装置中探测器输出信号的采样和处理。该电路主要由模拟提取电路、DRS4电路、ADC电路、FPGA、DAC电路、触发电路和接口电路等组成。在本次电路设计中,输入信号的采样以DRS4芯片为核心,数据处理以FPGA为核心,对电荷窄脉冲信号进行波形数字化处理。测试结果表明,该电路的模拟宽带在0~200 MHz时失真度误差小于0.7 dB,在0~100 MHz失真度误差小于0.2 dB,采样率高达5 GHz,最大非线性度不超过1.9 mV。在校准后,0 V直流作为输入,通道的电子学噪声小于0.5 mV,积分非线性优于1%。并且与PSD进行了联合测试,可以满足物理实验装置中探测器多参数测量的需求。

-

摘要: 基于开关电容矩阵(Switched Capacitor Array, SCA)的波形数字化技术是未来物理实验装置前端读出电子学的重要发展方向之一。本工作设计了一种基于SCA芯片DRS4(Domino Ring Sampler 4)的超高速波形数字化数据采集电路。DRS4单通道可以最高以5 GHz的采样率对探测器输出信号进行全波形采样。该电路主要由模拟调理电路、DRS4电路、ADC(Analog-to-Digital Converter)电路、FPGA(Field-Programmable Gate Array)、DAC(Digital-to-Analog Converter)电路、触发电路和接口电路等组成。性能测试表明,该电路通道的噪声小于0.5 mV,积分非线性 (Integral Non-Linearity, INL) 优于1%。本电路模拟输入带宽高,采样率700 MHz~5 GHz可调,具有良好的非线性。该数据采集电路具有一定的通用性,适用于多种类型的物理实验装置中的探测器读出。Abstract: Waveform digitization technology based on Switched Capacitor Array(SCA) is one of the important development fields of front-end readout electronics for future physical experiment facilities. In this paper, an ultra-high-speed waveform digital data acquisition circuit based on SCA chip DRS4(Domino Ring Sampler 4) is designed. A single channel of the DRS4 can sample the full waveform of the detector output signal at a sampling rate of up to 5 GHz. The circuit is mainly composed of analog conditioning circuit, a DRS4 circuit, ADC(Analog-to-Digital Converter) circuit, FPGA(Field-Programmable Gate Array), DAC (Digital-to-Analog Converter) circuit, a trigger circuit, an interface circuit, etc. Performance tests show that the circuit's noise is less than 0.5 mV, and the Integral Non-Linearity (INL) is better than 1%. In addition, the analog input bandwidth of this circuit is very high, the sampling rate is adjustable from 700 MHz to 5 GHz, and it has good nonlinearity. Therefore, the data acquisition circuit is versatile and suitable for detector readout in various physical experiment facilities.

-

Key words:

- Switched Capacitor Array /

- DRS4 /

- waveform sampling /

- performance testing

-

[1] STEELE J, BROWN J A, BRUBAKER E, et al. Journal of Instrumentation, 2019, 14(2): 02031. doi: 10.1088/1748-0221/14/02/P02031 [2] LIU J, ZHAO L, YAN L, et al. Nucl Instr and Meth A, 2019, 925: 53. doi: 10.1016/j.nima.2019.01.084 [3] HIEN D S, SENZAKI T. Nucl Instr and Meth A, 2001, 457(1): 356. doi: 10.1016/S0168-9002(00)00752-X [4] KITAMURA T, ISLAM M, HISAKADO T, et al. IEICE TRANSACTIONS on Fundamentals of Electronics, Communications and Computer Sciences, 2022, 105(11): 1450. doi: 10.1587/transfun.2021KEP0007 [5] WANG J, ZHAO L, FENG C, et al. IEEE Transactions on Nuclear Science, 2012, 59(5): 2435. doi: 10.1109/TNS.2012.2208656 [6] ZHOU Y, SUN Z Y, YU Y H, et al. Nuclear Science and Techniques, 2016, 27(3): 1. doi: 10.1007/s41365-016-0072-z [7] BOGDAN M, HUAN H, WAKELY S. Nucl Instr and Meth A, 2013, 718: 192. doi: 10.1016/j.nima.2012.08.087 [8] RITT S, DINAPOLI R, HARTMANN U. Nucl Instr and Meth A, 2010, 623(1): 486. doi: 10.1016/j.nima.2010.03.045 [9] ANDRÉS E, ASKEBJER P, BARWICK S W, et al. Nuclear Physics B-Proceedings Supplements, 1999, 70(1-3): 448. doi: 10.1016/S0920-5632(98)00468-X [10] VINCENZO F. Nuclear Physics B, 2013, 239-240: 176. doi: 10.1016/j.nuclphysbps.2013.05.028 [11] Paul Scherrer Institute, 9 Channel, 5 GSPS, Switched Capacitor Array, Paul Scherrer Institute [EB/OL]. [2022-08-21]. https://www.psi.ch/sites/default/files/2020-08/DRS4_rev09_2.pdf. [12] Analog Devices, 800 MHz, 50 mW Current Feedback Amplifier, AD8001, Analog Devices [EB/OL]. [2022-08-21]. https://www.analog.com/media/en/technical-documentation/datasheets/AD8001.pdf. [13] CATTANEO P, PULLIA M, PRATA M, et al. Journal of Instrumentation, 2020, 15(7): C07027. doi: 10.1088/1748-0221/15/07/C07027 [14] DONG T, ZHANG Y, MA P, et al. Astroparticle Physics, 2019, 105: 31. doi: 10.1016/j.astropartphys.2018.10.001 -

下载:

下载:

甘公网安备 62010202000723号

甘公网安备 62010202000723号