-

在核与粒子物理实验中高精度时间测量尤为重要[1-3]。传统的时间测量方式是甄别器结合时间数字变换器(Time-to-Digital Converter, TDC),该技术方案在目前稳定运行的大型核与粒子物理实验中最高能实现约20 ps精度的时间精度,例如STAR和BESIII中的TOF系统[4-5]。然而随着物理实验的发展,读出电子学时间测量的精度要求也在不断提高。而基于波形数字化技术的时间测量方案被证明可实现更好的精度[6-9],近年来基于该方案的时间测量电子学精度已达到10 ps水平[6]。传统的波形数字化方法是基于高速模拟数字变换器(Analog-to-Digital Converter, ADC)采样,但随着大规模核与粒子物理实验中通道数的增加,高速ADC由于功耗、成本以及集成度等方面的限制难以用于通道数众多的核与粒子物理实验中。作为一种替代方案,开关电容阵列(Switched Capacitor Array, SCA)先将采样到的电压值存储于电容阵列中,再用相对低速的ADC量化,能够实现低功耗和高集成度。随着SCA采样率的不断提升,基于SCA的波形数字化方案受到广泛的研究和应用[10-11]。

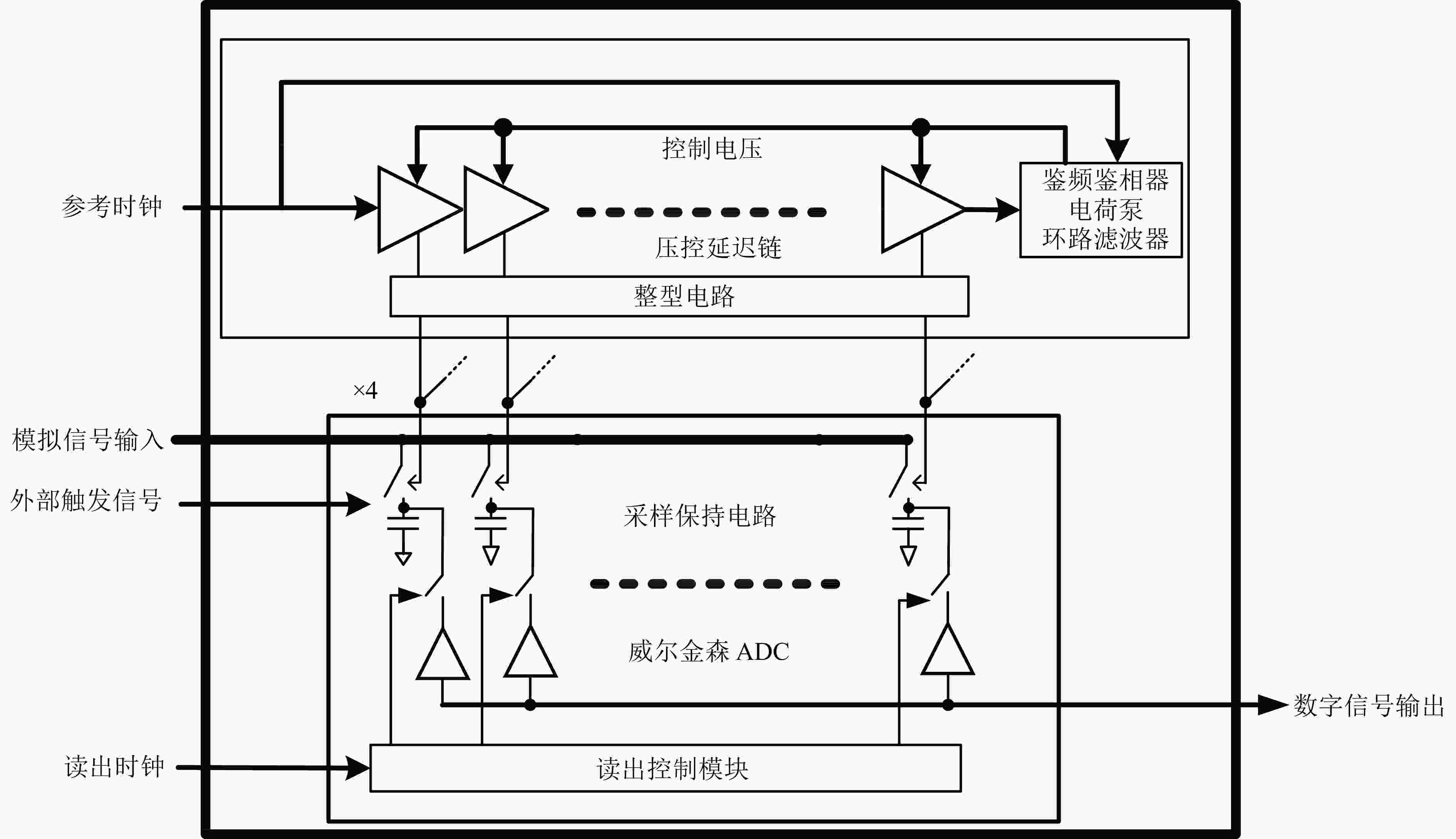

中国科学技术大学核探测与核电子学国家重点实验室设计了一款SCA专用集成电路(Application Specific Integrated Circuit, ASIC),该芯片的结构如图1所示。SCA采样率为1~5 Gsps,采样深度为128,模拟带宽约为400 MHz。该芯片共有4个通道,每个通道有128个采样保持电路和128个Wilkinson ADC。SCA所有通道共用一个时钟产生电路,时钟产生电路生成128路时钟信号控制采样保持电路的开关。当外部触发信号输入时,采样电容上的电压值并行地被威尔金森 (Wilkinson) ADC数字化。该芯片数据位宽为12 bits,串行数据读出速率最高200 MHz。本设计使用4片SCA ASIC,搭建16通道采样率5 Gsps的时间测量电子学系统。

-

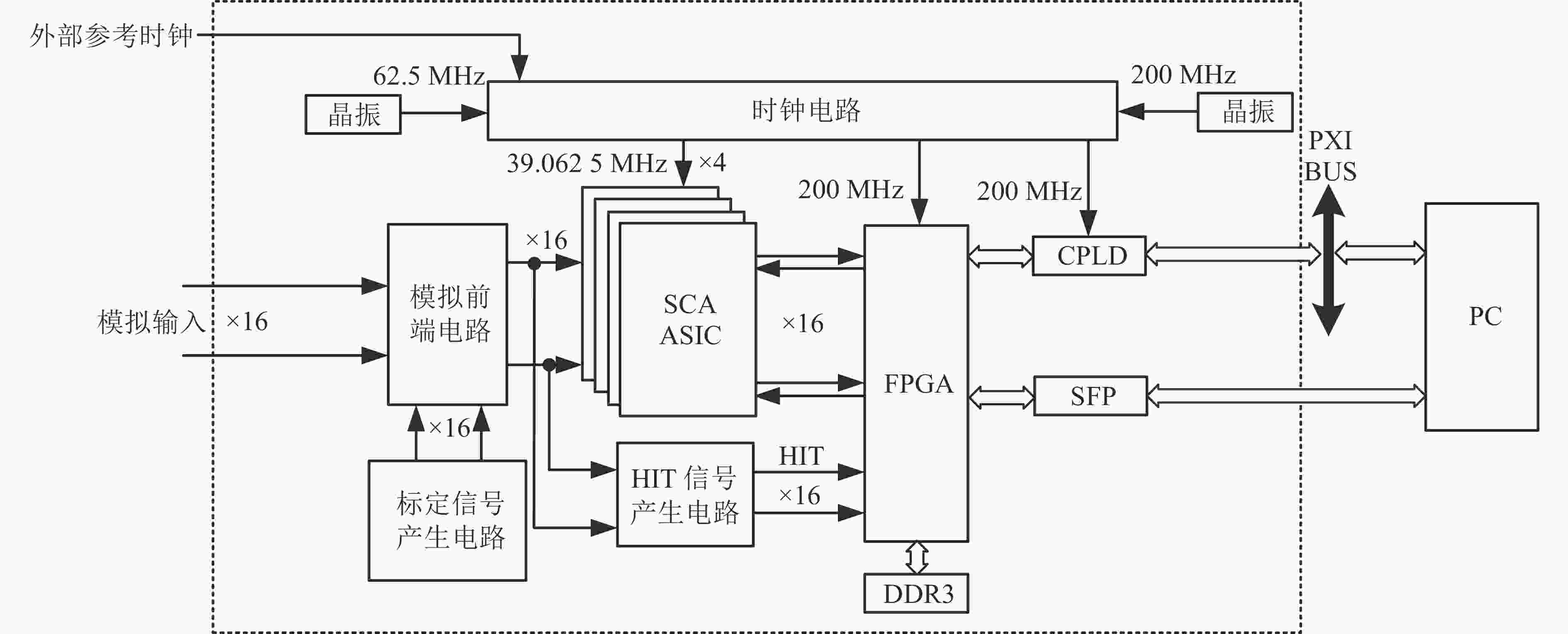

时间测量电子学系统主要由以下部分组成:模拟前端电路、标定信号产生电路、数字信号处理电路、时钟电路和电源电路。

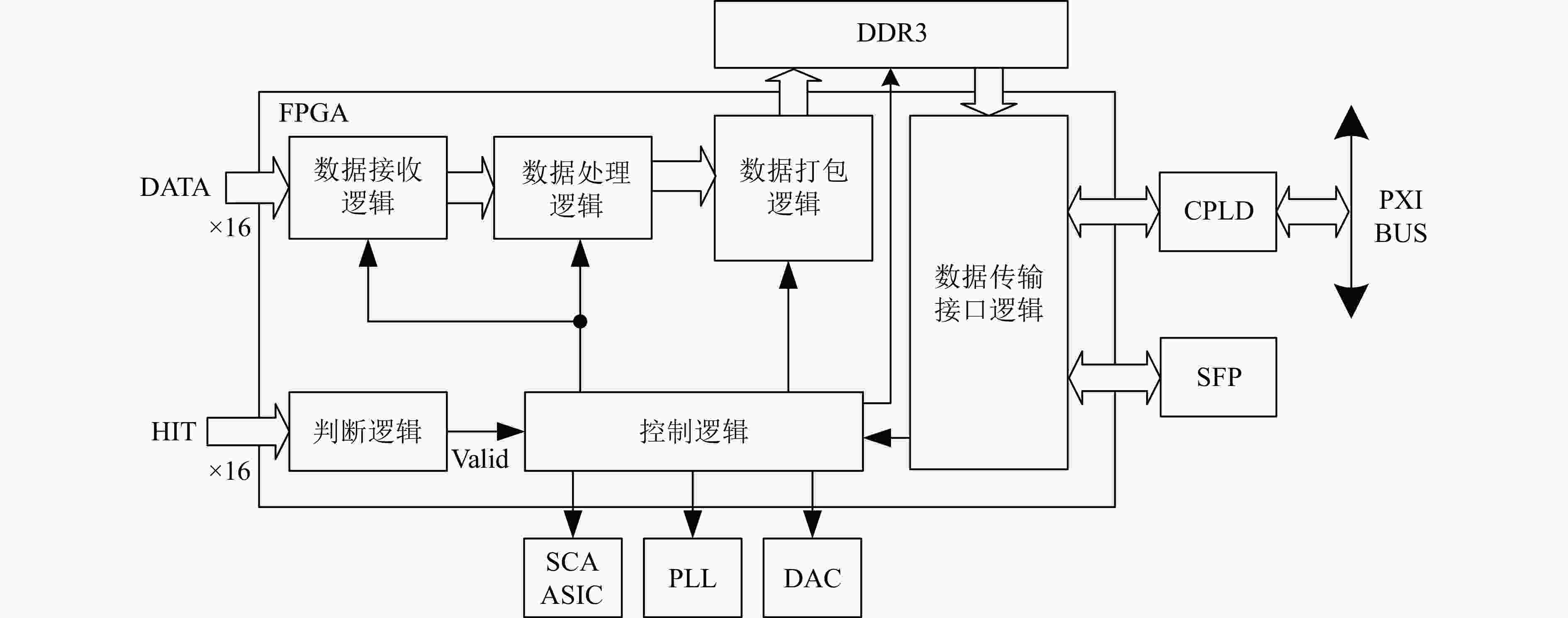

该系统基于PXI(PCI eXtensions for Instrumentation)6U设计,以保证稳定性和灵活性。输入先通过模拟前端电路进行阻抗匹配以及增大驱动能力,再进入SCA进行采样,同时输入模拟前端电路中的甄别器,每通道有一个甄别器,一旦输入超过设定的甄别器阈值就会输出一个hit信号到现场可编程逻辑阵列(Field Programmable Gate Array, FPGA)。在FPGA中hit信号进入判断逻辑,如果满足判断条件后会产生有效信号到控制逻辑,控制逻辑随即产生控制信号,使得SCA停止采样并进行数字化。数字化后的信号传入FPGA中进行处理,处理后的数据通过PXI或SFP传入PC。系统整体结构如图2所示。

-

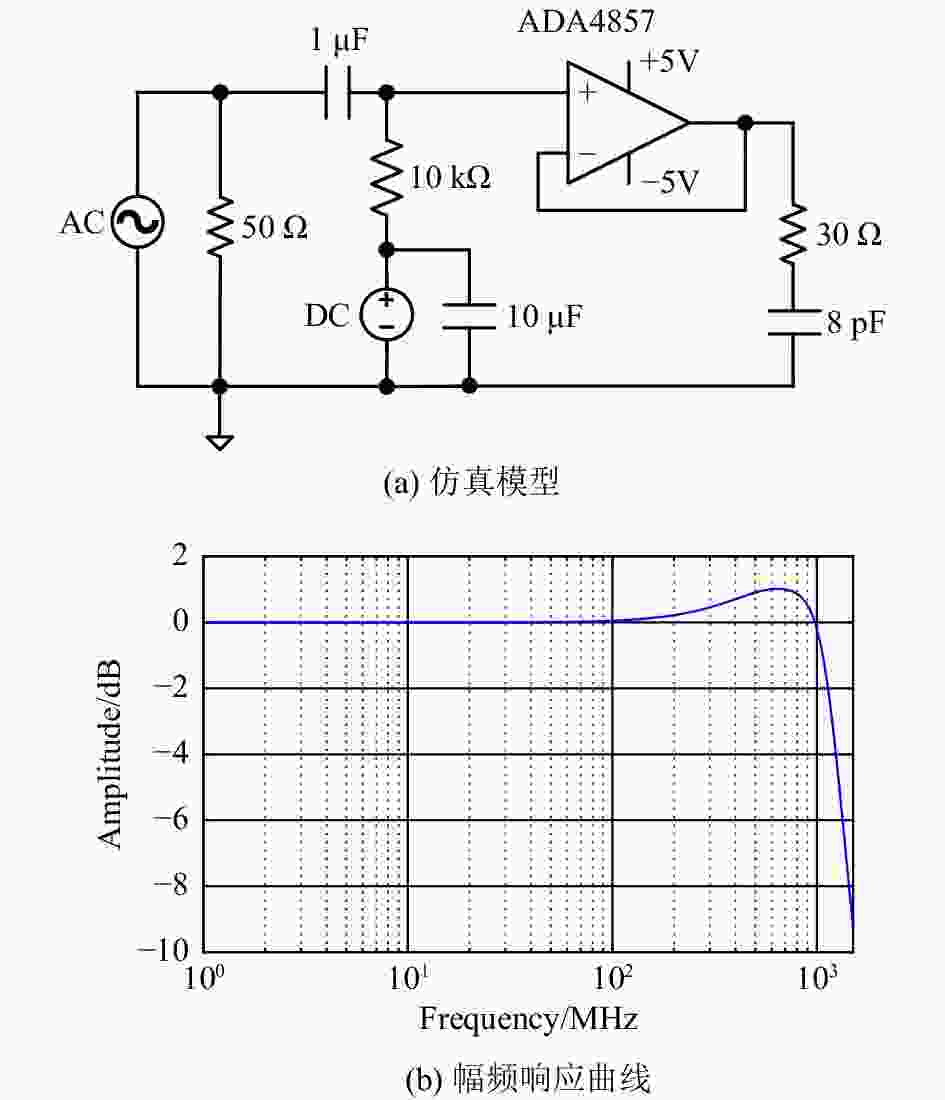

模拟前端电路如图3所示,主要包含驱动电路和hit信号产生电路。由于SCA内部没有输入驱动电路,所以输入信号需要外部驱动电路,以增大驱动能力并做阻抗匹配。SCA输入模拟带宽约为400 MHz,为了保证输入信号在输入模拟带宽范围内不失真,需要在该范围内有平坦的幅频响应曲线。SCA的输入为8 pF的容性负载,为了抑制时域波形的过冲需要在运放的输出端串联电阻,最终选择商用运放芯片ADA4857。pspice仿真模型如图4(a)所示,仿真结果如图4(b)所示,输出端串联30 Ω电阻时,在0~400 MHz的频率范围内幅频响应曲线较平坦。

为了产生SCA工作时需要的外部触发信号,使得SCA停止采样进入量化读出模式,设计了hit信号产生电路。如图3所示,在每个通道的模拟前端电路后面有一个甄别器,甄别器输出到FPGA。考虑到在实际应用场景下,输入信号脉宽可能较窄,需要能完成小宽度甄别的高速甄别器。最终选用LTC6754进行甄别,该芯片能完成小于1 ns宽度的甄别,并且传输延迟为1.8 ns,实时性较好,最后通过FPGA辅助完成SCA的触发。

-

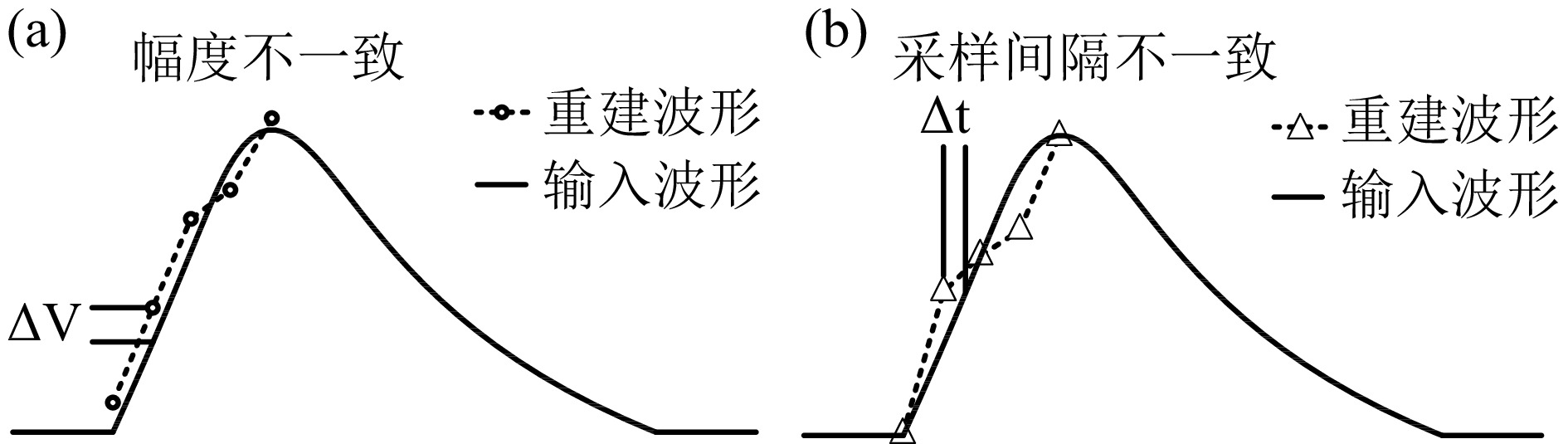

由于工艺偏差的存在,SCA ASIC各采样单元的幅度和采样间隔不可避免地会存在不一致性,如图5所示。该不一致性使得重建波形与输入波形差异很大,从而严重影响时间测量的精度[12],因此必须对其进行标定。

其中,幅度标定过程如下:输入已知电压的直流电平,SCA进行多次采样和量化,计算各采样单元多次量化的均值,改变直流电平电压,重复上述步骤。最后建立直流电平电压与量化值的查找表,即完成了幅度标定。采样间隔标定方法较多[12-15],本文使用基于超定线性方程组的全局时钟标定法,其原理如图6所示,通过测量已知频率的正弦波的周期,进而通过测量得到的周期反过来计算采样间隔。

该时间测量电子学系统上集成了直流标定和交流标定电路,不需要信号源即可对SCA ASIC的不一致性进行标定。如图3所示,由于模拟前端电路对输入信号进行了交流耦合处理,需要用数字模拟转换器(Digital-to-Analog Converter, DAC)提供输入信号经交流耦合后的直流偏置电压,该偏置电压在外部无信号输入的情况下可以作为直流标定电压。综合考虑选择高精度DAC芯片LTC2600产生参考电平,提供直流偏置电压以及直流标定电压。交流标定信号产生电路如图7所示,本设计利用SiT9121、AD9522-3结合低通滤波产生和SCA采样时钟不同源的交流标定信号。在模拟前端电路中通过开关ADG904选择交流标定信号输入,并通过基于超定线性方程组的全局时间标定法进行标定。

-

SCA采样时钟的不确定性会导致采样波形的不确定性,通常称为孔径偏差(Aperture Uncertainty),孔径偏差会恶化信噪比,假设时钟的抖动(jitter)为高斯分布,理论上由时钟抖动限制的信噪比为

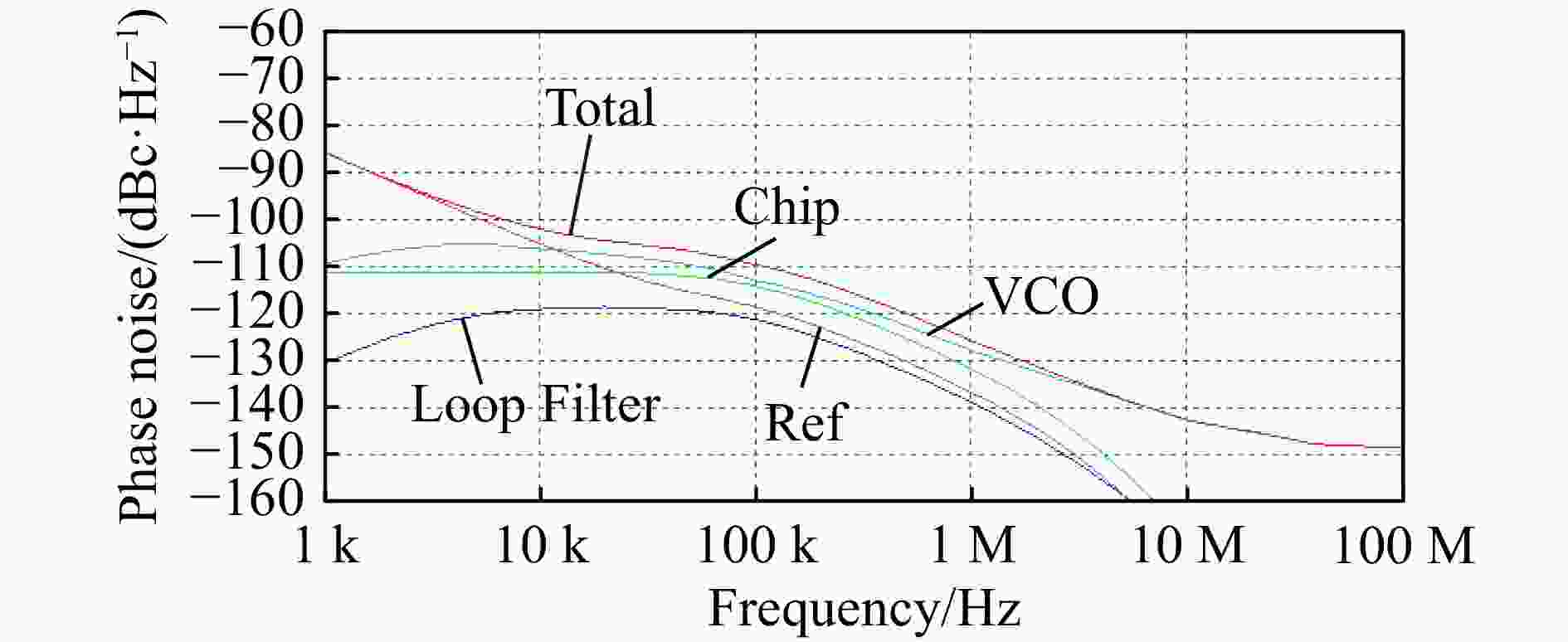

$$ SN{R_{{\rm{jitter}}}} = - 20\log (2\pi {f_{{\rm{in}}}}{\sigma _{{\rm{jitter}}}}) , $$ (1) 其中:fin为输入信号频率;σjitter为孔径偏差。SCA ASIC量化的信噪比约为50 dB(主要是热噪声),为避免信噪比恶化严重,由时钟抖动限制的信噪比需要大于SCA ASIC量化的信噪比,即大于50 dB。若要满足fin=400 MHz的需求,由式(1)可计算得到需要将σjitter控制在1.26 ps RMS(Root Mean Square)以内,RMS为均方根值,是衡量随机变量大小的一种方式。

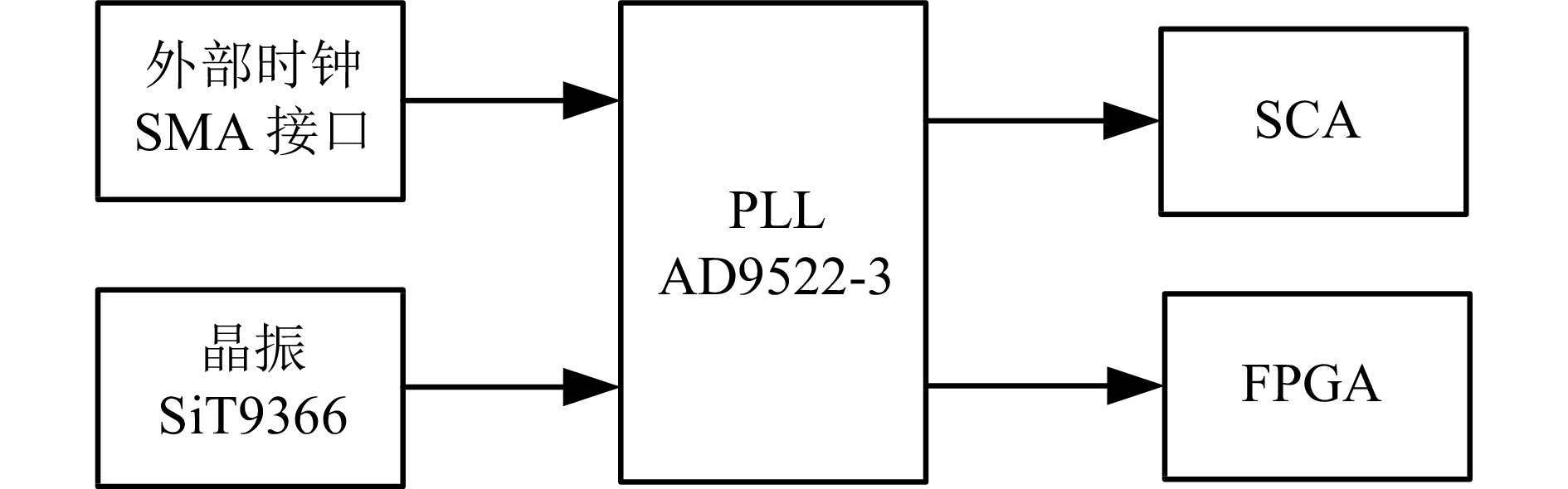

时钟电路如图8所示,主要由晶振SiT9366和锁相环(Phase Locked Loop, PLL)芯片AD9522-3组成,同时,为满足实际应用场景中接收外部同源时钟的需求,还设计了外部时钟输入接口。晶振和PLL的仿真结果如图9所示,从0.1 kHz到20 MHz的相位噪声积分为369 fs RMS,好于1.26 ps RMS的指标要求。

-

数字信号处理电路的主要功能为接收SCA的数据并实时地进行处理、对各芯片进行配置和传输数据。数字信号处理电路的结构如图10所示,包括FPGA、CPLD、SFP和DDR3,其中的核心为FPGA,根据资源量(如IO管脚个数、RAM容量等)以及速度等级等需求,选用了Xilinx公司Kintex-7系列的FPGA芯片XC7K325T。

由于FPGA内的RAM资源有限,当事例率较高时,为避免数据丢失,需要设计外部数据缓冲电路。为了完成上述功能,选用Micron公司的MT41K512M8型号的DDR3L SDRAM,其宽度为8 bits,容量为4 Gb,数据传输速率可达到1 600 MT/s,可满足16通道并行采样读出的需求。

FPGA处理后的信号可通过SFP接口传入PC,同时也可通过PXI总线进行数据传输。SFP接口数据传输是基于TCP/IP协议在FPGA中实现的简化千兆以太网通信。PXI总线数据传输则使用Altera公司的CPLD芯片EPM2210作为PXI接口芯片,辅助FPGA进行通信。

-

由3.4节可知,FPGA作为数字信号处理电路的核心,需要对各芯片进行配置,并且实时完成数据接收、修正、时间内插和数字甄别提取出时间信息,最后还要配合DDR3和CPLD进行数据的储存与传输,因此需要进行相应的逻辑设计。FPGA逻辑如图11所示,主要包含数据接收逻辑、数据处理逻辑和数据传输接口逻辑。

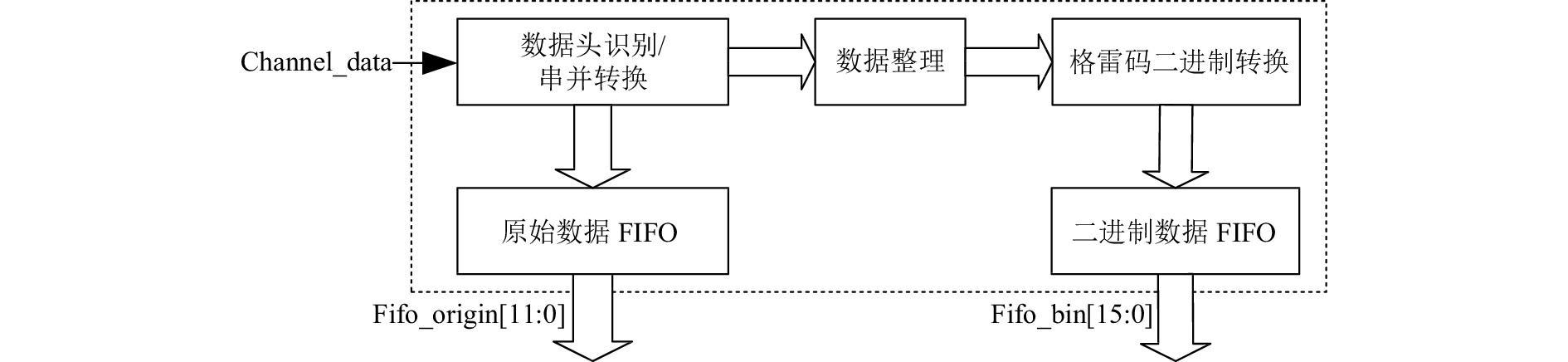

在电子学上电后,FPGA的控制逻辑对SCA ASIC、DAC和PLL进行配置。配置完成后判断逻辑接收来自模拟前端电路的hit信号并进行相应的逻辑判断,判断结果若有效则控制逻辑输出控制信号停止SCA ASIC的采样并进入量化读出模式。SCA ASIC量化读出的数据进入数据接收逻辑,数据接收逻辑包括数据头的识别、串并转换和格雷码转换为二进制码等功能,即数据的初步处理。经过数据接收逻辑初步处理后的数据进入数据处理逻辑,数据处理逻辑对SCA ASIC的数据进行实时的幅度和时间修正,并对处理后的数据进行时间提取,减少需要传输的数据量。数据经过打包后缓存到DDR3中,最终通过CPLD及PXI传输到上位机。

-

SCA ASIC输出频率可调的串行数据和时钟,最高支持200 MHz。SCA ASIC输出格式如表1所示,以12位为一组,共131组,包括时钟上升沿粗计数、时钟下降沿粗计数、SCA停止位和128个采样单元的量化结果。前三组数据的头是固定数据,其中第一组前两位为10,可通过该两位码值识别数据头。

表 1 SCA输出数据格式

内容 格式 时钟上升沿粗计数 “10”+10 bits粗计数 时钟下降沿粗计数 “10”+10 bits粗计数 SCA停止位 “10101”+7 bits停止位 SCA量化结果 12 bits量化结果 …… …… SCA量化结果 12 bits量化结果 数据接收逻辑需要对SCA ASIC输出的高速串行数据进行数据头的寻找、串并转换和格雷码转换为二进制码等操作。数据接收逻辑如图12所示,当hit信号来临,控制逻辑停止SCA ASIC的采样并进入量化读出时,控制逻辑会输出控制信号到数据接收逻辑,数据接收逻辑随即进入数据接收状态,将数据读入环形寄存器中。当识别到数据头时,把该组数据读入12位的环形寄存器,并将环形寄存器的值写入FIFO(First In First Out),共需读入131组,由此完成识别数据头和串并转换的功能。SCA内部ADC的输出为格雷码,为了方便之后的数据处理,需要将格雷码转换为二进制码,并根据SCA输出的特征码进行判断该次触发的数据是否有误。最后将数据由12位补充至16位,前四位增加通道标识、数据段标识和错误标识。

-

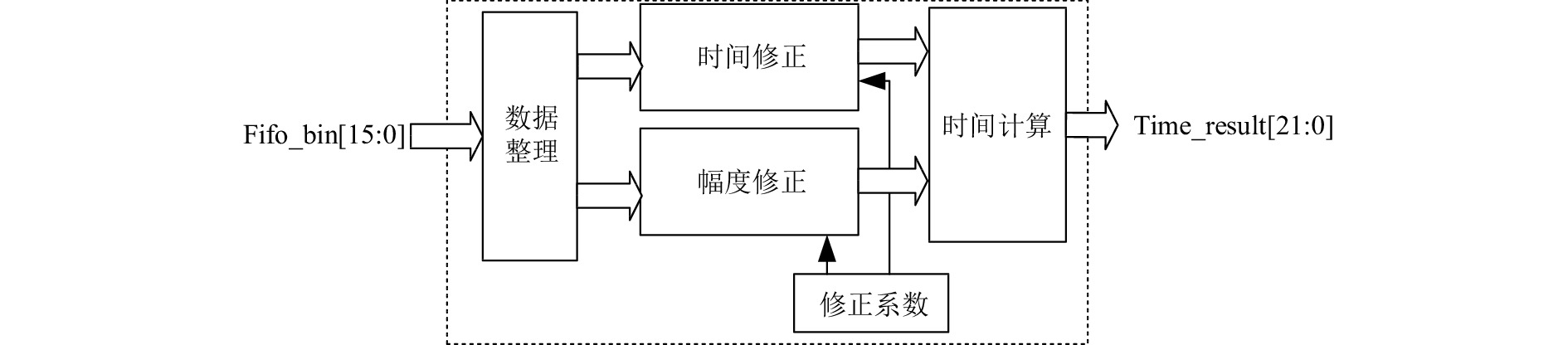

数据处理逻辑主要包括修正和时间提取,如图13所示。修正包括幅度修正和时间修正,在修正之前需要先进行相应的标定。通过标定计算得到相应的修正系数,利用该修正系数在FPGA中实现实时修正的功能,修正需要用到环形RAM和乘加运算器进行简单的运算。修正之后则进入时间提取环节,时间提取使用线性插值结合前沿定时甄别的方法,即通过公式

$$ t = \frac{{({t_1} - {t_2})({V_1} - {V_{{\rm{th}}}})}}{{{V_2} - {V_1}}} + {t_1} , $$ (2) 其中:t1和t2是过阈点附近的两个采样点的时间;V1和V2是该两点的幅度,由上式可知时间提取需要用到乘法器和除法器。

数据处理逻辑后将处理后的数据进行打包,一次事例波形数据打包格式如表2所列。

表 2 一次事例波形数据帧格式

内容 格式 时钟上升沿粗计数 “000010”+10 bits粗计数 时钟下降沿粗计数 “000010”+10 bits粗计数 SCA停止位 “001010101”+7 bits停止位 SCA量化结果 “0010”+12 bits量化结果 …… …… SCA量化结果 “0010”+12 bits量化结果 时间计算结果 “10101”+11 bits时间计算结果 时间计算结果 “10101”+11 bits时间计算结果 数据尾 “11111111”+4 bits通道号+4 bits通道号 -

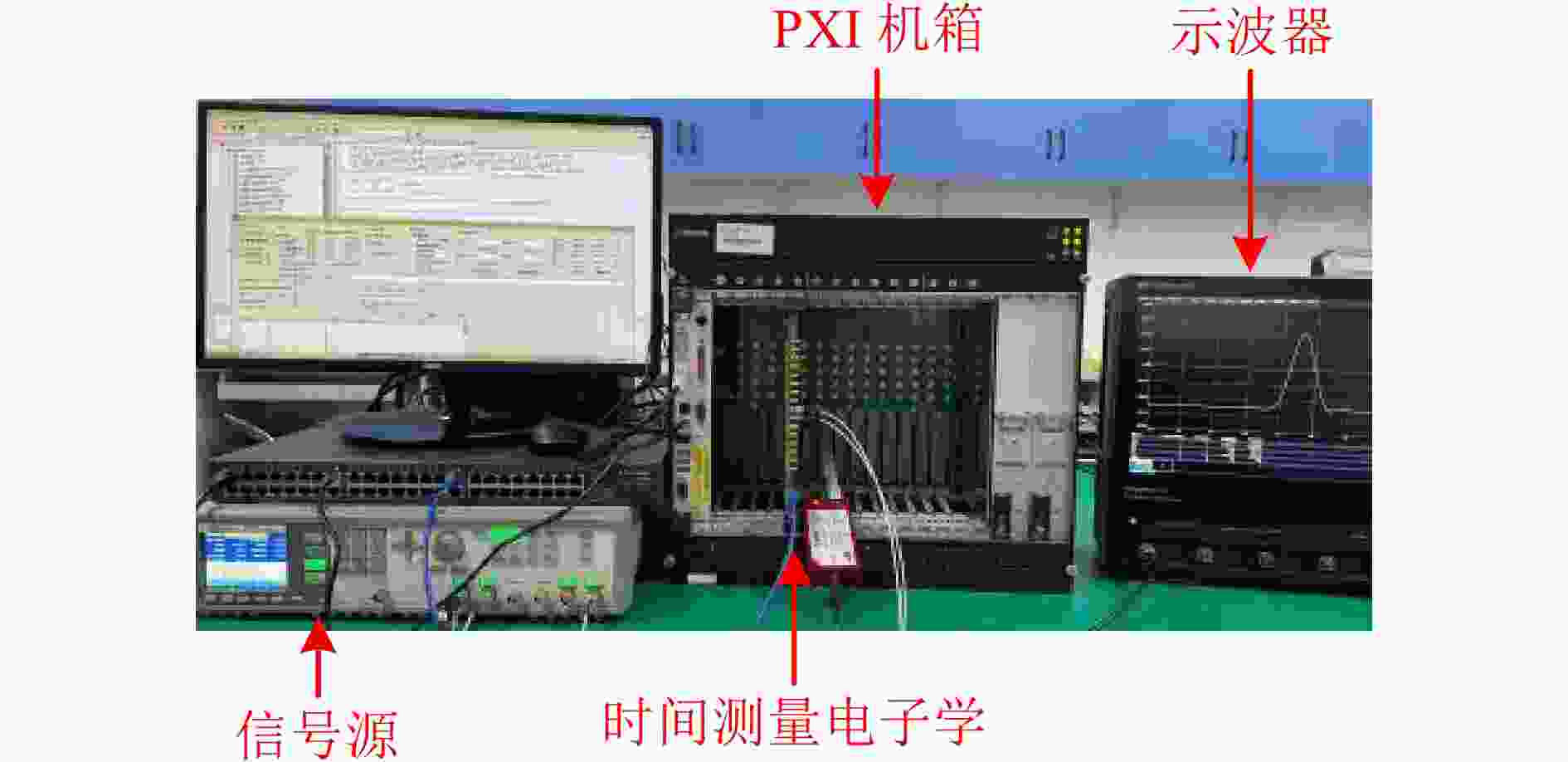

测试平台如图14所示,供电和数据传输通过PXI机箱实现。测试所用高质量正弦波信号由射频信号发生器ROHDE&SCHWARZ SMA100B产生,脉冲信号由安捷伦脉冲函数任意波形发生器Keysight 81160A产生,时间测量电子学输出的数据通过PXI总线传入上位机。

-

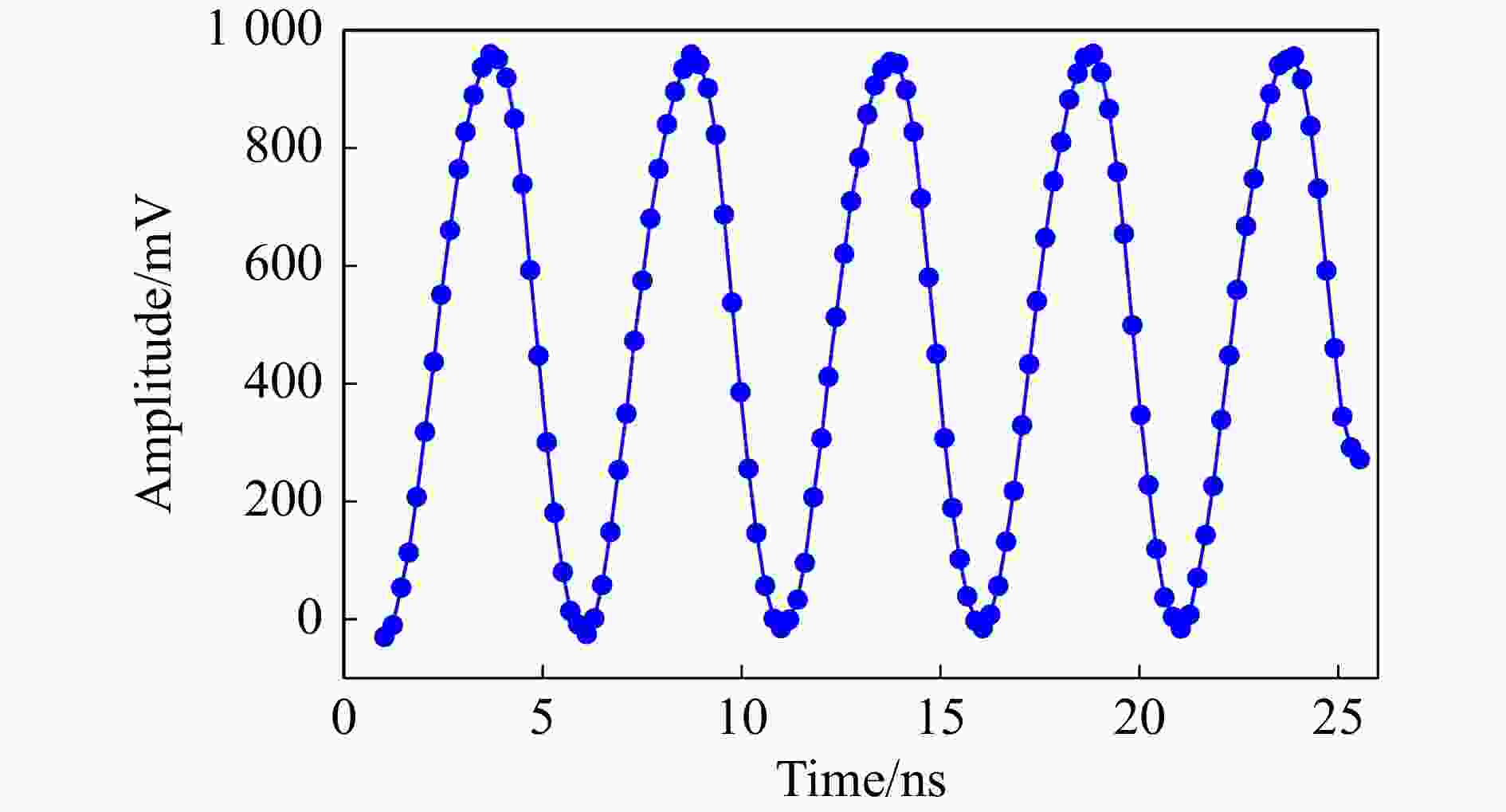

由SMA100B产生高精度正弦波至时间测量电子学,输出频率为200 MHz,峰峰值为900 mV,经过交流耦合后输入至SCA ASIC。测试时使用标定得到的码值电压查找表和采样间隔进行相应的修正后,得到的采样波形如图15所示。

用Keysight 81160A产生高斯信号波形,基线电压为100 mV,峰值为900 mV,经过相应的修正后得到的采样波形如图16所示。

-

时间测量电子学的模拟带宽对时间精度有非常大的影响[12],因此需要测试该系统的输入模拟带宽。使用SMA100B产生幅度相等频率不同的正弦波信号,测试频率为10 到500 MHz之间20个频率点,计算得到时间测量电子学的幅频响应曲线,如图17所示。时间测量电子学的−3 dB带宽约为420 MHz,满足设计需求。

-

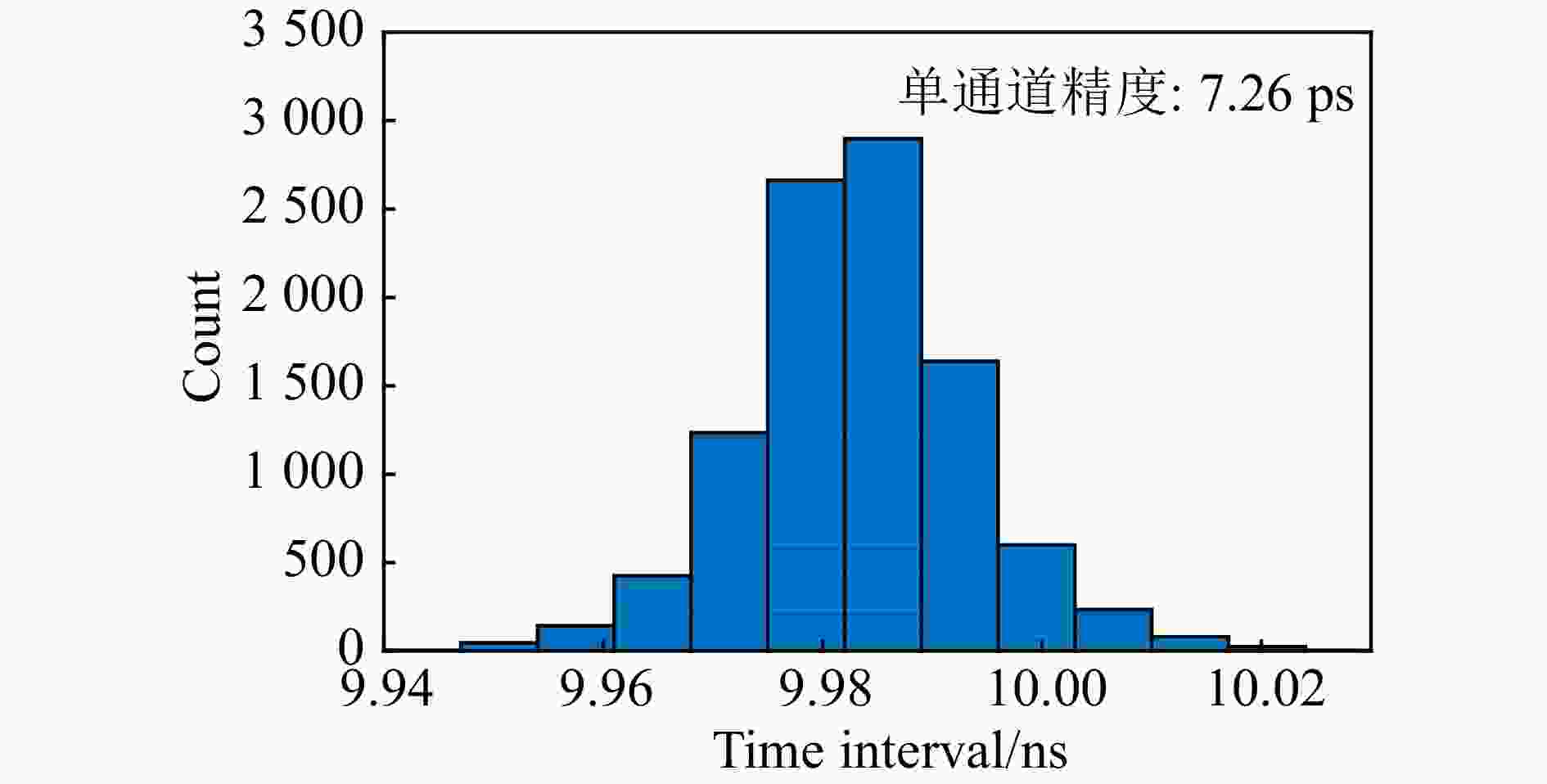

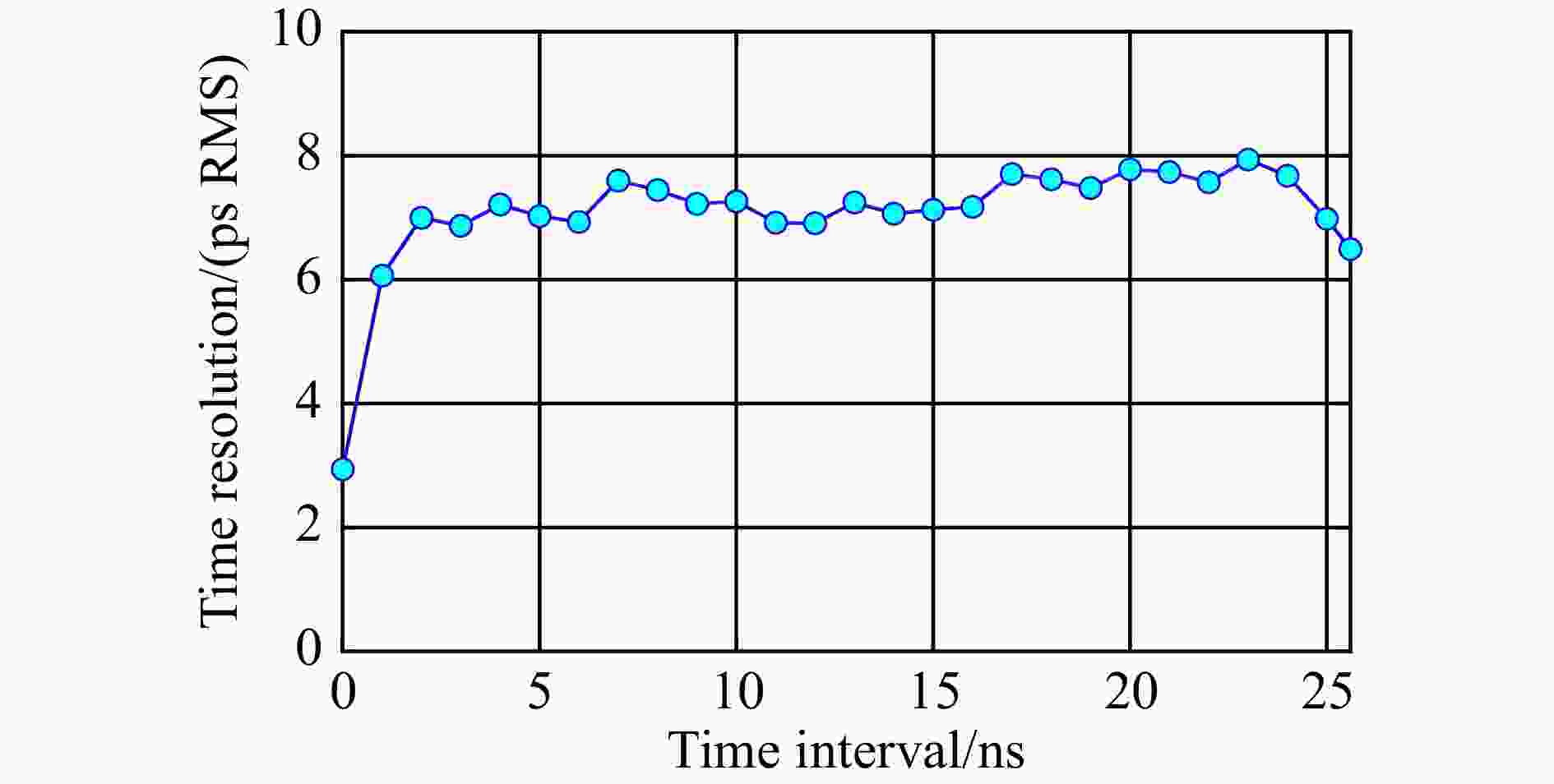

由信号源81160A产生两路固定时间间隔的脉冲波形输出至时间测量电子学,计算两通道间的时间间隔,统计时间间隔的分布,并计算该时间间隔的标准差,该标准差除以根号2即得到单通道的时间精度(假设两通道时间测量结果为独立的高斯分布)。可以得到不同时间间隔下的时间精度。进行相应的修正后,测量0到25 ns短时间间隔脉冲的时间精度。10 ns固定时间间隔脉冲的时间间隔结果分布如图18所示。各时间间隔的精度如图19所示,短时间间隔下的时间精度小于9 ps RMS。

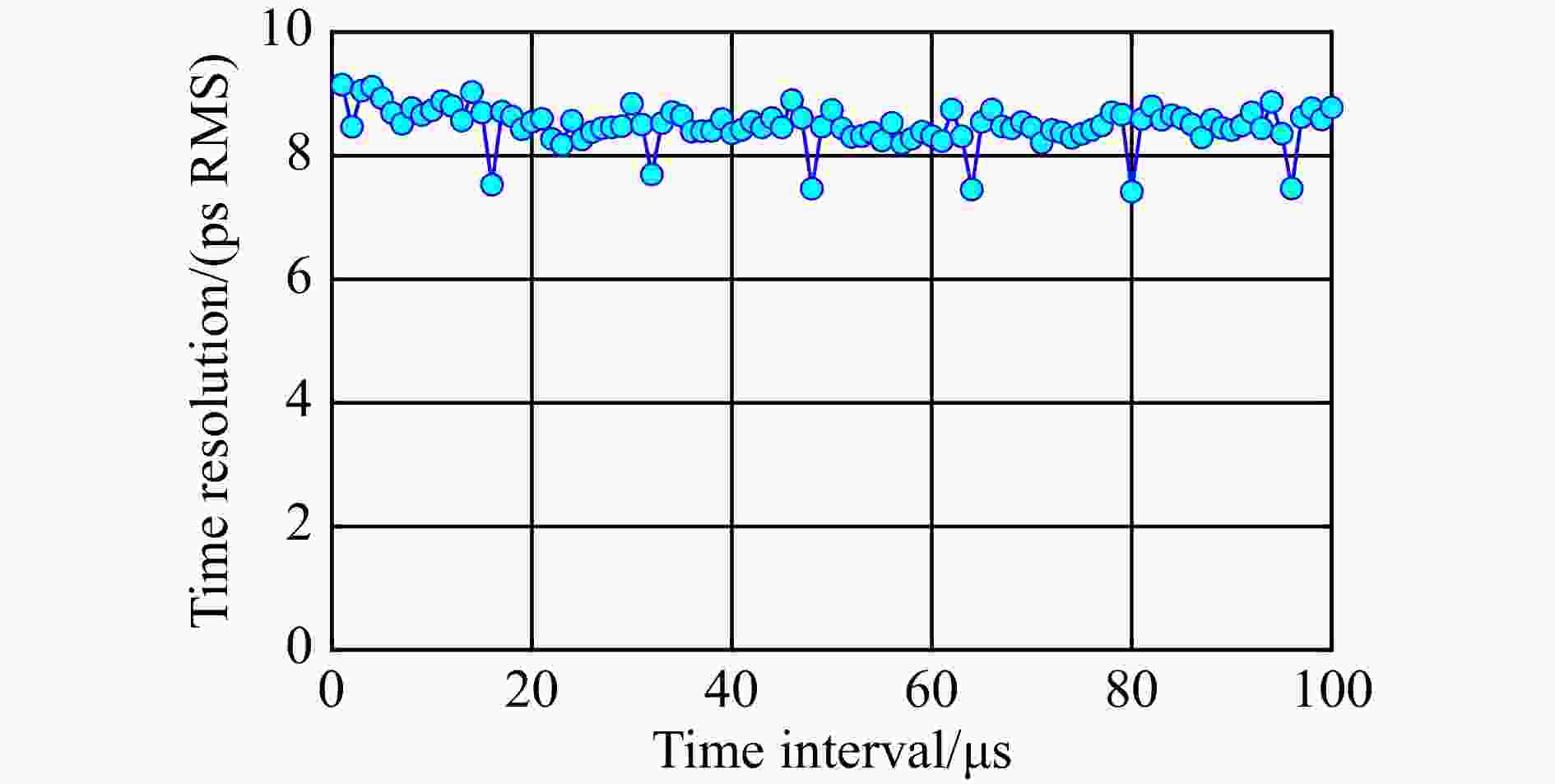

在某些应用场合下,需要测量大间隔下的时间精度,测量到的小于100 μs时间间隔的时间精度如图20所示,小于10 ps RMS。

-

在本论文工作中,完成了基于SCA采样的时间测量电子学原型设计,可实现16通道5 Gsps高速采样,并实时地进行数字信号处理以提取时间信息。SCA输出数据的处理在FPGA中完成,包括幅度和采样间隔的不一致性修正、线性插值和数字甄别等。对该时间测量电子学进行了瞬态波形测试、带宽测试和时间精度测试,测试结果表明各项结果符合预期,时间精度好于10 ps RMS。

-

摘要: 基于高速波形数字化实现高精度时间测量是核与粒子物理实验读出电子学中的研究热点。本工作针对高精度时间测量的需求基于实验室自主研发的开关电容阵列(Switched Capacitor Array, SCA)专用集成电路(Application Specific Integrated Circuit,ASIC)开展16通道集成的时间测量电子学原型的设计,输入信号经过SCA采样和量化后传输至现场可编程逻辑阵列(Field Programmable Gate Array, FPGA),在FPGA中进行误差修正、时间内插和数字甄别提取出时间信息。目前已在实验室环境下完成此电子学的时间精度测试,测试结果表明,此电子学可以实现好于10 ps RMS(Root Mean Square)的时间精度。Abstract: Precise time measurement based on high-speed waveform digitalization is a research hotspot in nuclear and particle physics experiment readout electronics. In this paper, a prototype of 16-channel time measurement electronics aiming for high-precision time measurement is designed, based on a Switched Capacitor Array(SCA) Application Specific Integrated Circuit(ASIC) designed by the laboratory where I am. After being sampled and digitized by the SCA ASIC, signals are directly transmitted to one Field Programmable Gate Array(FPGA), in which mismatch error correction, linear interpolation, and digital discrimination are integrated into it to extract the time information. The laboratory test results indicate that a time resolution of better than 10 ps RMS can be achieved in electronics.

-

Key words:

- time measurement /

- waveform digitization /

- switched capacitor array

-

表 1 SCA输出数据格式

内容 格式 时钟上升沿粗计数 “10”+10 bits粗计数 时钟下降沿粗计数 “10”+10 bits粗计数 SCA停止位 “10101”+7 bits停止位 SCA量化结果 12 bits量化结果 …… …… SCA量化结果 12 bits量化结果 表 2 一次事例波形数据帧格式

内容 格式 时钟上升沿粗计数 “000010”+10 bits粗计数 时钟下降沿粗计数 “000010”+10 bits粗计数 SCA停止位 “001010101”+7 bits停止位 SCA量化结果 “0010”+12 bits量化结果 …… …… SCA量化结果 “0010”+12 bits量化结果 时间计算结果 “10101”+11 bits时间计算结果 时间计算结果 “10101”+11 bits时间计算结果 数据尾 “11111111”+4 bits通道号+4 bits通道号 -

[1] FENG C, LIU S, AN Q. IEEE Transactions on Nuclear Science, 2010, 57(2): 463. doi: 10.1109/TNS.2009.2034658 [2] ERTLEY C, ANDERSON J, BYRUM K, et al. IEEE Transactions on Nuclear Science, 2009, 56(3): 1042. doi: 10.1109/TNS.2009.2016422 [3] PAUS C, GROZIS C, KEPHART R, et al. Nucl Instr and Meth A, 2001, 461: 579. doi: 10.1016/S0168-9002(00)01305-X [4] LLOPE W. STAR Collaboration. M Nucl Instr and Meth A, 2012, 661: 110. doi: 10.1016/j.nima.2010.07.086 [5] CAO P, SUN W, JI X, et al. Chinese Physics C, 2014, 38(4): 046101. doi: 10.1088/1674-1137/38/4/046101 [6] LIU J, ZHAO L, YAN L, et al. Nucl Instr and Meth A, 2019, 925: 53. doi: 10.1016/j.nima.2019.01.084 [7] GENAT J, VARNER G, TANG F, et al. Nucl Instr and Meth A, 2009, 607: 387. doi: 10.1016/j.nima.2009.05.193 [8] RONZHIN A, ALBROW M, LOS S, et al. Nucl Instr and Meth A, 2012, 668: 94. doi: 10.1016/j.nima.2011.11.083 [9] BRETON D, DELAGNES E, MAALMI J, et al. Nucl Instr and Meth A, 2011, 629: 123. doi: 10.1016/j.nima.2010.10.087 [10] RITT S, DINAPOLI R and HARTMANN U. Nucl Instr and Meth A, 2010, 623: 486. doi: 10.1016/j.nima.2010.03.045 [11] OBERLA E, GENAT J, GRABAS H, et al. Nucl Instr and Meth A, 2014, 735: 452. doi: 10.1016/j.nima.2013.09.042 [12] STRICKER-SHAVER D, RITT S, PICHLER B. IEEE Transactions on Nuclear Science, 2014, 61(6): 3607. doi: 10.1109/TNS.2014.2366071 [13] KIM H, CHEN C, ECLOV N, et al. Nucl Instr and Meth A, 2014, 767: 67. doi: 10.1016/j.nima.2014.08.025 [14] NISHIMURA K, ROMERO-WOLF A. Physics Pcocedia, 2012, 37: 1707. doi: 10.1016/j.phpro.2012.02.495 [15] CHENG B, ZHAO L, QIN J, et al. Nucl Instr and Meth A, 2019, 916: 71. doi: 10.1016/j.nima.2018.11.029 -

下载:

下载:

甘公网安备 62010202000723号

甘公网安备 62010202000723号