文章编号: 1007-4627(2009)04-0308-04

## HIRFL-CSR 前端总线控制器的改进设计\*

赵 龙<sup>1,2</sup>, 乔卫民<sup>1, #</sup>, 敬 岚<sup>1</sup>, 刘伍丰<sup>1,2</sup> (1中国科学院近代物理研究所, 甘肃 兰州 730000; 2中国科学院研究生院, 北京 100049)

摘 要:论述了用于兰州重离子加速器冷却存储环(HIRFL-CSR)控制系统的前端总线系统控制器的改进。改进了控制器的嵌入式操作系统和应用程序,开发了控制器和数据库交换数据的应用程序。该控制器基于BGA 封装的 ARM920T(ARM9)处理器和嵌入式的 LINUX 操作系统,可以连接标准的 VGA 显示器、键盘、鼠标,采用了现场可编程的 FPGA 器件进行背板接口设计,并具有 64 mA 高驱动能力的总线驱动器,以及拥有灵活的接口信号定义可编程能力,是 HIRFL-CSR 控制系统的关键部件。

关键词: ARM9; 总线控制器; 通用计算机外围接口; 嵌入式 LINUX

中图分类号: TL503.6 文献标识码: A

### 1 引言

兰州重离子加速器冷却储存环(Heavy Ion Research Facility in Lanzhou-Cooling Storage Ring, HIRFL-CSR)是兰州重离子研究装置(HIRFL)的 扩建工程,属于国家"九五"重大科学工程项目。它 的建设目的是将重离子的能量提高到 1 GeV/u 附 近,同时利用储存环电子冷却技术将束流品质提高 约一个量级,并提供多种类的重离子束,以开展更 广范围和更高精度的物理实验。随着计算机及其网 络技术的迅猛发展,世界上大多数加速器实验室的 控制系统都逐渐采用了称之为"标准模型"的体系结 构。在标准模型下,控制系统由3部分组成:通用 工作站、控制局域网和控制器。若干个控制器负责 管理各个控制子系统。通用工作站与控制器之间通 过控制局域网通信。局域网通常采用 FDDI 或以太 网,控制器通常采用高性能 VME 总线。近年来, 国内外建成或正在建设的加速器控制系统都采用了 分布式控制系统标准模型的结构。

美国物理学会(American Physical Society,简称 APS)加速器控制系统[1]采用"标准模型",工作站可以位于任何地方而且能够完成所有的控制功

能。前端计算机成为输入输出控制器,负责直接对 各分系统进行控制。网络采用 10, 100 Mb 或 1 Gb 的以太网,通信协议为 TCP/IP。日本 KEKB 加速 器控制系统[2] 也采用标准模型,其网络采用 FDDI 做主干网,以太网和 FDDI 主干网之间通过 FDDI-Ethernet 网桥互相连接。德国重离子研究中心(Gesellschaft fuer Schwerionenforschung, 简称 GSI) 的控制系统[3]采用的是一种分散的分布式系统。被 控设备通过现场总线(field bus)与 I/O 部件相连 接, I/O 部件通过以太网与工作站通信。北京正负 电子对撞机(Beijing Electron-Positron Collider, 简 称 BEPC)[4] 采用美国 SLAC New SPEAR[5] 控制系 统结构。其中,磁铁电源控制系统采用了标准模型 的分布式控制系统结构,前端控制计算机是基于 VME 总线的单板机。合肥同步辐射实验室(National Synchrotron Radiation Laboratory, 简称 NRSL)的控制系统[6]是一种基于 EPICS 的分布式 控制系统。该系统的前端控制器大多采用工业 PC 和欧姆龙系列的可编程控制器(PLC), IOC 与前端 控制器之间采用光电隔离的 RS422/232 作为现场

<sup>\*</sup> 收稿日期: 2009 - 02 - 25; 修改日期: 2009 - 03 - 23

<sup>\*</sup> 基金项目: 国家九五大科学工程冷却储存环项目(06HIRFL200) 作者简介: 赵龙(1983-),男(汉族),甘肃庆阳人,硕士研究生,从事计算机系统结构及自动控制研究。

<sup>#</sup> 通讯联系人: 乔卫民, E-mail: qwm@impcas. ac. cn

总线;某些子系统采用 CANBus 作为现场总线。上海光源(Shanghai Synchrotron Radiation Facility,简称 SSRF)的控制系统[7]结构采用了分层式分布处理系统结构,它的控制系统基于 EPICS 系统设计,操作接口层提供上层编程环境支持、数据库支持、共享文件和网络管理等,由一系列的工作站和PC 机等组成。以上各家的加速器控制系统所采用的控制板卡,基本都是商业采购,缺乏对整个控制系统总体实现细节上的认识,工程费用较高。

鉴于 CSR 大量的被控设备分布在主环、实验环、RIB 分离器和束运线上<sup>[8]</sup>, CSR 控制系统采用了基于网络架构的大型分布式系统,此控制系统是基于高档微机、工作站、服务器的智能化、开放型、全分布式和系统造价低的控制系统,由总体控制和前端控制两部分构成。总体控制包括网络通信支持系统、集群服务系统和数据库系统;前端控制器用来提供对受控目标和装置的完全控制,它们可接收命令和数据、运行算法、向设备送出控制信号、返回设备的状态和数据,并提供人机界面等。前端控制器具有多种灵活的接口,通过网络接口将前端智能控制器和控制系统核心数据库相连接;以及将加速器运行所需的数据和参数下载至前端智能控制器,并将加速器运行的状态返回至核心数据库。前端控制器是 HIRFL-CSR 控制系统的关键部件。

# 2 HIRFL-CSR EVME 总线控制器的 硬件系统

### 2.1 HIRFL-CSR EVME 总线控制器的硬件原理

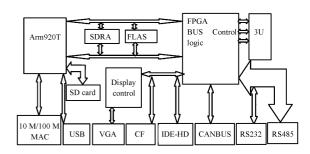

EVME 总线是以性能价格比及可靠性均较高的 VME 总线技术为基础,充分兼容目前电子技术的最新发展,定义的 HIRFL-CSR 前端控制总线规范。前端总线控制器用来提供对受控目标和装置的完全控制。HIRFL-CSR EVME 总线控制器 FBC-01 是标准的 3U 高的插件,其功能模块和原理框图如图 1 所示。

ARM 处理器主要功能是传输控制;下载波形数据,采集存储电源状态;利用控制器上的 Flash空间,存储需永久保存或反复使用的波形数据,尽量减少与上层数据库的数据交换;还可驱动 VME

总线控制器,通过 HPI 接口来管理访问和分配 DSP 的存储空间。FPGA 模块主要为 EVME 总线提供时序。

图 1 HIRFL-CSR EVME 总线控制器框图<sup>[9]</sup>

### 2.2 Arm9 处理器的改进

HIRFL-CSR EVME 总线控制器的核心是 AT-MEL 公司推出的 AT91RM9200 处理器。该处理器集成了相当多的系统外设,如 USB host 接口、LCD 控制器、IDE 控制器、PCMCIA 控制器、串口、音频接口、10/100 Mbps 网络 MAC、SDRAM控制器等。处理器具有一个高速片内 SRAM 工作空间和低延迟的外部总线接口(EBI),可以与用户需要的多种构型的片外存储器及存储器定位的外设进行无缝连接。EBI 集成了同步动态随机存储器(SDRAM)控制器、FLASH 和静态存储器控制器,以及用于与 NAND Flash,Smart Media 及 CF 卡接口的专门电路。

另外,处理器集成了包括 JTAG-ICE、UART DEBUG 通道、嵌入式实时跟踪等调试工具。使得所有的应用程序的开发和调试,特别是实时性强的应用程序的开发更为方便。

### 2.3 FPGA 现场可编程器件

HIRFL-CSR EVME 总线控制器采用现场可编程器件 ACEX 1 K30 实现所有的 HIRFL-CSR EVME 总线控制逻辑和外部设备控制逻辑。这在 HIRFL-CSR 控制系统中是非常重要的,它可以针对控制系统中被控设备的多样性、信号连接的复杂性,在现场随时改变接口的信号定义,大大方便了 HIRFL-CSR 控制系统与各种智能控制器通信。这个特点也为控制器的通用性打下了良好的基础。使用 VHDL 语言编写的硬件接口控制逻辑代码,可以方便地随时更换,使得整个 HIRFL-CSR 控制系统的硬件系统平台具有非常强大的包容性。基于

DSP 技术和 MCU 技术的各种智能控制器能够很容易地运行在一个通用的平台上,执行各自不同的控制任务。它们通过 HIRFL-CSR EVME 总线背板交换数据, HIRFL-CSR EVME 总线控制器通过 Intranet 和数据中心及中央控制室用户界面交换信息,从而实现分布式控制系统的功能。

### 2.4 系统的存储设备

系统的操作系统、系统参数、环境变量存放在 SDRAM 和 FLASH 里,可以附带 IDE 硬盘和其他 移动存储设备,如 SD 卡和 CF 卡等,大大增强了系 统的实用性和灵活性。另外,这些功能被 Linux 操 作系统很好地支持。

## 3 HIRFL-CSR EVME 总线控制器软件系统的改进

### 3.1 嵌入式操作系统

HIRFL-CSR EVME 总线控制器运行 ARM-Linux 嵌入式操作系统,它遵循 GPL 协议,源码全部公开并且免费,稍加修改后便可应用于本系统。此外,还有大量遵从 GPL 协议并开源的优秀开发工具,通过它们可以大大降低软件的开发和维护成本。其优秀的网络功能和 Linux 本身具备的稳定性、可靠性和运行所需资源少等特点都是十分适合当前环境下的嵌入式应用。

### 3.2 操作系统的改进设计

作为一款优秀的嵌入式操作系统,ARM-Linux 可以运行于多种平台上,它的内核可裁减,根据系统的不同,用户可以定制适合自己所需的内核。控制器运行 Linux 2.6 的内核,通过定制,它支持多种网络协议(如 IPv4 和 IPv6);提供 NFS 网络文件系统支持,配合 NFSD 服务,可方便地同上层数据库交换数据;支持 USB2.0 协议,通过挂载,可读写 U盘,支持 USB接口的键盘和鼠标支持热插拔;通过修改显示芯片的驱动程序,可支持图形显示,可接显示器。

#### 3.3 应用程序的改进设计

ARM-Linux 嵌入式操作系统的启动有两种方式:一是通过 tftp 协议,通过 tftp 的服务和网络将内核和 Ram disk 下载到 ARM 的内存空间解压缩自启动,这种方式适合于研发阶段,方便快捷;二

是研发完成后,将最后修改的内核和 ram disk 通过 网络下载到 ARM 内存中,烧写到 Flash 中,以后 每次启动系统将自动从 Flash 获取内核和 ram disk,在解压缩后便可自动运行。

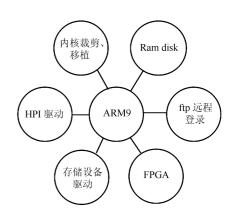

在智能嵌入式控制器上实现的各种驱动和应用 程序如图 2 所示。

图 2 嵌入式系统驱动和应用程序开发图

Ram disk 是用作一个硬盘分区的部分内存空间,大多数嵌入式系统都是没有硬盘等存储设备的,所以将制作好的 Ram disk 根文件系统存储在Flash中,并在Flash中开辟专门的存储空间,可在系统启动后保存少量的数据。

在改进控制器的软件系统时,主要重新设计了系统的内核和应用程序,内核使用了新裁剪的 2.6 版本,2.6 的内核可以更好地控制和管理设备,新调度器基于每个 CPU 来分布时间片,消除了全局同步和重新分配循环,从而提高了性能。此内核版本的扩展性更强,支持更多的设备。应用程序的优化包括从数据库获取波形数据,传输波形数据到DSP中去,然后返回波形数据到数据库,增加了数据反馈,提高了控制器的稳定性和可维护性。

## 4 结论

HIRFL-CSR EVME 总线控制器已经运行在 HIRFL-CSR 的前端控制系统中,除了进行本地控 制外,还作为网关,起着连接智能控制器到中央控 制系统的桥梁作用。目前经过改进已经完成了通用 并行总线设备驱动程序的编程,并和在此平台上开 发的其它智能模块,如基于 DSP 的电源控制模块 和高频控制模块等配套使用,用于 CSR 主环及实 验环的控制系统。经过将近一年的现场应用,证明 改进后的系统功能更加完善,工作可靠性更强,更加方便于现场测试和使用。控制器的软件和硬件采用了 ARM 和 LINUX 等嵌入式主流技术,减少了开发成本,并且具有很好的应用价值。

### 参考文献(References).

- [1] Sidorowicz K V, Leibfritz D, McDowell W P. The APS Control System Network Upgrade. International Conference on Accelerator and Large Experimental Physics Control Systems, Trieste (Italy): Argonne National Laboratory, 1999.

- [2] Akiymama A, Araki S, Katoh T, et al. KEBE Control System. Proceedings of the 1999 Particle Accelerator Conference, New York (USA): American Physical Society, 1999.

- [3] Krause U, Schaa V R W. Particle Accelerator Physics, 2001, 345.

- [4] Zhao J, Wang C H, Zhan M C, et al. Upgrade of Control System for the BEPCII. International Conference on Computing in

- High Energy and Nuclear Physics, Beijing(China): Institute of High Energy Physic, 2001, 1: 117—120.

- [5] Garrett R, Howry S, Wermelskirchen C, et al. A Control System Upgrade of the Spear Synchrotron and Injector. International Conference on Accelerator and Large Experimental Physics Control System, Stanford (USA): Stanford Synchrotron Radiation Laboratory, 1995.

- [6] Liu Gongfa, Li Weimin, Jingyi, et al. Nuclear Science and Techniques, 2005, 31(2): 82.

- [7] Mi Qingru, Zheng Lifang, Liu Songqiang. Nuclear Techniques, 2008, **31**(1): 1.

(米清茹,郑丽芳,刘松强. 核技术, 2008, **31**(1): 1.)

- [8] Xia Jiawen, Zhan Wenlong, Wei Baowen, et al. Nuclear Physics Review, 2001, **18**(1): 35(in Chinese). (夏佳文, 詹文龙, 魏宝文等. 原子核物理评论, 2001, **18**(1): 35.)

- [9] Jing Lan, Qiao Weimin, Xu Yang, et al. Nuclear Techniques, 2006, 29(10): 792(in Chinese).(敬岚,乔卫民,徐杨等. 核技术,2006,29(10): 792.)

## Improved Design of HIRFL-CSR EVME Bus Controller\*

ZHAO Long<sup>1, 2</sup>, QIAO Wei-min<sup>1, #</sup>, JING Lan<sup>1</sup>, LIU Wu-feng<sup>1, 2</sup>

(1 Institute of Modern Physics, Chinese Academy of Sciences, Lanzhou 730000, China;

2 Graduate School of Chinese Academy of Sciences, Beijing 100049, China)

**Abstract:** The EVME bus controller which is a key component of the HIRFL-CSR control system was improved. Besides reconfiguring the embedded Linux, a utility program was developed for data exchange between the controller and the database. The bus controller is based on ARM920T(ARM9) micro processor which is BGA packaged. The bus controller has the universal interface of VGA display, keyboard, and mouse. The backboard interface logic is programmed in an in-system configurable FPGA device. The bus can drive high current up to 64 mA, with the flexibility of the programmable signal definitions. All the improved performance helped the EVME bus controller play a crucial role in HIRFL-CSR control system.

Key words: ARM9; bus controller; universal computer peripheral interface; embedded Linux

<sup>\*</sup> Received date: 25 Feb. 2009; Revised date: 23 Mar. 2009

<sup>\*</sup> Foundation item: Cooling Storage Ring of National Key Science Engineering Project(06HIRFL200)

<sup>#</sup> Corresponding author: Qiao Wei-min, E-mail: qwm@impcas. ac. cn